数字设计 FPGA 应用,第三章组合逻辑设计和 VIVADO 进阶,课程设计性质的作业题2

第二题:再建一个工程,调用该 IP 核实现 4 输入逻辑函数f=∑wxyz(1,3,6,7,11,13,14)。对该工程进行仿真测试(必须)

使用软件: Vivado

开发板: EGO1采用Xilinx Artix-7系列XC7A35T-1CSG324C FPGA

第一题及生成的IP核见链接:

第一题:实现8选1的数据选择器74HC151

问题分析

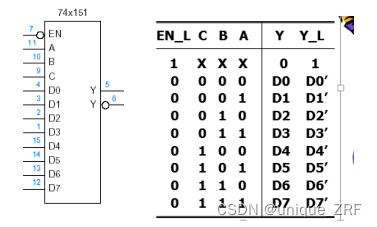

74HC151及其功能表如下图所示:

- 当EN_L=0时,74HC151的输出逻辑表达式可以写为:

Y=(C’B’A’) · D0+(C’B’A)· D1+(C’BA’)· D2+(C’BA)· D3+(CB’A’)· D4+(CB’A)· D5+(CBA’)· D6+(CBA)· D7 - 将给定的逻辑函数 f=∑wxyz(1,3,6,7,11,13,14)写为:

f=w’x’y’z+w’x’yz+w’xyz’+w’xyz+wx’yz+wxy’z+wxyz’

3.逻辑函数式对应1中的逻辑表达式写成如下格式:

f=(w’x’y’)· z+(w’x’y)· z+(w’xy’)· 0+(w’xy)· (z+z’)+(wx’y’)· 0+(wx’y)· z+(wxy’)· z+(wxy1)· z’

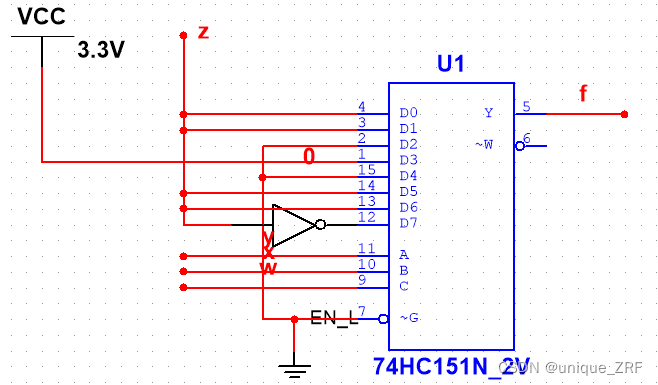

Y与f式相对应即可得出74HC151的输入:

令 C=w、B=x、A=y、D0=z、D1=z、D2=0、D3=1、D4=0、D5=z、D6=z、D7=z’

如下图所示:

代码实现

- Verilog代码

`timescale 1ns / 1ps

//

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?