使用软件: Vivado

开发板: EGO1采用Xilinx Artix-7系列XC7A35T-1CSG324C FPGA

BRAM笔记

BRAM介绍

BRAM 即块 RAM, 是 FPGA 的固有硬件资源。 另一种形式的 RAM 是分布RAM(Distribution RAM), 是由 FPGA 逻辑资源查找表 LUT 拼起来的 。这两种 RAM 最本质的区别是块RAM 默认输入有寄存器,所以它在读、写使能信号后的下个时钟边沿返回数据,而分布式RAM就没有,就是个组合逻辑,读、写使能的同一时刻返回数据。从时序的角度上来说,块RAM更好,唯一不足的是,它是珍贵的硬件资源。一般来说,芯片越高级,块RAM资源越多。

Artix- - 7 FPGA 的最高型号具有可分配的 13Mbit双端口BRAM, 而实验电路板选型的XC7A35T具备 18Kbit 的BRAM100 个 ,36Kbit 的BRAM 50 个,共1800Kbit 。 Xilinx 7系列 FPGA 可将 BRAM 配置为同步双端口 RAM或单端口 RAM。

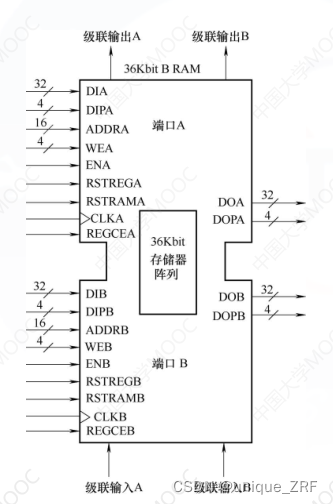

同步双端口BRAM

方便通过一个端口写的同时可以从另一个端口进行读取

每个真正的双端口的36Kbit BRAM 包含 36Kbit 个存储单元以及2个完全独立的访问接口A 和B 。每个 18Kbit BRAM 双端口内存包含18Kbit 个存储单元以及2个完全独立的访问接口A和B 。内存的结构完全对称, 双端口可互换。

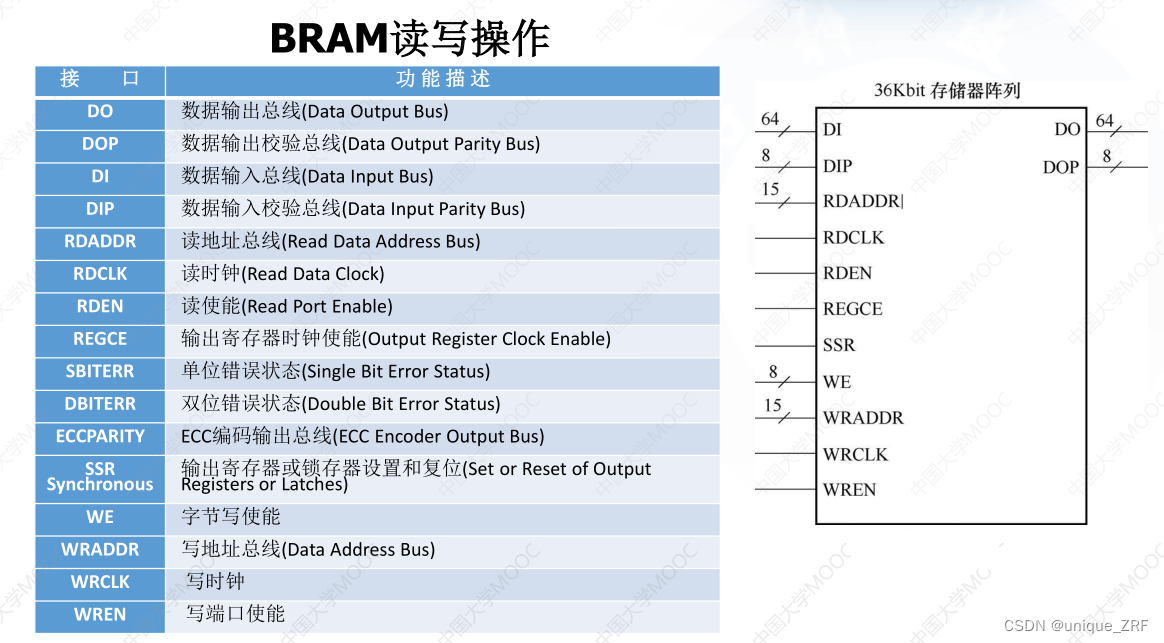

BRAM读写操作

(1)读操作

读操作是在一个时钟边沿完成读取RAM指定单元(读地址)内容的操作。首先将读取地址寄存在读端口,并在RAM读取时间之后将存储的数据加载到输出锁存器中。当使用输出寄存器时,读操作需要一个额外的等待周期。

(2)写操作

写操作是一个时钟边沿写入RAM的操作。写地址寄存在写入端口,数据输入存储在内存中。

(3)写模式

写模式有三种,决定了写入时钟边沿后,有效数据出现在输出锁存器的时间。

三种模式是: 写优先模式WRITE_FIRST、读优先模式READ_FIRST和不变模式。每个端口的写模式可以通过配置过程单独配置。

默认模式是写优先模式,在这种模式总是将最新写入的数据送到输出总线上。

在读优先模式,当新的数据被写入时,仍然输出先前存储的数据。

在不变模式,输出总线上保持先前的输出。

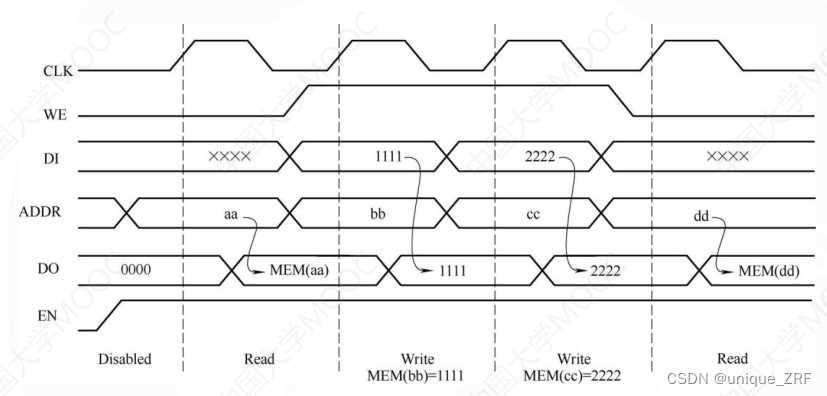

写优先模式

在第一个时钟的上升沿,将地址aa的数据MEM(aa)读出放在数据总线DO上。在第二个时钟的上升沿,写有效,因此将DI上的1111写入地址bb。因为写优先,所以出现在数据总线上的是新写入的1111。

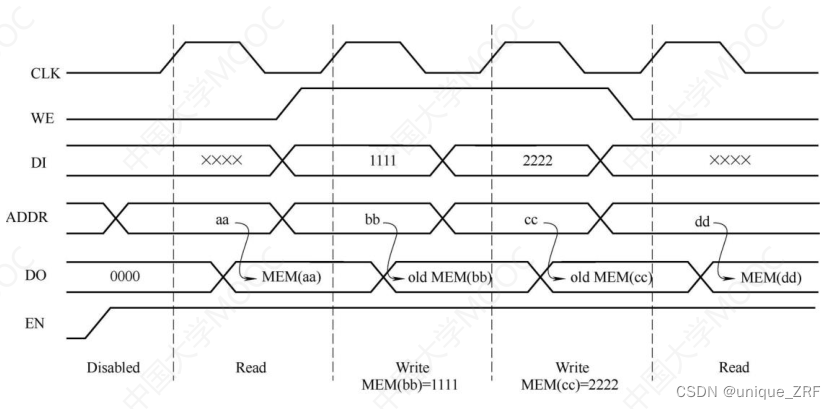

读优先模式

在第一个时钟的上升沿,将地址aa的数据MEM(aa)读出放在数据总线DO上。在第二

个时钟的上升沿,写有效,因此将DI上的1111写入地址bb。因为读优先,所以出现在数据总线上的不是新写入的1111,而是原来地址bb的内存的值old MEM(bb)。

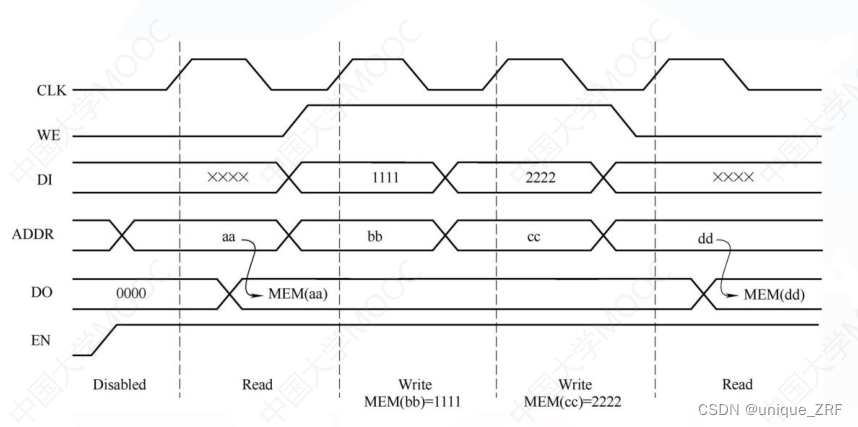

不变模式

在第一个时钟的上升沿,将地址aa的数据MEM(aa)读出放在数据总线DO上。在第二个时钟的上升沿,写有效,因此将DI上的1111写入地址bb。因为不变模式,所以在写有效的时候出现在数据总线上的数据是不变的,仍然是MEM(aa),直到写无效后的第一个时钟上升沿才变为MEM(dd)。

双端口块内存接口

本文详细介绍了Xilinx Artix-7 FPGA中的块RAM(BRAM)资源,包括其与分布式RAM的区别、同步双端口BRAM的特点以及读写操作。同时,讲解了BRAM的三种写模式:写优先、读优先和不变模式,并提供了BRAM IP核的使用步骤、coe文件的生成以及Verilog代码实现和仿真验证。通过对BRAM的深入理解,有助于更好地利用FPGA的内存资源进行设计。

本文详细介绍了Xilinx Artix-7 FPGA中的块RAM(BRAM)资源,包括其与分布式RAM的区别、同步双端口BRAM的特点以及读写操作。同时,讲解了BRAM的三种写模式:写优先、读优先和不变模式,并提供了BRAM IP核的使用步骤、coe文件的生成以及Verilog代码实现和仿真验证。通过对BRAM的深入理解,有助于更好地利用FPGA的内存资源进行设计。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?