硬件描述语言实验十一:数码管数字序列显示实验

本篇博客用来记录一下本周一的硬件实验(非常非常值得纪念!—”慈祥“的硬件老师)

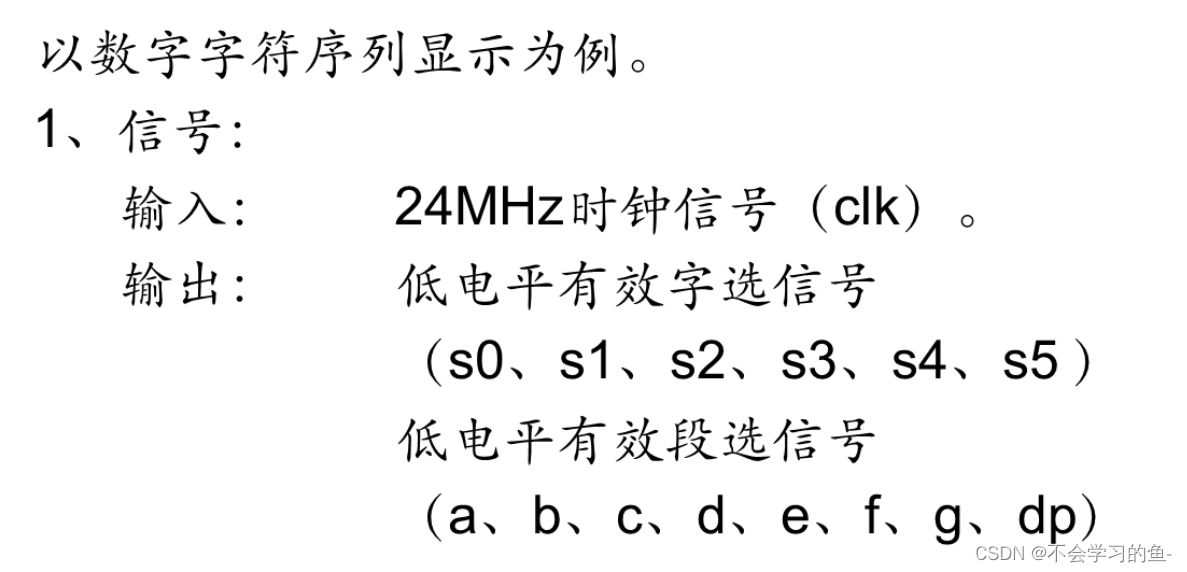

实验要求:

在HDLE-1硬件描述语言综合实验平台上,用六位数码管显示学生本人的学号。最低要求:至少同时显示出学号的后六位;终极目标:滚动显示全部学号。

实验思路提示:

设计数字系统,应该应用系统的思考方法。一个较复杂的功能电路,首先将系统分割成多个功能相对简单、独立的模块,清晰准确的定义个模块的功能以及模块之间的接口;模块还可以进一步分割,使系统为一个具有多层次、多模块的整体。

实验思路:

参考老师上课给出的硬件结构思维图 辅助理解代码

实验代码:

xh6.vhd文件

直接”拿来主义“

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity xh6 is

port(

clk:in std_logic;

s:out std_logic_vector(5 downto 0);//字选

q:out std_logic_vector(6 downto 0));//段选

end xh6;

architecture rtl of xh6 is

signal clk1:std_logic;

signal cnt1:integer range 0 to 5;//计数

signal count1:integer range 0 to 49999;//分频

begin

process(clk)

begin

if clk'event and clk = '1' then

if count1 = 49999 then

clk1 <= '1';

count1 <= 0;

else

count1 <= count1+1;

clk1 <= '0';

end if;

end if;

end process;

process(clk1)

begin

if clk1'event and clk1 = '1' then

if cnt1 = 5 then cnt1 <= 0;

else

cnt1 <= cnt1+1;

end if;

end if;

end process;

process(cnt1)

begin//多路选择器+解码器

case cnt1 is

when 0 => q <= "xxxxxxx";s <="011111";//xxxxxxx填自己学号后六位对应的数码管编号

when 1 => q <= "xxxxxxx";s <="101111";

when 2 => q <= "xxxxxxx";s <="110111";

when 3 => q <= "xxxxxxx";s <="111011";

when 4 => q <= "xxxxxxx";s <="111101";

when 5 => q <= "xxxxxxx";s <="111110";

when others => null;

end case;

end process;

end rtl;

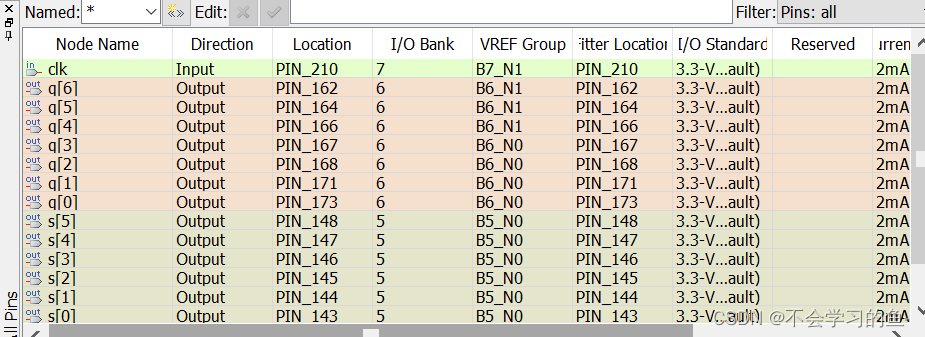

引脚位置配置:

注意数码管段选和字选接口顺序不要反了!

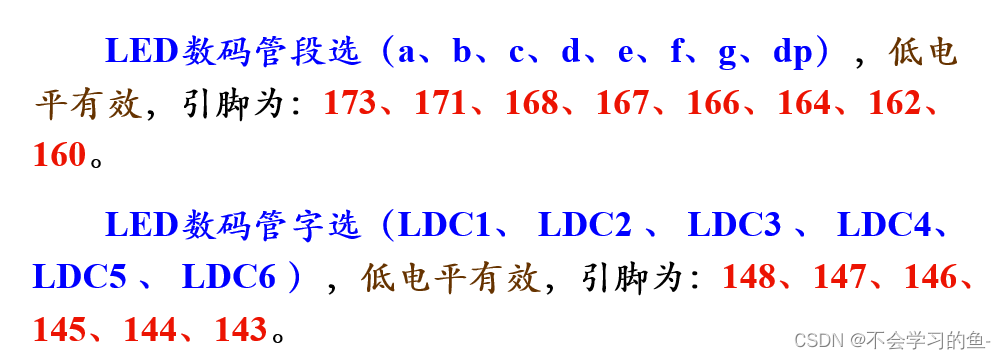

最后附上数码管引脚位置说明:

本次实验课教训是不能做太着急,要先独立思考。

1657

1657

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?