使用 FPGA 开发板上的 6 位数码管以动态方式从 0 开始计数,每 100ms 计数值增加一, 当计数值从 0 增加到 999999 后重新从 0 开始计数。

Library IEEE;

Use IEEE.std_logic_1164.ALL;

use ieee.std_logic_signed.all;

ENTITY shuma IS

port(

sys_clk : in std_logic;--50MHz

SG : out std_logic_vector(7 downto 0);--段控制信号输出

BT : out std_logic_vector(5 downto 0) --位控制信号输出

);

END shuma;

ARCHITECTURE behav OF shuma IS

signal LED1,LED2,LED3,LED4,LED5,LED6:std_logic_vector(7 DOWNTO 0);

signal scan_LED:integer range 0 to 5;--扫描数码管的个数

signal clk1:std_logic;

signal clk2:std_logic;

signal cnt1,cnt2,cnt3,cnt4,cnt5,cnt6:integer range 0 to 9 :=0;--由低位到高位(个~十万)

BEGIN

--100ms时钟模块

Module_1Hz : PROCESS(sys_clk)--时钟分频--100ms

variable num1:integer range 1 to 2500000;

BEGIN

if rising_edge(sys_clk)then

if num1 = 2500000

then num1:= 1;clk1<= not clk1;

else num1:= num1+1;

END if;

END if;

END PROCESS module_1Hz;

--1000Hz扫描模块

Module_200Hz : PROCESS(sys_clk)--时钟分频--1000Hz

variable num2:integer range 1 to 25000;

BEGIN

if rising_edge(sys_clk)then

if num2 = 25000

then num2 := 1;clk2<= not clk2;

else num2 := num2+1;

END if;

END if;

if rising_edge(clk2)then

if(scan_LED=5)then

scan_LED<=0;

else

scan_LED<=scan_LED+1;

end if;

end if;

END PROCESS Module_200Hz;

--1s计数模块,6个数码管累加显示数字,范围000000-999999

Module_cnt : process(clk1)

begin

if rising_edge(clk1)then

if(cnt1=9)then

if(cnt2=9)then

if(cnt3=9)then

if(cnt4=9)then

if(cnt5=9)then

if(cnt6=9)then

cnt6<=0;

cnt5<=0;

cnt4<=0;

cnt3<=0;

cnt2<=0;

cnt1<=0;

else

cnt6<=cnt6+1;

cnt5<=0;

cnt4<=0;

cnt3<=0;

cnt2<=0;

cnt1<=0;

end if;

else

cnt5<=cnt5+1;

cnt4<=0;

cnt3<=0;

cnt2<=0;

cnt1<=0;

end if;

else

cnt4<=cnt4+1;

cnt3<=0;

cnt2<=0;

cnt1<=0;

end if;

else

cnt3<=cnt3+1;

cnt2<=0;

cnt1<=0;

end if;

else

cnt2<=cnt2+1;

cnt1<=0;

end if;

else

cnt1<=cnt1+1;

end if;

end if;

end process Module_cnt;

--译码电路,数码管动态字符查表

Module_Decoding : process(cnt1,cnt2,cnt3,cnt4,cnt5,cnt6)

begin

case cnt1 is

when 0 => LED1 <= "11000000";--数字0

when 1 => LED1 <= "11111001";--数字1

when 2 => LED1 <= "10100100";--数字2

when 3 => LED1 <= "10110000";--数字3

when 4 => LED1 <= "10011001";--数字4

when 5 => LED1 <= "10010010";--数字5

when 6 => LED1 <= "10000010";--数字6

when 7 => LED1 <= "11011000";--数字7

when 8 => LED1 <= "10000000";--数字8

when 9 => LED1 <= "10010000";--数字9

when others => Null;

end case;

case cnt2 is

when 0 => LED2 <= "11000000";--数字0

when 1 => LED2 <= "11111001";--数字1

when 2 => LED2 <= "10100100";--数字2

when 3 => LED2 <= "10110000";--数字3

when 4 => LED2 <= "10011001";--数字4

when 5 => LED2 <= "10010010";--数字5

when 6 => LED2 <= "10000010";--数字6

when 7 => LED2 <= "11011000";--数字7

when 8 => LED2 <= "10000000";--数字8

when 9 => LED2 <= "10010000";--数字9

when others => Null;

end case;

case cnt3 is

when 0 => LED3 <= "11000000";--数字0

when 1 => LED3 <= "11111001";--数字1

when 2 => LED3 <= "10100100";--数字2

when 3 => LED3 <= "10110000";--数字3

when 4 => LED3 <= "10011001";--数字4

when 5 => LED3 <= "10010010";--数字5

when 6 => LED3 <= "10000010";--数字6

when 7 => LED3 <= "11011000";--数字7

when 8 => LED3 <= "10000000";--数字8

when 9 => LED3 <= "10010000";--数字9

when others => Null;

end case;

case cnt4 is

when 0 => LED4 <= "11000000";--数字0

when 1 => LED4 <= "11111001";--数字1

when 2 => LED4 <= "10100100";--数字2

when 3 => LED4 <= "10110000";--数字3

when 4 => LED4 <= "10011001";--数字4

when 5 => LED4 <= "10010010";--数字5

when 6 => LED4 <= "10000010";--数字6

when 7 => LED4 <= "11011000";--数字7

when 8 => LED4 <= "10000000";--数字8

when 9 => LED4 <= "10010000";--数字9

when others => Null;

end case;

case cnt5 is

when 0 => LED5 <= "11000000";--数字0

when 1 => LED5 <= "11111001";--数字1

when 2 => LED5 <= "10100100";--数字2

when 3 => LED5 <= "10110000";--数字3

when 4 => LED5 <= "10011001";--数字4

when 5 => LED5 <= "10010010";--数字5

when 6 => LED5 <= "10000010";--数字6

when 7 => LED5 <= "11011000";--数字7

when 8 => LED5 <= "10000000";--数字8

when 9 => LED5 <= "10010000";--数字9

when others => Null;

end case;

case cnt6 is

when 0 => LED6 <= "11000000";--数字0

when 1 => LED6 <= "11111001";--数字1

when 2 => LED6 <= "10100100";--数字2

when 3 => LED6 <= "10110000";--数字3

when 4 => LED6 <= "10011001";--数字4

when 5 => LED6 <= "10010010";--数字5

when 6 => LED6 <= "10000010";--数字6

when 7 => LED6 <= "11011000";--数字7

when 8 => LED6 <= "10000000";--数字8

when 9 => LED6 <= "10010000";--数字9

when others => Null;

end case;

end process Module_Decoding;

--刷新显示模块

Module_SG : process(scan_LED)

begin

case scan_LED is

when 0 => SG <= LED1;BT <= "111110";--数码管1

when 1 => SG <= LED2;BT <= "111101";--数码管2

when 2 => SG <= LED3;BT <= "111011";--数码管3

when 3 => SG <= LED4;BT <= "110111";--数码管4

when 4 => SG <= LED5;BT <= "101111";--数码管5

when 5 => SG <= LED6;BT <= "011111";--数码管6

when others => Null;

end case;

end process Module_SG;

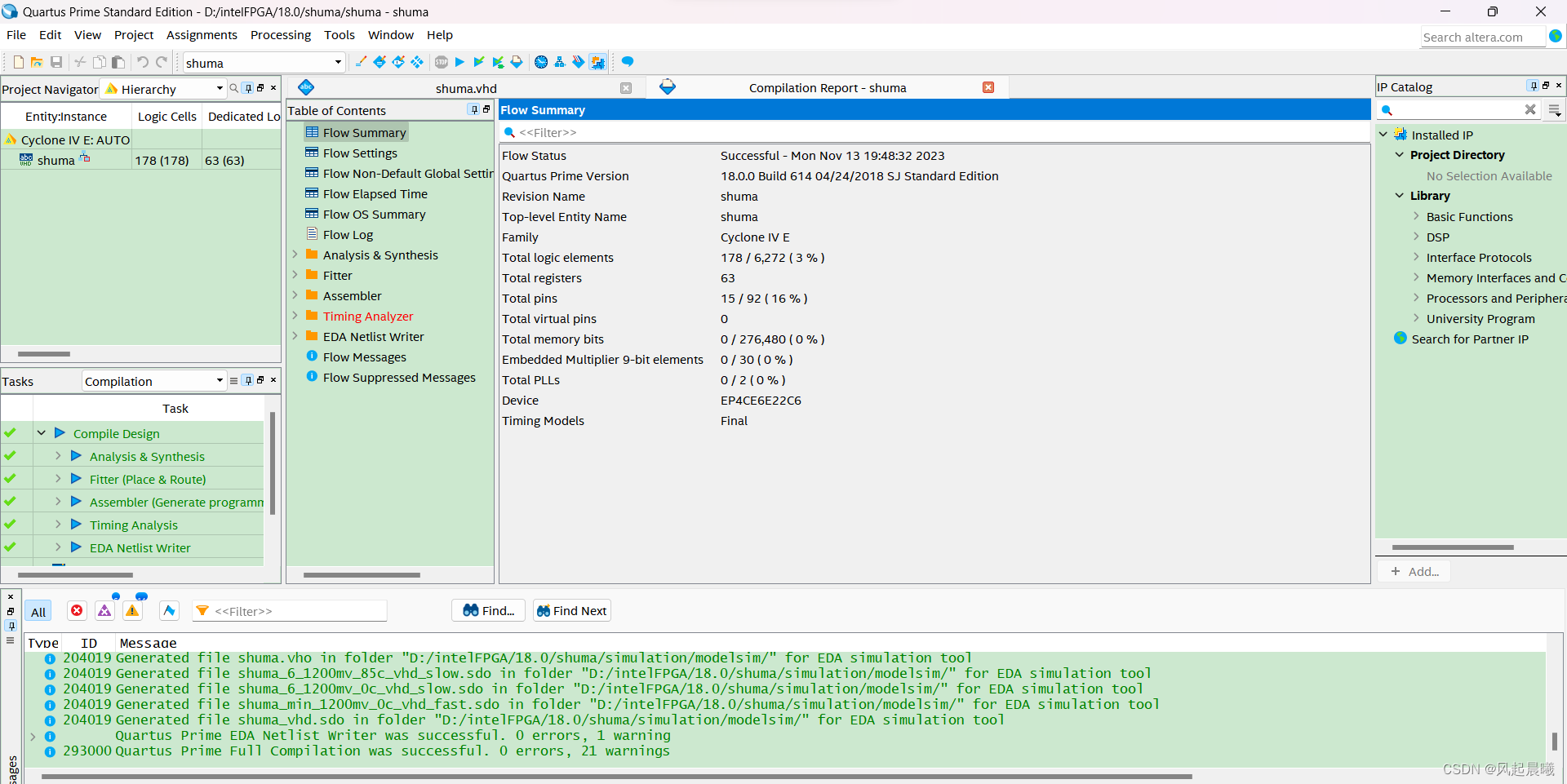

end behav;编译结果:

1961

1961

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?