因最近客户需求,用纯PL实现AD9361的数字信号调制解调,于是就把各种数字调制都在AD9361上都实现了一遍。

优点就是:既可以在zynq系列上配置9361,也可以在纯FPGA系列配置9361。并且理解起来比较简单!!!

制作不易,记得三连哦,给我动力,持续更新中!!!

完整工程文件下载:纯逻辑设计AD9361发射FM工程下载 (点击蓝色文字即可下载)

提取码:19w5

对于之前学习过我文章的小伙伴来说,大家应该都了解如何利用 AD936x Evaluation Software 生成 AD9361 的配置,并在 Vivado 中调用该配置,最后写入 AD9361 芯片。

对于新来的小伙伴而言,我建议你可以先回顾一下我之前的文章内容。在那些文章中,我详细介绍了如何通过软件生成 AD9361 的配置,并在 Vivado 开发环境中使用该配置。这些基础知识对于接下来的内容学习很重要。

在接下来的设计中,我们将在纯逻辑配置 AD9361 的基础上,实现各种数字信号的调制解调功能。这将涉及更多的数字信号处理知识和技术。如果你对这些内容感兴趣,不妨继续关注我的后续文章。我会在这些文章中, 全面地讲解如何基于 AD9361 实现各种数字调制解调功能的具体实现方法。

本篇文章将介绍如何通过AD9361发射FM信号以及纯verilog代码实现和讲解。

一、FM原理

基于 FPGA 和 AD9361 实现 FM 数字调制与解调的原理如下:

-

FM 数字调制:

- 利用 FPGA 逻辑电路生成正弦波载波信号。

- 根据输入的数字信号,动态调整载波信号的频率。这就实现了FM调制。

- 将调制后的信号输入到 AD9361 的 TX 端,进行模拟上变频和放大.

-

FM 数字解调:

- AD9361 的 RX 端接收 FM 调制信号,完成下变频和数字化。

- FPGA 接收 AD9361 输出的数字 FM 信号,采用频率判决或相位锁定环等方式实现FM解调。

- 从解调后的数字信号中提取出原始的输入数据。

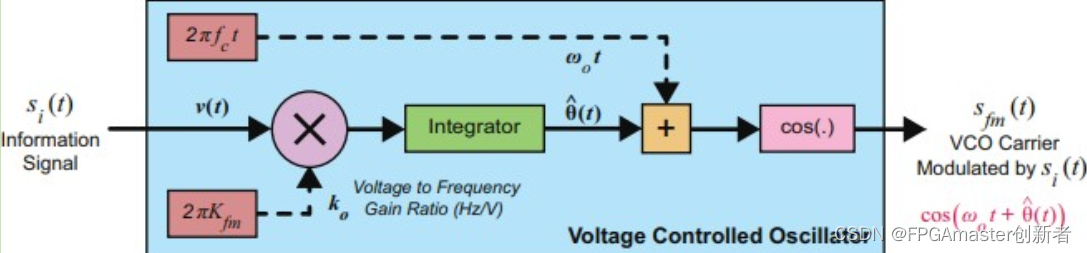

FM 就是频率调制,就是使用载波的频率来承载消息信号,当消息信号的幅值较大的时候,产生的频率比较大,当消息信号较小时,产生的频率比较小。在我们之前介绍过的 VCO 这个结构,就是一个最简单的 FM 的调制器。

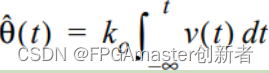

控制信号进入了 VCO 之后,首先需要乘上一个增益,这个增益表示电压(消息信号的幅值) 到频率(FM 调制的结果) 的增益值, 𝑣𝑣(t)与𝑘𝑘𝑜𝑜的乘积会经过一个积分器。积分之后的信号为:

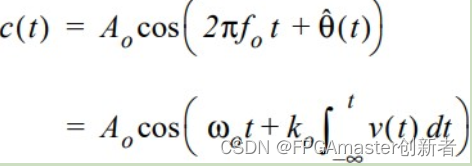

由 VCO 产生的正弦波会有一个初始的振幅𝐴𝐴0和频率𝑓𝑓0,正弦波的相位取决于前面这个积分信号的瞬时值。将这个值带入到产生的正弦波当中。

其中这个𝑘𝑘𝑜𝑜可以表示为𝑘𝑘𝑜𝑜 = 2𝜋𝜋𝜋𝜋𝑓𝑓𝑎𝑎,因此 VCO 得到的输出信号为:

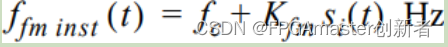

VCO 输出信号的频率就是对相位的微分,可以表示为:

可以看到使用 FM 调频之后,已调信号将会包含很多的频率分量。

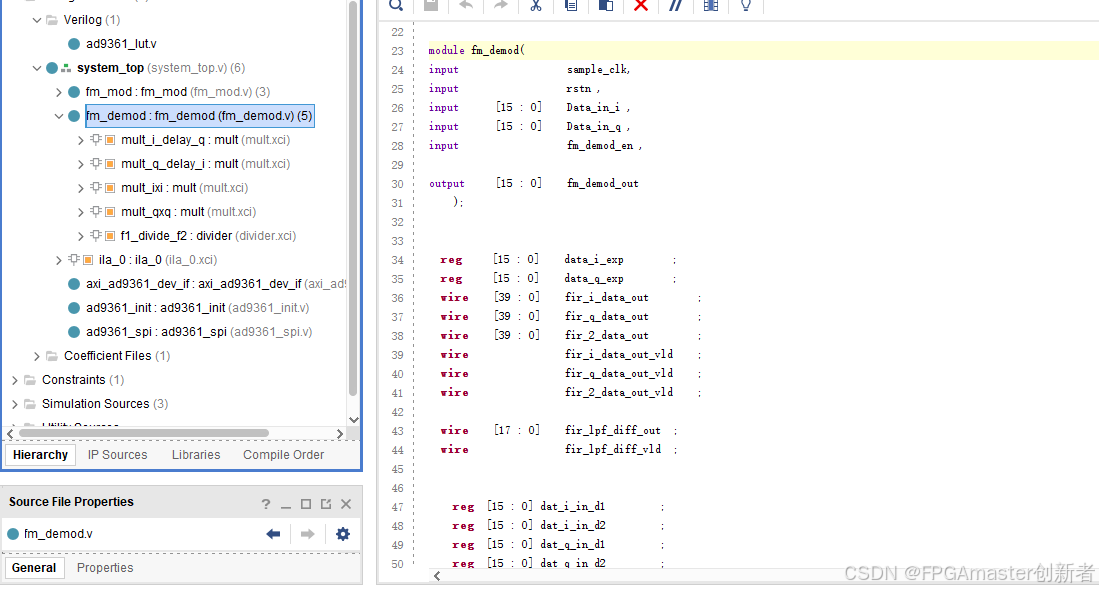

二、FPGA工程代码

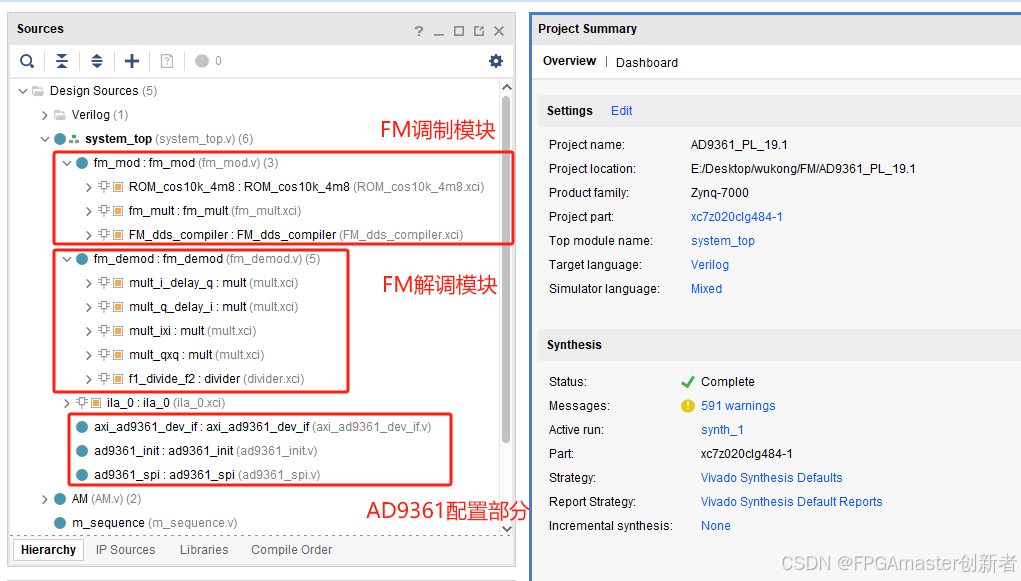

主要代码为:FM调制模块、FM解调模块、9361数据接收和发射接口、9361配置模块,和之前的ASK调制的差异主要是把ASK调制部分替换为了FM调制和解调,其他代码不变(一劳永逸)

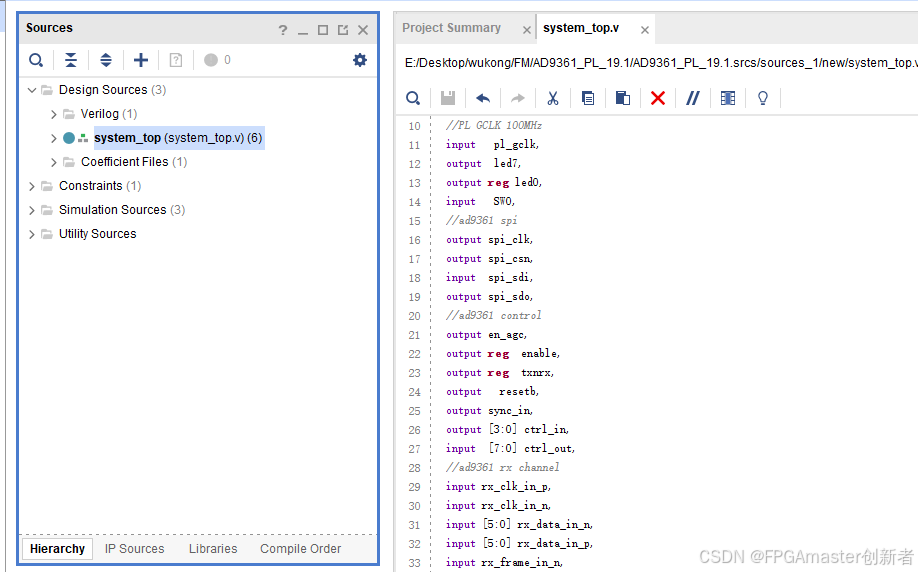

(1)顶层top

主要连接各个模块,已结对差分信号的差分转换

部分代码:

wire [11:0] fm_source_data;

fm_mod (

.sample_clk ( sample_clk ),

.rstn ( initial_rstn ),

.source_data ( fm_source_data ),

.date_i ( dac_data_i1 ),

.date_q ( dac_data_q1 )

);

fm_demod fm_demod(

.sample_clk(sample_clk),

.rstn( initial_rstn ),

.fm_demod_en( initial_rstn ),

.Data_in_i({adc_data_i1[11],adc_data_i1[11],adc_data_i1[11],adc_data_i1[11],adc_data_i1}),

.Data_in_q({adc_data_q1[11],adc_data_q1[11],adc_data_q1[11],adc_data_q1[11],adc_data_q1}),

.fm_demod_out(fm_demod_out)

);

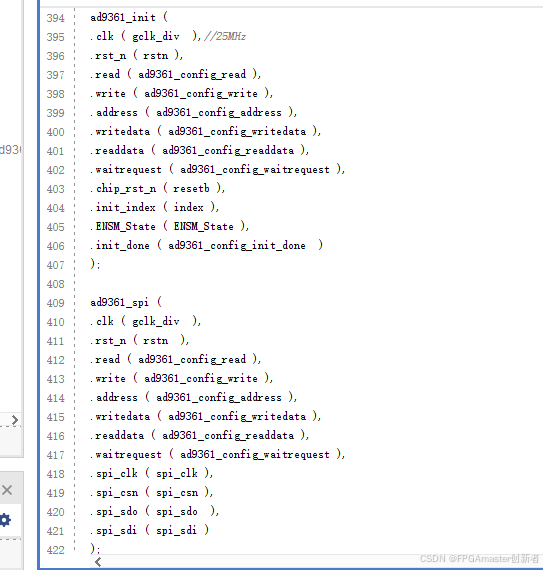

(2)配置9361模块

主要通过读取ad9361_lut.v中的配置信息,然后通过SPI去写入9361寄存器,实现对9361的配置

部分代码:

module ad9361_init(

input clk,

input rst_n,

output reg read,

output reg write,

output reg [9:0] address,

output reg [7:0] writedata,

input [7:0] readdata,

input waitrequest,

output reg chip_rst_n,

output [12:0] init_index,

output reg [3:0] ENSM_State,

output reg init_done

);

//`define MODELSIM

`define SPI_CLK_FREQ 20 //MHz

`include "ad9361_lut.v"

reg [12:0] index;

reg [2:0] state;

reg [31:0] delay_cnt;

reg [18:0] command;

assign init_index=index;

always @ (posedge clk)

command <= ad9361_lut(index);

always @ (posedge clk or negedge rst_n)

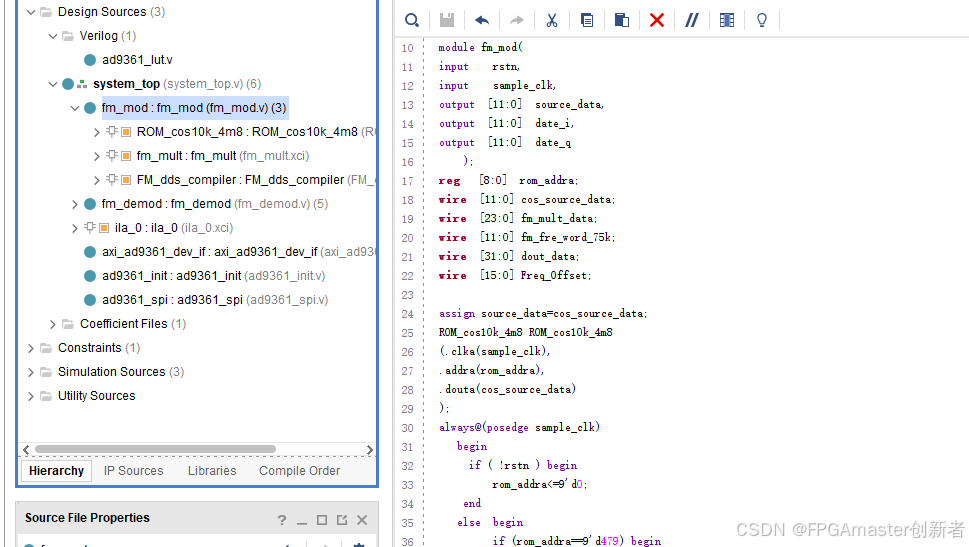

(3)FM调制模块

通过IQ调制,把FM信号,调制到IQ两个通路

部分代码:

module fm_mod(

input rstn,

input sample_clk,

output [11:0] source_data,

output [11:0] date_i,

output [11:0] date_q

);

reg [8:0] rom_addra;

wire [11:0] cos_source_data;

wire [23:0] fm_mult_data;

wire [11:0] fm_fre_word_75k;

wire [31:0] dout_data;

wire [15:0] Freq_Offset;

assign source_data=cos_source_data;

ROM_cos10k_4m8 ROM_cos10k_4m8

(.clka(sample_clk),

.addra(rom_addra),

.douta(cos_source_data)

);

always@(posedge sample_clk)

begin

if ( !rstn ) begin

rom_addra<=9'd0;

end(4)FM解调模块

把9361接收到的IQ数据,解调为数字信号输出

部分代码:

module fm_demod(

input sample_clk,

input rstn ,

input [15 : 0] Data_in_i ,

input [15 : 0] Data_in_q ,

input fm_demod_en ,

output [15 : 0] fm_demod_out

);

reg [15 : 0] data_i_exp ;

reg [15 : 0] data_q_exp ;

wire [39 : 0] fir_i_data_out ;

wire [39 : 0] fir_q_data_out ;

wire [39 : 0] fir_2_data_out ;

wire fir_i_data_out_vld ;

wire fir_q_data_out_vld ;

wire fir_2_data_out_vld ;

wire [17 : 0] fir_lpf_diff_out ;

wire fir_lpf_diff_vld ;

reg [15 : 0] dat_i_in_d1 ;

reg [15 : 0] dat_i_in_d2 ;

reg [15 : 0] dat_q_in_d1 ;

reg [15 : 0] dat_q_in_d2 ;

wire [31 : 0] p_i_delay_q ;

wire [31 : 0] p_q_delay_i ;

wire [32 : 0] p_i_delay_q_2 ;

wire [32 : 0] p_q_delay_i_2 ;

reg [32 : 0] f_1 ;

wire [31 : 0] p_i_i ;

wire [31 : 0] p_q_q ;

wire [32 : 0] p_i_i_2 ;

wire [32 : 0] p_q_q_2 ;

reg [32 : 0] f_2 ;

reg [31 : 0] div_diend ;

reg [31 : 0] div_disor ;

reg [31 : 0] f1_f2_div_diend ;

reg [31 : 0] f1_f2_div_disor ;

wire [47 : 0] f1_f2_div_out ;

wire f1_f2_div_vld ;

reg f1_f2_div_vld_d ;

wire f1_f2_div_tuser ;

wire [31: 0] div_quotient ;

wire [15: 0] div_fractional ;

reg [31: 0] div_quotient_reg ;

reg [15: 0] div_fractional_reg ;

reg [47 : 0] div_out ;

reg [15 : 0] f1_f2_div_frac_temp ;

wire [39:0] cic_data_out;

reg [15:0] cic_data_out_temp;

reg [7:0]clk_count0;

reg clk_48k ;三、下板验证

(1)硬件环境

采用一个ZedBoard+AD9361_FPGA开发板作为发射,和一个zynq+9361集成的sdr作为接收,一个作为发送,连接方式如下图所示:

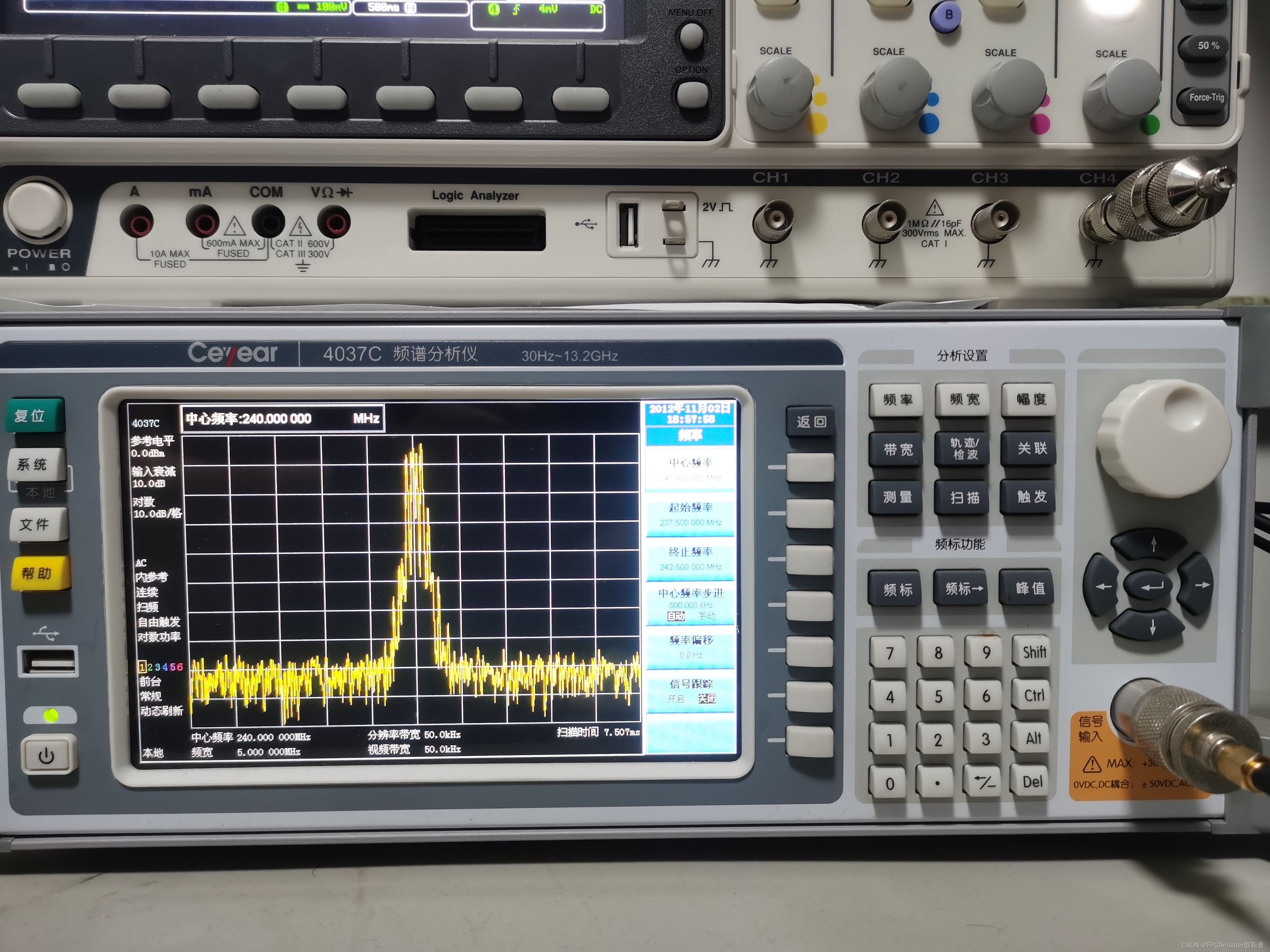

(2)测试

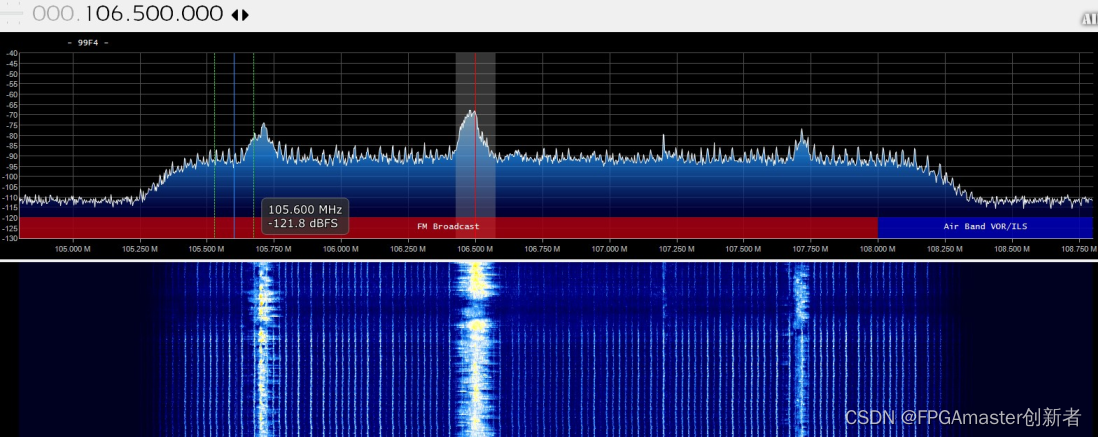

频谱仪查看发射信号:

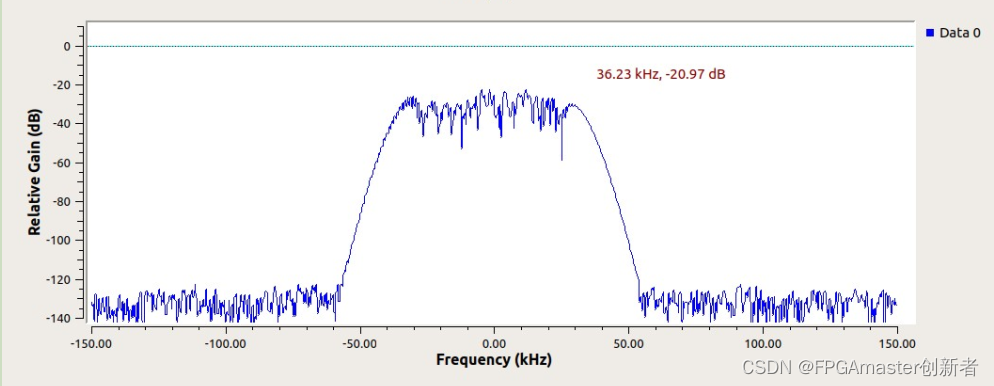

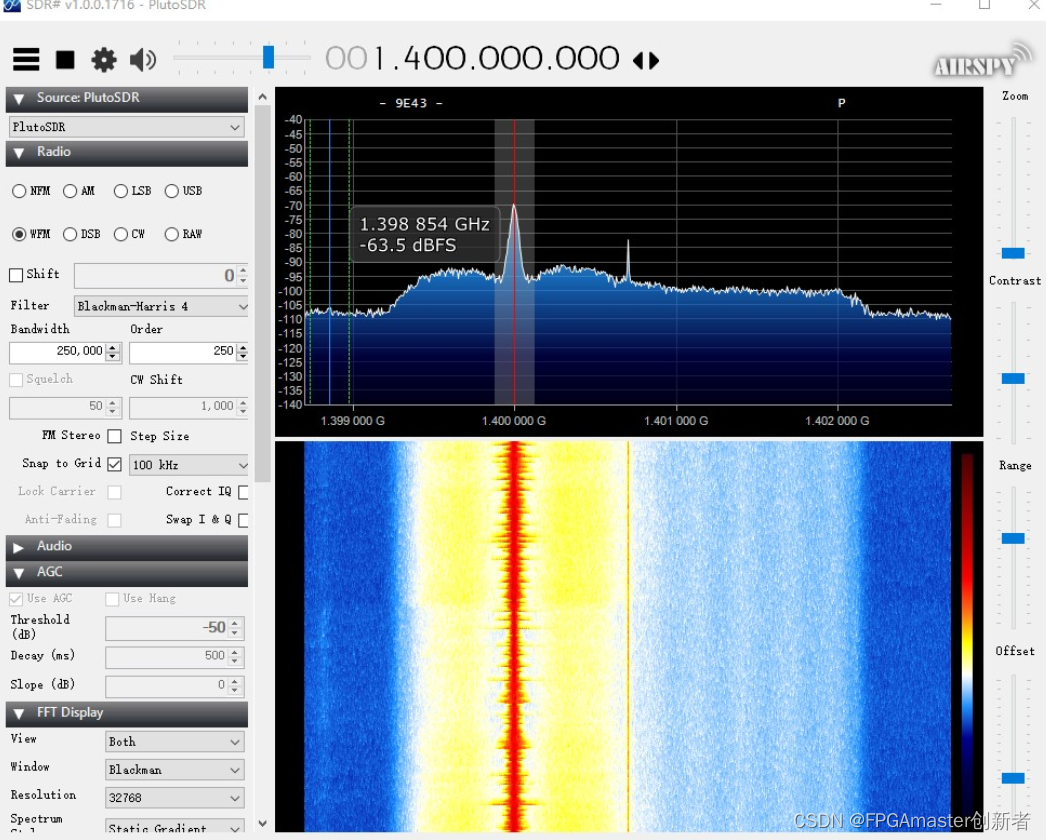

SDR查看时域:

SDR接收验证:

可见本设计接受广播信号是完全没问题的,非常稳定!!

如上几幅图,可以看出来9361的发射和接收都没问题。

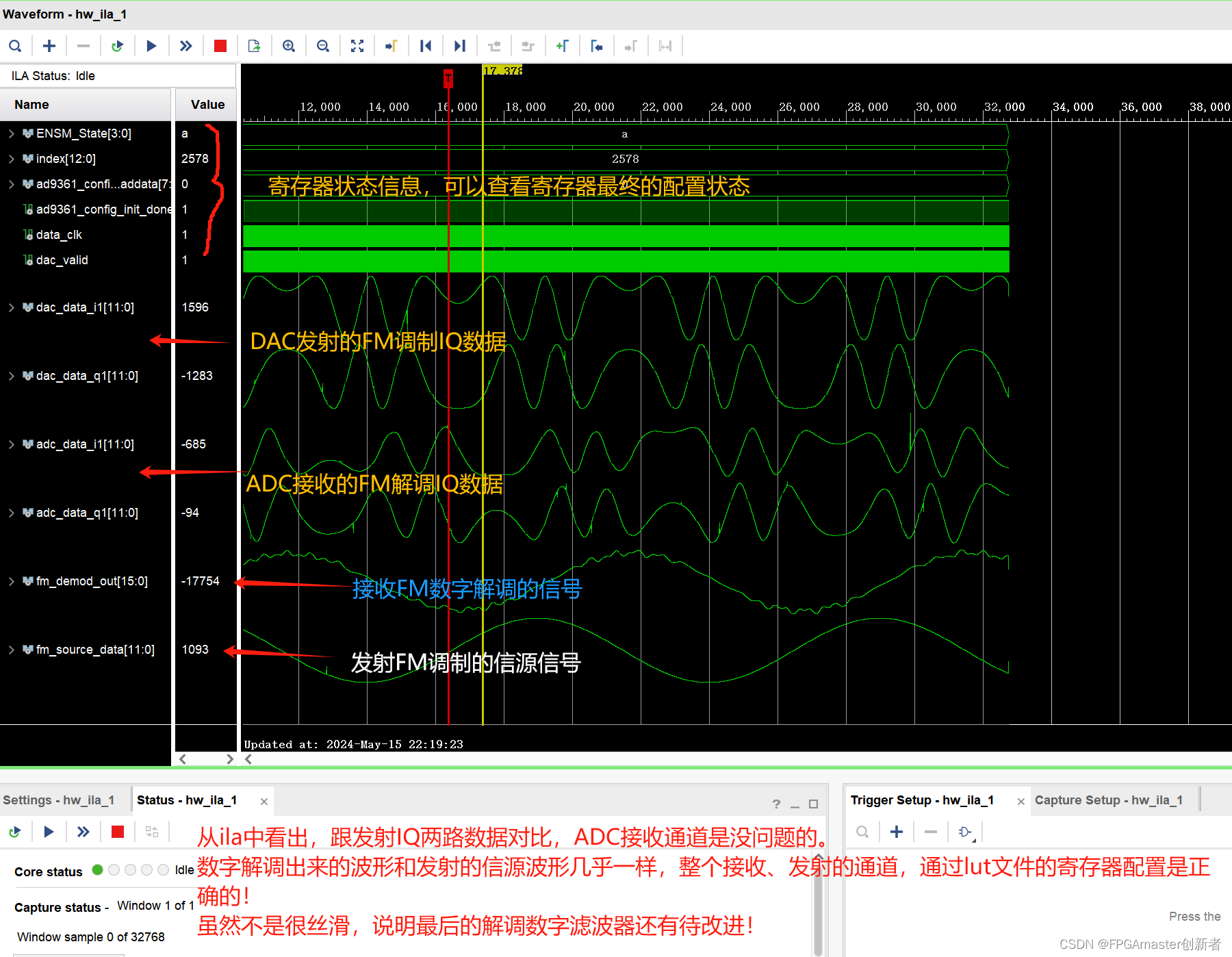

最后通过ila查看数字域信号:

通过ila可以发现,9361的发射IQ数据通路和接收IQ数据通路,几乎完全相同,说明本设计的FM调制解调没问题,成功!!

至此FM调制解调的部分就已经结束了,后期更新QPSK调制解调部分

完整工程文件下载:纯逻辑设计AD9361发射FM 提取码:w515

如果感觉文章对您有用,麻烦三连支持一下,方便下次用到的时候,就可以快速找到我,非常感谢您的支持!!!

8130

8130

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?