脉动阵列实现卷积计算

1、将卷积计算转化为矩阵与矩阵乘

2、通过脉动阵列实现矩阵乘法

脉动阵列的概念最早在1982年提出,在2017年6月26日的第44届International Symposium on Computer Architecture (ISCA)上,谷歌公司提出了用于数据中心服务器端进行神经网络推理加速的张量处理器Tensor Processing Unit (TPU) ,其相比于服务器端的CPU与GPU速度快了近15-30倍。(谷歌论文:In-datacenter performance analysis of a tensor processing unit)

将卷积计算转化为矩阵乘法运算

此处可参考文章:链接: link

例一:

例二:如下图,特征图像 F 大小为 3 x 3,通道数为 2;卷积核 W 和 G 大小为 2 x 2,卷积核个数为 2。

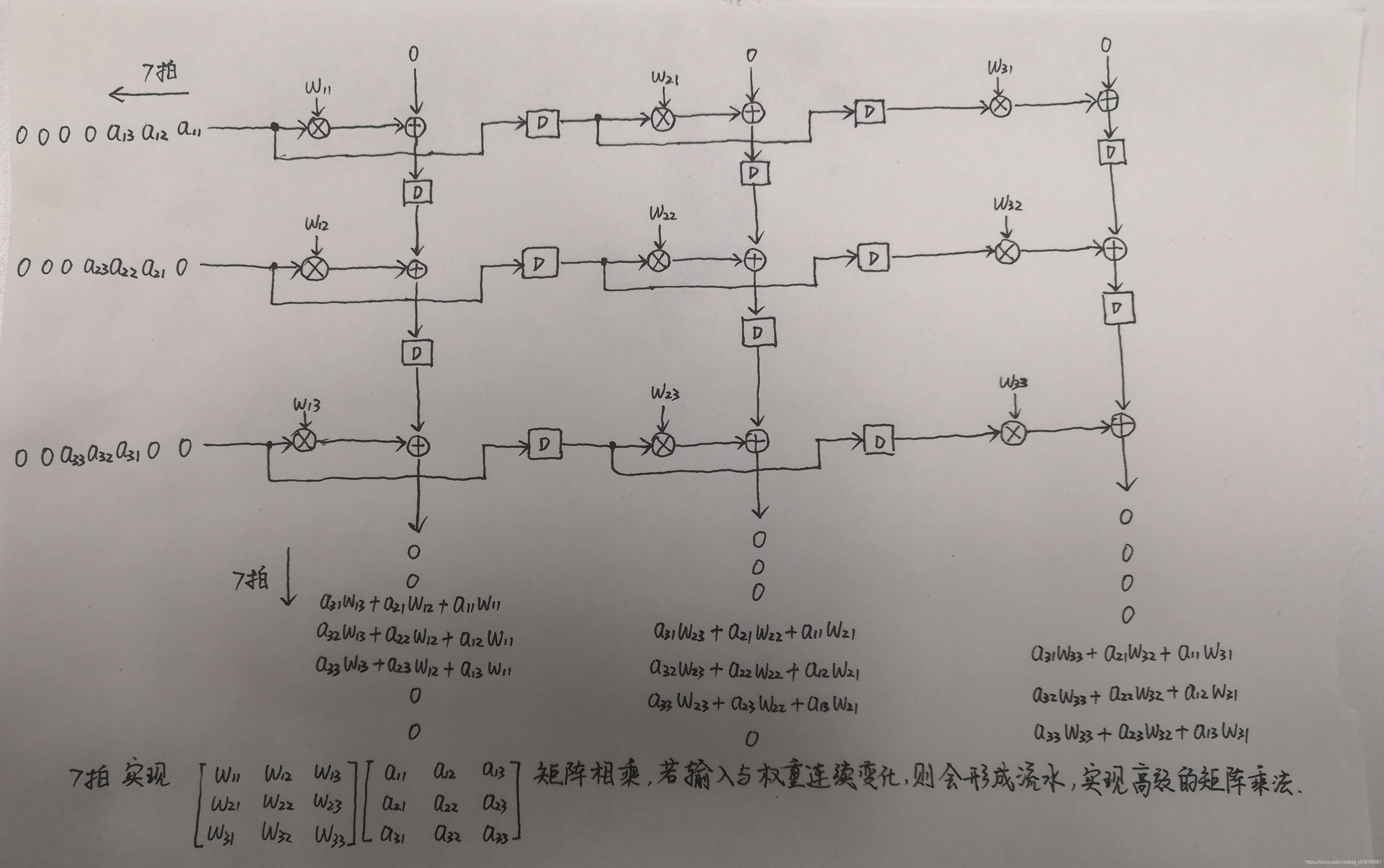

通过脉动阵列实现矩阵乘法

每一个PE就是一个乘加器MAC。

值得注意的是,在使用脉动矩阵进行矩阵计算的时候需要对数据调整好形式,按照一定顺序,分时进入脉动阵列。

模式一:在脉动阵列中流动的是输入和权重乘的中间结果,权重存储在脉动计算单元中。

(参考文章:链接: link)

数据的输入与输出在不同列方向是错拍的,但是有多个矩阵相乘时,可以实现连续流水错拍输出。当脉动阵列的规模很大时,大尺度的矩阵相乘也会在较少的时钟周期下按节拍输出,十分高效。

模式二:在脉动阵列流动的是输入和权重,而每一步的结果保存在脉动计算单元中。

(参考文章:链接: link)

本文是我对我看的文章的一个简要概括。(引用的文章在文中都有链接,内容更加详细,介绍更清楚)

5894

5894

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?