软件安全机制分类

1. 与软件本身、基础软件或者操作系统失效探测、指示和减轻有关的自检或监控功能

- 软件程序流监控

- 输入输出合理性检测:软件回读写入数据、软件回读传输数据等、传感器合理性检查

- 基础软件自检:软件自检

2. 与安全相关硬件要素故障探测、指示和减轻相关的功能

- 基础软件相关安全机制包括控制单元电源、时钟、内存等硬件要素的故障信息探测、指示和控制:软件测试内部硬件诊断、软件测试像素接口协议故障检查软件测试TS功能包括故障测试、boot时PBIST内存检查

3. 使系统达到或维持安全状态或降级状态的功能

- 错误管理、安全状态等

随机故障完整性要求包括满足永久和瞬态故障的单点故障度量(SPFM)目标、潜在故障度量(LFM)目标、永久和瞬态故障的安全故障分数(SFF)目标、随机硬件故障概率度量(PMHF)

FIT目标和基于假设用例的硬件故障概率(PFH) FIT目标

DRA829/TDA4VM产品关键核心包括带标量和矢量核的下一代DSP、专用深度学习和传统算法加速器、用于通用计算的最新ARM和GPU处理器、集成的下一代成像子系统(ISP)、视频编解码器、以太网集线器和隔离的MCU岛。所有的汽车级安全和安全硬件加速器的保护。

TI为Arm内核提供了一套完整的软件和开发工具,包括处理器SDK Linux-RT, RTOS和Android,以及C编译器和调试接口,用于查看源代码执行

应用程序包括:

• ADAS环绕视图感知/停车辅助

• 汽车信息娱乐集成驾驶舱与导航,媒体和音频

• 汽车中央网关

• 域控制器

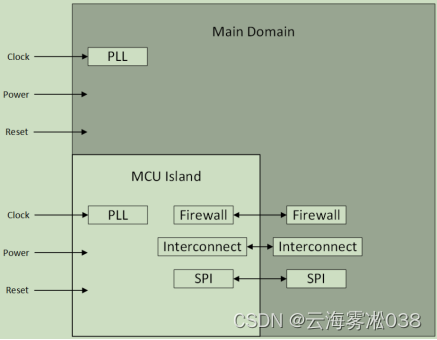

DRA829/TDA4VM器件通过在内部集成单独的MCU来执行监控系统安全功能的运行的任务,MCU域由Arm Cortex-R5F

CPU及其L1缓存和紧耦合存储器(TCM),互连,SRAM和外设组成,可以配置为同步运行。这个域称为MCU安全岛,具有独立的电压电源,并提供独立的时钟和复位,甚至还有一个单独的内部SPI平面用于通信

外设配置(锁步、防火墙、FFI)

每个Cortex-R5处理器都可以配置,以便在复位时在双CPU性能模式(在这种模式下,每个CPU独立运行)和安全应用的冗余锁步模式之间切换。在lockstep模式下,第二个CPU充当第一个CPU的冗余副本。第二个CPU以两个时钟周期的延迟执行第一个CPU执行的所有操作,并在每个时钟周期比较每个输出。这种比较可以检测到任一R5中的故障。每个R5都配置为通过布局技术具有物理分集,以及通过处理器之间的两个周期延迟具有时间分集。这有助于防止可能影响两个R5处理器的比较的常见原因错误

FFI设计

1. 主、MCU域隔离,时钟、电源、复位独立

安全处理器在其自己的领域(称为MCU领域)和SOC的其余部分(包括应用处理器)中分离出来。这些域中的每一个都包含专用外设、互连和配置逻辑。这确保了MCU域中的R5

MCU可以使用专用资源独立执行。提供给MCU域的电源轨与主域的电源轨是独立的。单独的时钟振荡器为主域和MCU域提供独立的时钟。主域和MCU域的独立复位引脚,提供了在MCU域仍处于活动状态时复位主域的灵活性。

2. 安全启用互连和超时垫圈

在DRA829 /

TDA4VM中,为了满足目标应用的高安全性要求,需要进一步将安全处理能力从MCU岛扩展到SOC的其余部分或主域。这进一步加强了对免受干扰自由(FFI)所需的安全机制的需求。主板与单片机主板之间的互连总线具有安全特性,可以在单片机主板上实现ASIL-

D功能。这些安全功能包括大多数关键控制信号的完全冗余,数据信号的ECC,选择控制和地址信号的奇偶校验。在主域和MCU域互连之间也有超时垫圈,以避免在互连中挂起。

3.集中的配置管理和错误处理

位于MCU/WKUP域中的设备管理和安全控制器负责在MCU和主域中配置防火墙和时钟,电源和复位控制。这种集中控制配置是必要的,以避免较低的ASIL

IP错误地改变设备配置。同样,MCU域是报告设备错误的主域。聚合来自不同模块的错误相关事件的ESM模块被放置在主域和MCU域中。主ESM错误信号被路由到MCU

ESM,以便当主域中出现不可纠正的错误时,MCU域可以采取必要的行动。

SRAM故障主要来源于瞬态故障

诊断实施指导——ARM Cortex-A72 子系统

• A72SS.CPU3 - MMU - MMU违规是通过ARM架构手册中的MMU异常处理机制来处理的

• A72SS.CPU5 -非法操作和指令捕获-非法操作导致异步中止,必须由异常处理程序处理

• A72SS.RAM1 -内存ECC -单比特修正不会导致任何中止,但会记录在ARM状态寄存器中。双位错误导致异步数据中止

• A72SS.RAM4 -内存奇偶校验-指令缓存中的单个位错误导致缓存线被重新取出。这被记录在内部ARM状态寄存器中

1. 多样化的软件冗余 ——A72SS.CPU1B

这种技术创建了两个冗余的软件实现,每个实现都使用不同的软件路径或算法。这些软件输出相互比较,在不匹配的情况下,软件采取缓解措施或发出故障检测状态的信号。例如冒泡排序、堆排序并比较输出。

该诊断的有效性高度依赖于应用程序和诊断实现。有效性可以通过使用软件仪器测试来评估。软件可能通过使用软件来代理影响软件执行中任意数量的中间步骤的硬件错误而造成不匹配。例如软件故障将两个不正确的数字相加,模拟CPU加法器中的错误,并演示比较代码捕获错误。

2. 软件的互反比较 ——A72SS.CPU1C

在这种技术中,两个独立的核交换和比较数据。如果发生不匹配,软件将采取缓解措施或发出故障检测状态的信号。该诊断的有效性高度依赖于应用程序和诊断实现。有效性可以通过使用软件仪器测试来评估。软件可能通过使用软件来代理影响软件执行中任意数量的中间步骤的硬件错误而造成不匹配。例如,软件可能故意将两个不正确的数字相加,以模拟CPU加法器中的错误,并演示比较代码捕获错误。

有许多方法实现诊断,例如使用不同的内核(将R5和A72比较)、使用不同的算法、不同的模式(如使用R5上的雷达数据识别障碍物,并与A72上处理的声呐识别障碍物进行检查)

3. 编码处理 ——A72SS.CPU1D

在编码处理的情况下,输入数据通过功能转换进行修改,这样正确的可能结果的数量是固定和已知的,错误很可能导致非法的结果。如果出现非法结果,软件将采取缓解措施或发出故障检测状态的信号。编码处理可以通过独立的核心或进程进行非法结果检查来进一步改进。该诊断的有效性高度依赖于应用程序和诊断实现。有效性可以通过使用软件仪器测试来评估。软件可能通过使用软件来代理影响软件执行中任意数量的中间步骤的硬件错误而造成不匹配。例如,软件可能故意将两个不正确的数字相加,以模拟CPU加法器中的错误,并演示比较代码捕获错误

4. 程序序列监控 ——A72SS.CPU1E

许多应用程序通过代码都知道预期的执行路径。在执行代码时,将构造所取路径的记录,并将其与软件循环执行结束时的期望值(或一组合法值)进行比较。例如,软件可以跟踪循环迭代的次数或调用了哪些子函数。程序序列监控还应该考虑到预期的事件(比如每秒接收到的图像帧数)

将程序序列监视与看门狗执行结合起来是有效的。例如如果程序序列不像预期的那样进行,那么看门狗就不能得到适当的服务。该诊断的有效性高度依赖于应用程序和诊断实现。有效性可以通过使用软件仪器测试来评估。软件可能通过使用软件来代理影响软件执行中任意数量的中间步骤的硬件错误而造成不匹配。例如,软件可能有意跳过预期的函数调用,并证明程序序列监视捕获了错误。程序序列监控也是一种有用的技术,即使其他技术(CPU1B/C/D)也被采用

5. LBIST的执行 ——A72SS.CPU2

该器件架构支持使用硬件逻辑BIST

(LBIST)引擎,该引擎可用于在晶体管级别对选定模块(cpu和指定硬件加速器)提供非常高的诊断覆盖率。该逻辑利用插入设备的相同测试设计(DFT)结构,以快速执行高质量的制造测试,但使用内部测试引擎而不是外部自动测试设备(ATE)。

LBIST机制要求在测试时将模块与设备逻辑的其余部分隔离。还需要在LBIST之前执行完整的上下文保存。当测试执行完成后,模块将被重置。设备逻辑的其余部分继续正常运行。强烈建议在开机时运行LBIST,以便检测永久故障和潜在故障(诊断机制中的永久故障)。可以通过使用上下文保存/恢复在运行时运行LBIST,但这是可选的,CPU1B/C/D/E应该被用作检测永久故障的主要方法

6. MMU ——A72SS.CPU3

本设备实现的Cortex-A72

CPU包括一个MMU。MMU逻辑可以通过进行虚拟地址到物理地址的转换和执行访问策略,在设备内存中提供软件任务的空间分离。期望操作系统控制MMU,并根据每个任务的需要更改MMU的设置。违反配置的内存保护策略将导致CPU中止。强烈建议使用MMU。

MMU还可以配置内存系统的内存排序策略。默认情况下,所有外设访问都是强排序的——这意味着所有按顺序完成的事务都被发出,没有写事务被缓冲。如果需要,操作系统可以将访问配置为设备-

这意味着写入是缓冲的。这可以提高强有序模型的性能,但代价是一定的确定性。强烈建议将被认为具有关键配置的模块设置为强有序访问模型。

MMU功能可以通过功能软件测试进行检查,以确保正常运行和错误响应。此外,当MMU执行CPU测试时,LBIST诊断提供对MMU的检查。

7. 使用PMU进行在线分析 ——ARMMU.CPUA

A72 CPU包含一个PMU (performance monitoring

unit)。此逻辑旨在用于调试和代码分析目的,但它也可以用作安全机制。PMU包括一个CPU周期计数器以及三个额外的计数器,可以编程来计算许多不同的CPU事件

可以监控的CPU事件示例包括:

• CPU诊断检测到ECC或奇偶校验错误的周期数

• CPU处于活锁状态的周期数

• 执行的指令数

• 异常发生的周期数

有了这些信息,就可以生成一个软件例程,定期检查PMU计数器的值,并将这些值与正常操作期间期望的配置文件进行比较。PMU默认不使能,必须通过软件配置。可以通过执行LBIST诊断来检查PMU诊断。使用PMU进行在线诊断分析是可选的

8. 非法操作和指令缺陷 ——A72SS.CPU5

A72

CPU核心包括对非法操作的诊断和可以作为安全机制的指令。许多这些陷阱在复位后不启用,必须由软件配置。强烈建议安装软件处理程序来支持硬件非法操作和指令捕获。

CPU非法操作和指令陷阱的例子包括:

• 非法指令

• 浮点下溢和溢出

• 浮点数除以零

• 侵犯特权

9. 静态配置寄存器的周期性软件回读/写配置的软件回读 ——A72.CPU6/A72.CPU7

A72有许多定义处理器配置和状态的配置寄存器。这些寄存器的设置应该由负责设置它们的软件实体检查(例如,不同的寄存器设置由Hypervisor或OS控制,而不是应用程序)。这些寄存器在v8-A体系结构规范和A72

TRM中定义

10. MMU功能的软件测试包括错误测试 ——A72SS.CPU-T2

软件可以通过尝试非法访问来测试MMU功能。例如,应用程序可以尝试访问它没有访问权限的地址空间,并观察是否发生了适当的异常。异常处理程序在协调这一点时应该小心,因为MMU访问违规通常会被视为致命的

11. PMU功能的软件测试包括错误测试 ——A72SS.CPU-T3

PMU分析是通过比较PMU捕获的概要文件和在软件中比较预期的概要文件来完成的。该函数的测试将包括故意错误比较和检查系统响应

12. 非法操作和指令捕获的软件测试包括错误测试 ——A72SS.CPU-T4

为了测试非法指令捕获,应该有意地执行非法指令(例如除零)并测量系统响应。在软件级别应该特别小心,因为这些类型的错误通常被视为致命的异步中止,因此需要与异常处理程序(例如管理程序或操作系统)进行特殊协调

诊断实施指导——Boot ROM

1. 设备配置完整性的软件检查 ——BROM3

在应用软件初始启动之后,在将系统从安全系统状态释放之前,应用软件应该对设备配置进行全面检查,以确认设备配置状态是运行安全功能的预期配置。

2. PMIC安全系统状态控制 ——BROM4

PMIC提供输出以保持系统处于安全状态,直到设备确认安全功能准备开始。

PMIC有一个EN_DRV引脚,可以在设备启动期间和安全回路启动之前将系统置于安全状态。

在启动时,PMIC将EN_DRV保持在低电平,直到MCU通过I2C写命令将其设置为高电平。为了将EN_DRV设置为高,MCU必须为看门狗服务,并且必须在PMIC中启动错误信号监控,并且必须清除所有挂起的中断位。

在安全关键故障时,例如设备MCU域的输出电源错误,PMIC立即将EN_DRV拉低

3. 执行软件进度跟踪 ——BROM5

在boot过程的执行期间,boot启动软件跟踪执行的顺序和进度

诊断实施指导——Clock时钟

1. 片上振荡器时钟检测 ——CLK1

此诊断用于检测主时钟振荡器(Wake

up或MCU域晶体振荡器)的故障。在上电复位状态下默认开启。可以将ESM配置为在safety_error引脚上报告此错误,以便外部监控系统进行干预并使设备进入安全状态

2. 双时钟比较器 ——CLK2

双时钟比较器(DCC)用于检测不正确的频率和时钟源之间的漂移。DCC使用另一个输入时钟作为参考来测量可选时钟源的频率。参考时钟和被测时钟均可通过软件选择,时钟频率的预期比率也可通过软件选择。共有16个DCC实例(MCU域3个,主域13个)

诊断实施指导——PBIST

1. 内存检查(启动时) ——PBIST1

PBIST提供了一种可靠的方法来识别内存中的卡滞/永久故障。建议上电复位时运行PBIST检查内存。由于它对内存内容具有破坏性,如果系统需要定期运行PBIST检查,则应该在进行PBIST检查后重置实例化PBIST的模块,并按照该模块推荐的协议进行初始化

2. 运行时内存检查 ——PBIST2

类似于PBIST1,但在正常运行时运行。本质上是破坏性的,需要在此检查后进行模块重置。由于需要在运行后重置,因此建议仅在对应用程序有意义的情况下才使用此诊断,例如,在上下文丢失不会中断的情况下,对正在进行常规处理(如图像帧)的实体进行周期性的PBIST和重置

3. PBIST软件测试 ——PBIST-T1

PBIST有一个内置的负面测试(故意注入的错误),可以用来显示比较器的工作情况

4. 自动覆盖 ——PBIST-T2

PBIST对每个周期进行比较。PBIST自动覆盖意味着,如果模式生成中存在错误,那么逐个周期的期望值比较将失败

诊断实施指导——SMMU

1. 软件测试基本功能,包括故障测试 ——SMMU1

软件测试可以用来测试基本功能,以及注入诊断错误和检查正确的故障响应。这样的测试可以在启动Boot时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义。此类测试的一个示例涉及访问允许此类访问的外设以及由于故意使用非法id或属性而导致错误而被拒绝的情况。地址转换也可以用类似的方法测试物理上不连续的内存块,方法是使用内绑定和外绑定地址区域。

2. 非法越界交易的错误捕获 ——SMMU4

区域用软件配置的大小在地址转换块中定义。如果事务从区域开始并跨越区域边界,则检测到边界跨越错误。错误响应和任何必要的软件需求由系统集成商定义

3. 控制和地址信号的奇偶校验 ——SMMU8

奇偶校验是一种在互连中提供防止单比特故障的机制,无论是永久的还是瞬时的(软错误)。奇偶校验是在通过SMMU的事务的内部总线接口上实现的。在互连中检测到的奇偶校验错误将导致断言一个事件,以指示检测到错误,并将识别错误位置的信息记录下来,供软件在诊断中使用。共享模块接口(称为ECC聚合器)为系统集成商提供了访问错误检测状态和日志信息的权限

4. 关键控制信息的复制 ——SMMU9

在互连中最关键的控制信号上提供了完全的硬件冗余。该实现可以检测信号中的错误,并在检测到错误时标记错误。共享模块接口(称为ECC聚合器)为系统集成商提供了访问错误检测状态和日志信息的权限。注意,对于经过SMMU的事务,关键控制信号在内部总线接口上是重复的

诊断实施指导——Timers定时器

1. 使用第二个计时器用1oo2逻辑进行投票 ——TIM1

计时器模块包含一个升计数器,可用于提供操作系统时间刻度。通过软件对两个计时器中的计数器值进行定期检查,第二个计时器可以用作对第一个计时器的诊断。设备中其他基于时间的计数器也可用于支持这种诊断。其他基于时间的计数器包括Cortex-R5F

CPU内部的PMU

CPU周期计数器、ARM通用计时器和导航子系统中的计时器管理器。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商实现的软件定义。对于目标为99%诊断覆盖率的系统,建议使用多个计时器来实现此诊断

2. 软件测试基本功能,包括故障测试 ——TIM2

软件测试可以用来测试基本功能,以及注入诊断错误和检查正确的错误响应。这样的测试可以在启动时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义。

该测试的一个示例将涉及设置一个短计时器值,然后期望发生中断

3. 内部看门狗(DWD) ——CLK5A; 内部看门狗(DWWD) ——CLK5B

; 外部看门狗 ——CLK5C

该装置内部有两种操作模式:数字看门狗和数字窗口看门狗。该设备还支持用于设备监控的外部看门狗。这些内部和外部看门狗计时器可以有效地在TIM1和TIM2诊断之上提供诊断覆盖。对于CLK5A,用户为看门狗编程一个超时限,并在计数器过期之前为看门狗提供一个预定的响应。在带窗口看门狗的情况下,用户编写上界和下界以创建一个时间窗口,在此期间,软件向看门狗提供预定的响应。

外部看门狗,当使用时,减少了共模故障的可能性,因为看门狗利用时钟,复位和电源与被监控的设备分开。因此,强烈建议采用外部监督机构,而不是内部监督机构

DRA829/TDA4VM安全手册

系统性失效通过流程避免,而随机性失效被相关安全机制等检测和响应,系统集成商需要审查FMEDA安全分析报告和安全手册中的诊断机制。

故障响应机制

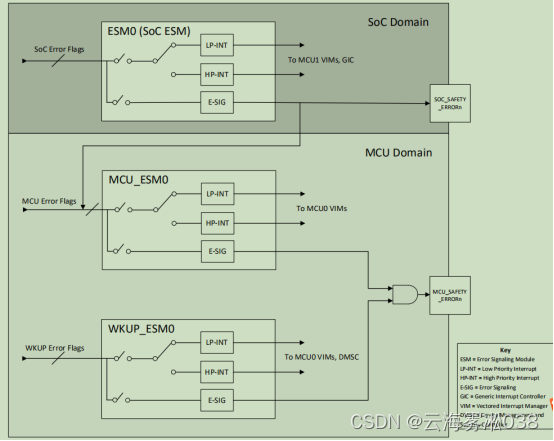

TDA4VM用的是ESM模块来实现故障的响应和管理。ESM报告故障时是故障检测状态,ESM模块框图如下:

LP-INT 低优先级中断 HP-INT高优先级中断 E-SIG故障号

GIC通用中断控制器 VIM矢量中断管理器 DMSC设备管理和安全控制

ESM会将SoC或者MCU所有安全相关事件集合到xx_SAFETY_ERRORn,向处理器发送中断信号,外部I/O在最短时间内保持asserted有效。此时如果错误被内部处理器清除,引脚pin变成inactive状态,如果Pin没有处于inactive,会有外部机制进行干预处理。

ESM提供错误中断输出LP-INT和HP-INT,便于在发生错误事件时,处理器可以发出信号进行干预。

ESM提供错误引脚输出SoC_SAFETY_ERRORn和MCU_SAFETY_ERRORn,向外部代理(如PMIC)发出信号表明错误需要干预处理。错误引脚在(最短时间间隔过期、导致错误引脚assert有效的事件清楚、将CLEAR写入错误引脚寄存器PIN_CTRL)后deassert无效。

ESM在系统转换为安全状态前进行错误纠正。

安全机制类别

TDA4VM中包括以下类型的安全机制:

1. 硬件安全机制:TI实现检测故障传达错误状态的诊断,由软件开启此诊断

2. 软硬结合安全机制:TI较为推荐的一种测试,此诊断使用的硬件的故障模式作为安全分析/FMEDA的一部分进行分析/cover,软件部分由系统负责分析

3. 软件安全机制:TI推荐的测试,完全由软件使用,此诊断中软件的故障模式在安全分析/FMEDA中分析/cover

4. 系统安全机制:由外部设备实现的诊断,例如用于安全机制的外部监控视为系统安全机制

5. 诊断测试:此测试只提供诊断机制上的故障覆盖率,不提供主要功能的覆盖率

6. 可选择诊断:特定的一种诊断测试,不能检测硬件中的故障,但是能识别主要功能故障(其他诊断无法检测到的)

安全机制描述

tip:对于IP Vendor来说,我们就是系统集成商

- 12bit TLP序列号计数器 (PCIe中,TLP事务级包)

PCIe发送器在每个TLP中插入一个12bit

序列号。PCIe接收器检查TLP序列号的连续性,以此确保数据包按照预定顺序送达。如果序列号不连续,接收方需要请求重发数据包。

- 使用第二个自旋锁进行1oo2逻辑投票 (1out of 2,可以满足SIL3要求)

自旋锁模块包含多个用于原子处理器间通信的自旋锁。第二个自旋锁用于对第一个自旋锁的诊断。错误响应、软件需求均由系统实现的软件定义

- 使用第二定时器进行1oo2逻辑投票

1oo2通道架构是在IEC 61508中定义的,在此情况下,oo2架构是一个双通道系统,双通道任意一个通道都可以执行安全功能,对比结果确保匹配。

定时器Timer包含一个升计数器up-conter,可以用于提供一个操作系统的时间节拍time-

tick。通过软件对两个定时器中的定数器进行周期性检查,第二定时器可以用于诊断第一定时器。设备中其他基于时间的计数器也可以用于支持这样的诊断。基于时间的计数器包括在Cortex-R5F

CPU内部的性能监控单元(PMU)、Cortex-A53子系统内部的ARM通用定时器、NAVSS中的定时器管理器。错误响应、软件需求等由系统集成商实现的软件定义。

全局时间基计数器GTC模块包含一个升计数器可以用于提供MPU定时器的时间刻度值。通过软件对两个定时器中的定数器进行周期性检查,第二定时器可以用于诊断第一定时器。设备中其他基于时间的计数器也可以用于支持这样的诊断。基于时间的计数器包括NAVSS的通用计数器、定时器管理器。错误响应、软件需求等由系统集成商实现的软件定义。

定时器管理器模块包含一个升计数器用于提供该定时器管理器计数器(Timer Manager

timers)的时间刻度值。通过软件对两个定时器中的定数器进行周期性检查,第二定时器可以用于诊断第一定时器。设备中其他基于时间的计数器也可以用于支持这样的诊断。基于时间的计数器包括通用定时器。错误响应、软件需求等

由系统集成商实现的软件定义 。

- 使用第二计时器进行1oo2逻辑投票 (用于投票器滴答tick)

定时器管理器模块包含一个升计数器用于提供该定时器管理器计数器(Timer Manager

timers)的时间刻度值。通过软件对两个定时器中的定数器进行周期性检查,第二定时器可以用于诊断第一定时器。设备中其他基于时间的计数器也可以用于支持这样的诊断。基于时间的计数器包括通用定时器。错误响应、软件需求等由系统集成商实现的软件定义。

- 8/10-bit编码(Gen2, Gen1) 128/130-bit编码(Gen3)

PCIe物理层发送器对Gen1/Gen2/Gen3使用8b/10b或者128b/130b代码进行数据编码,此编码可以确保PCIe接口接收器从数据流中恢复时钟。

补充:Gen1是PCI-E 1.0模式,传输速率是5Gbps;Gen2是PCI-E插槽的运行模式(PCI-E

2.0模式),传输速率是10Gbps;Gen3是PCI-E 3.0模式,兼容PCI-E 1.x和PCI-E

2.x设备,去除8b/10b编码机制,避免20%的原始传输率的浪费。

- 使用防火墙进行访问管理 (master的资源访问权限管理)

互连子系统包括防火墙,主要位于互连的从属终端。防火墙根据主服务器的优先级ID(privID)、transaction事务特权和事务类型,对资源的访问限制到选定的主服务器。不符合防火墙权限的事务被检测到,写操作不会完成,读操作返回0,将该事件记录并生成一个错误事件。这一机制通过软件进行测试。

- 确认错误检测

当CAN网络上的某个节点接收到一个已发送的信息,它会发送一个成功接收的确认信息。当发送的信息未被接收节点确认时,发送CAN标记“确认错误”。错误响应和软件需求由系统集成商定义。

- ADAS置信因子

在光流optical flow立体计算机视觉中,计算像素如何在帧间移动。标准做法是生成一个置信因子。置信因子的使用分三个层次:

1. (自动automatic)置信因子主要用途是作为瞬时算法质量instantaneous algorithm quality的指标

2. (自动)区分故障条件下的低分辨率像素poor pixel

3. (软件辅助)软件可以使用很高的低置信因子率作为重大过失gross fault状况的指示器(多像素或卡在故障上)

错误响应和软件需求等由系统集成商定义。

- 地址和数据路径奇偶校验

USB控制器对地址/数据路径和控制路径进行奇偶校验。地址/数据路径包括在USB控制器端口接口(UTM/PIPE)和AXI接口之间的地址和数据逻辑总线。例如TRB读取,必须从系统内存中取出TRB到内部RAMs中。奇偶校验不会重叠CRC校验的数据点,除了AXI接口,还会对APB接口地址和数据路径进行奇偶校验。如果检查失败则触发错误中断。

- 地址和数据路径奇偶校验错误探测器

当在APB接口上使用奇偶校验传递选项发送读写事务,用户逻辑可以提供不正确的奇偶校验和APB接口的地址或数据,标记为“asf_dap_err”。奇偶校验传递选项可以使用“asf_par_passthru_en”在APB接口上输入错误的奇偶校验,从而导致奇偶校验错误在ASF故障日志寄存器中报告。

- 地址路径损坏检测

PCIe

IP内部地址包括奇偶校验保护,可以作为一个可配置选项快速检测错误。当选择此选项时,AXI接口之间的地址路径关键部分使用一个额外的1bit奇偶校验保护方案进行保护,以便单比特位故障可以被检测到。该机制可以保护地址路径中永久性和暂时性故障。

- 对齐异常检测 (接收帧包含不均匀字节数)

如果一个接收到的以太网信息帧包含不均匀字节数(不是8的倍数),模块会标记为对齐异常。错误响应和软件需求由系统集成商定义。

补充:对齐异常Alignment Error Detection是当CPU访问内存地址时,发现访问的地址是不对齐的,硬件会自动触发对齐异常。

-

模数转换器信息冗余技术包含在端到端安全机制 中

-

APB地址和数据奇偶校验诊断

该机制为数据/地址路径保护诊断提供测试方法。当奇偶校验通过选项使用“asf_par_passthru_en”参数,可以在APB接口注入错误的奇偶校验,这将在ASF故障日志寄存器中被检测到并报告。

- APB地址和数据奇偶校验保护

地址和数据路径

-

APB数据总线奇偶校验保护

-

APB地址总线奇偶校验保护

-

APB接口超时检测

-

ASF中断检查

-

用户观察音频

与软件相关的安全机制(1-328) :

- ASF中断检查

软件可以写ASF_INT_TEST寄存器来强制触发ASF中断引脚。这可以定期检查ASF中断引脚是否正常工作。这必须是周期性的,以便能够检查故障

- Aux事务故障探测

AUX通道错误由DPTx控制器和/或系统软件检查。所有AUX事务都由请求和应答组成。请求总是由DPTx设备发送,并由DPRx设备接收。应答总是由DPRx设备发送,并由DPTx设备接收。应答的格式基于请求的类型(例如DCPD读或DCPD写)。每个请求的应答必须在最大超时内收到。如果未收到答复或收到损坏的答复,请求者可以重试请求。允许重试的次数取决于系统对所需故障响应时间的总体需求。如果AUX响应器接收到一个损坏的AUX请求,它应该响应一个NACK应答

- 通过软件控制PHY支持的BIST内部和IO回环

MMCSD

PHY支持BIST(内置自检),用于PHY内部的数字和模拟功能测试。BIST的功能是能够测试PHY的各种功能(不使用eMMC协议/软件堆栈),并将测试结果提供给诊断软件。BIST测试可以通过软件通过内存映射触发寄存器

- 错误码检测

当模块将信息传输到它的总线上时,它还可以监控总线,以确保传输的信息按预期出现在总线上。如果没有从总线回读期望的值,硬件可以标记错误并向CPU发出中断信号。此特性必须在软件中启用和配置

- 通道程序流监控

通道程序流监控是一种软件诊断,它利用软件定时器api来跟踪DMA相关的程序序列。这可以在每个通道的基础上或跨多个通道使用。计时器API跟踪UDMA完成中断,以确定程序序列是否已成功执行。此诊断符合程序序列监控(时间和逻辑)-

ISO 26262- 5:18附件D和IEC 61508-7附件a中描述的软件方法。请注意,UDMA

IP负责生成发送到中断聚合器的DMA完成事件,IA负责生成中断到处理器。UDMA IP不产生中断,而是产生事件通知IA产生中断

- 编码处理

编码处理是ISO 26262-5:2018附录D和IEC 61508-7附录a中描述的一种软件方法,其具体实施由系统集成商确定。

输入数据通过功能转换修改,这样正确的可能结果的数量是固定和已知的,错误很可能导致非法的结果。如果出现非法结果,软件将采取缓解措施或发出故障检测状态的信号。

该诊断的有效性高度依赖于应用程序和诊断实现。有效性可以通过使用软件仪器测试来评估。软件可能通过使用软件来代理影响软件执行中任意数量的中间步骤的硬件错误而造成不匹配。例如,软件可能故意将两个不正确的数字相加,以模拟CPU加法器中的错误,并演示比较代码捕获错误

- 配置寄存器损坏检测

配置寄存器是奇偶保护和连续监控的,这样,如果在任何字节上观察到任何单个位值的变化,就会产生一个中断,以通知系统软件可能的损坏

- 转换器校正测试/转换器自检

ADC模块实现了校准测试功能。校正测试能力可用于比较已知参考值的转换。重复执行校准测试可用于检测应用过程中的漂移。

ADC模块实现了输入自检功能。输入自检功能可用于检测输入中的短路和开路。

软件必须配置、启用和评估这些诊断的结果。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商实现的软件定义

- 消息负载中的CRC

MIPI规范定义的CSI输入协议具有CRC保护的有效载荷。由于视频流量通常是嘈杂的,CRC失败的数据包将被允许进入系统。在这种情况下,将更依赖于视频处理来过滤损坏的像素数据,而不管像素数据是从原始传感器(相机)开始损坏的,还是在数据传输到CSI模块期间损坏的。使用这种检测允许软件测量CRC的失败率作为故障的指示。如果CRC检测到每个数据包中都存在故障,则可能表明传输数据路径中存在故障。软件可以通过测量CRC错误之间的时间间隔来跟踪CRC错误率。高错误率可以作为系统意外故障的指示

- ECC保护CSI协议的报头

MIPI规范定义的CSI输入协议具有短报文,长报文的报头由ECC保护。不保护长报文(像素数据)的报文内容。单比特错误由ECC逻辑校正;多个比特错误导致报文被丢弃。将生成一个事件,用于纠正或丢弃条件,该事件可用于中断并警告更高层的错误软件。软件可以通过中断报告跟踪ECC错误率。较高的ECC错误率表明存在需要进一步注意的故障

- SPI数据溢出检测

如果多通道串行外设接口(MCSPI)

RX缓冲区在先前的数据被读取之前接收到新的数据,则现有的数据将被覆盖并丢失。如果发生这种情况,MCSPI硬件可以标记错误并对CPU产生中断。此特性必须在软件中启用和配置。

如果OSPI(八进制串行外设接口)RX缓冲区在之前的数据被读取之前接收到新的数据,则现有的数据将被覆盖并丢失。如果发生这种情况,OSPI硬件可以标记错误并对CPU产生中断。此特性必须在软件中启用和配置。

CSI

fifo包括溢出检测和报告。如果fifo已满,并且在读取之前的数据之前接收到新的数据,则数据将丢失。如果发生这种情况,溢出检测将标记一个错误并对CPU产生中断

- 数据结构完整性检查

外部软件检查由USB控制器存储在系统内存中的TRBs的完整性。例如,软件可以检查TRB指针字段是否指向预期的TRB。有关完整性检查的完整列表,请参阅安全手册第4.1.2节。程序错误响应和任何必要的软件要求由系统集成商定义

- 软件多样化冗余

多样化的软件冗余是ISO

26262-5:2018附录d中描述的一种软件方法,具体的实现留给系统集成商来确定。创建两个冗余的软件实现,每个实现使用不同的软件路径或算法。这些软件输出相互比较,在不匹配的情况下,软件采取缓解措施或发出故障检测状态的信号。该诊断的有效性高度依赖于应用程序和诊断实现。有效性可以通过使用软件仪器测试来评估。软件可能通过使用软件来代理影响软件执行中任意数量的中间步骤的硬件错误而造成不匹配。例如,软件可能故意将两个不正确的数字相加,以模拟CPU加法器中的错误,并演示比较代码捕获错误

- DMA配置检查

通过软件测试可以检查IDMA的配置情况。这样的测试可以在启动Boot时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义

- 双时钟比较器DCC

一个或多个双时钟比较器(DCCs)被实现为多用途安全诊断。DCC可以用来检测不正确的频率和时钟源之间的漂移。DCC由两个计数器块组成:一个用作参考时基,另一个用于被测时钟。参考时钟和被测时钟都可以通过软件选择,时钟频率的预期比率也可以通过软件选择。偏离预期比率会对ESM产生错误指示。有关实现的时钟选择选项的更多信息,请参阅特定于设备的数据表。有关DCC编程的详细信息,请参见技术参考手册。

DCC诊断默认不启用,必须通过软件启用。可以通过软件禁用和配置此诊断。DCC模块应用的周期性检查提供了一种固有的自检级别(自动覆盖),可以考虑将其应用于潜在故障诊断

- 数据信号ECC

ECC是一种通过允许检测和纠正单比特错误和检测双比特错误来提供增强的软错误保护的机制。在不能容忍由于互连总线错误而导致的系统崩溃的系统中,这是特别可取的。ECC保护总线总是防止单比特错误。有一个ECC聚合模块与互连,聚合状态从ECC总线到主机的单个中断。该聚合器还支持ECC单/双比特错误的软件可读状态以及错误位置等相关信息

- EFUSE CRC的软件检查

这是一个用于诊断的测试,应该由系统集成商在软件中实现。这个诊断测试为EFUSE

CRC硬件比较逻辑提供了覆盖范围。每个EFUSE链的期望CRC和实际CRC存储在mmr中。软件可以读取这些mmr并执行二次检查以确认EFUSE

CRC逻辑的结果,从而识别EFU2中解释的EFUSE比较逻辑中的任何错误

- 非法越界交易的故障捕获

区域用软件配置的大小在地址转换块中定义。如果事务从区域开始并跨越区域边界,则检测到边界跨越错误。错误响应和任何必要的软件需求由系统集成商定义

- 故障定位模块ELM

当读取NAND存储器时,软件将读取的数据以及存储在NAND中的ECC综合征馈送到ELM模块。ELM模块计算错误的数量并给出每个错误位的位置。基于ELM模块提供的信息,软件随后对读取数据中的适当位进行校正

- LBIST的执行

本设备支持使用硬件逻辑BIST

(LBIST)引擎。该逻辑用于在门级对选定模块(cpu和指定硬件加速器)提供非常高的诊断覆盖率。这种逻辑利用插入设备的相同的测试设计(DFT)结构来快速执行高质量的制造测试,但是使用内部测试引擎而不是外部自动化测试设备(ATE)。这种技术已被证明比基于软件的逻辑测试有效得多,特别是对于现代CPU中看到的复杂逻辑结构。

LBIST机制要求在测试时将模块与设备逻辑的其余部分隔离。还需要在LBIST之前执行完整的上下文保存。当测试执行完成后,模块将被重置。设备逻辑的其余部分继续正常运行。模块复位后,软件可能需要读取LBIST多输入签名寄存器(MISR)来验证LBIST测试的通过/失败状态,然后恢复上下文

- 通过SYSCLKOUT和OBSCLK进行外部监控

该设备为外部监控提供内部时钟信号。要识别导出的内部时钟,请参见特定设备的数据表。SYSCLKOUT和OBSCLK输出的内部时钟输出默认不开启,必须通过软件开启。可以通过软件启用和配置此诊断

- 外部看门狗

当使用外部看门狗时,有可能减少多核处理器(MCP)时钟系统的共模故障,因为看门狗可以利用与被监控系统分开的时钟、复位和电源。错误响应、诊断可测试性和任何必要的软件要求由系统集成商选择的外部看门狗定义。强烈建议使用外部看门狗,而不是内部提供的看门狗。

内部或外部看门狗可以提供无意激活逻辑的指示,导致对安全关键执行的影响。外部添加的任何看门狗应包括程序序列的时间和逻辑监视的组合或其他适当的方法,以便可以声称具有高诊断有效性

- 总线master访问防火墙

该模块进行由特权标识和特权模式标识的访问。建议将特权模式设置为user。互连中的防火墙应该配置为允许基于主机的特权标识和特权模式访问特定的外设和特定的内存范围。跨设备的关键配置寄存器预计仅限于特权模式。该模块的设置和防火墙中的设置的组合提供了一种机制,以防止该模块无意中配置寄存器或修改关键内存。可以通过生成软件事务和检查设备响应来测试该机制

- 帧超时监控

DSS(一旦正确配置)以固定的间隔生成DSS_VSYNC中断,以指示新帧开始。应该启用看门狗定时器来监视DSS_VSYNC没有停止和/或没有明显延迟。这样的事件表明显示失败

- 黄金帧测试

对于黄金帧测试,使用已知的预定义图像和配置进行比较,以便识别由于图像处理管道中的永久故障而在图像输出中引入的差异或噪声。此诊断可以在正常操作期间运行。但是,这将要求IP在运行诊断之前处于空闲状态。虽然不需要完整的上下文保存和恢复,但软件可能必须重新编程配置寄存器以恢复正常操作模式。这种诊断在任何用例中都是有效的。这种诊断在识别永久性故障方面非常有效

补充: Golden Frame 用于视频背景的更新,可以用来克服帧丢失, 是可以显示的

- 主机处理器结果握手故障注入与检测

可以用故意错误的软件测试传输主机处理器握手故障

- 主机调度超时故障检测

USB主机可以检测USB标准定义的传输调度超限协议错误。USB主机产生中断响应,以支持基于软件的处理和故障恢复。程序错误响应和任何必要的软件要求由系统集成商定义

- 非法操作和指令陷阱

A72

CPU包括对非法操作的诊断和可以作为安全机制的指令。许多这些陷阱在复位后不启用,必须由软件配置。强烈建议安装软件处理程序来支持硬件非法操作和指令捕获。

CPU非法操作和指令陷阱的例子 包括:

• 非法指令

• 浮点下溢和溢出

• 浮点数除以零

• 侵犯特权

- 通过软件对邮箱数据进行索引

通过使用邮箱单词中的元数据来跟踪单词顺序,可以检测FIFO溢出和欠运行,以及FIFO指针错误。使用每个32位邮箱字的前三位来存储增量索引,允许软件通过使用上面的三位作为索引或顺序id来跟踪邮箱中写入和读出的每个字是否按照正确的顺序完成。这减少了邮箱的吞吐量,但允许软件确保数据没有被另一个主机覆盖,或者没有FIFO指针错误导致溢出或欠运行。错误响应、诊断可测试性和任何必要的附加软件需求都由系统集成商实现的软件定义

- 信息冗余技术

信息冗余技术可以通过软件应用,作为该模块的附加运行时诊断。可以应用许多技术,例如回读已写入的值,以及对结果进行比较的相同数据的多个输出。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商实现的软件定义。

当定时器工作在PWM模式时,定时器输出信号可以连接到一个或多个GPIO输入。可以将GPIO输入配置为中断,该中断可以进行时间戳,以提供对PWM脉冲宽度的检查

- DMA的信息冗余技术

信息冗余技术可以通过软件作为DMA的附加运行时诊断来应用。可以应用许多技术,例如CRC、校验和和在同一传输中发送冗余数据。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商实现的软件定义

- 信息冗余技术,包括端到端安全

信息冗余技术可以通过软件应用,作为该模块的附加运行时诊断。为了为多核处理器(MCP)(线束、连接器、收发器)之外的网络元素提供诊断覆盖,应用了端到端安全机制。这些机制还可以在MCP内部提供诊断覆盖。应用了许多不同的方案,例如额外的消息校验和、消息或帧计数器或其他类似的机制。最常见的是将校验和添加到传输的有效载荷部分,以确保传输的正确性。除了任何协议级校验和之外,还应用这些校验和。由于校验和是由通信两端的软件生成和评估的,因此整个通信路径是安全的,从而实现端到端安全。

错误响应、诊断可测试性和任何必要的软件需求都由系统集成商定义

- 帧内冗余和帧间冗余

输入/中间像素数据本身是有噪声的。对接收到的图像数据进行进一步的处理,还可以由于路径上的各种处理块而得到修改。总的来说,算法链确保了对这些噪声的鲁棒性

- 接口超时故障检测器

为了测试接口超时功能,将IP中存在的超时寄存器编程为一个小值,例如“1”,并检查是否观察到“asf_trans_to_err”。对于IP中存在的所有接口超时寄存器,每次执行一次

- 内部看门狗-DWD

该设备支持使用在实时中断(RTI)模块中实现的内部看门狗。内部看门狗有两种工作模式:数字看门狗(DWD)和数字窗口看门狗(DWWD)。工作模式是互斥的,设计者可以选择使用其中一种模式,但不能同时使用两种模式。关于内部看门狗的编程,请参见设备相关的技术参考手册。

DWD是传统的单阈值看门狗。用户向看门狗编程一个超时值,并且必须在超时计数器过期之前向看门狗提供一个预定的“宠物”响应。超时计数器过期或不正确的“pet”响应将触发错误响应。DWD可以在检测到故障时发出内部(热)系统复位或CPU不可屏蔽中断。DWD复位后未开启。软件开启后,除系统复位或上电复位外,无法关闭免打扰功能。启用模块后,用户应注意不要更改DWD时钟源,否则行为不可预测。

DWWD是一种传统的窗户看门狗。用户编程一个上界和下界,以创建一个时间窗口,在此期间,软件必须向看门狗提供预定的“宠物”响应。未能在时间窗口内收到正确的响应或错误的“pet”响应将触发错误响应。DWWD可以在检测到故障时发出内部(热)系统复位或CPU不可屏蔽中断。复位后未使能DWWD。DWWD一旦被软件启用,除系统复位或上电复位外,不能被禁用。与DWD实现相比,时间窗口的使用允许检测额外的时钟故障模式。

内部或外部看门狗可以提供无意激活逻辑的指示,导致对安全关键执行的影响

- 锁步比较

该设备包括一个同步处理器诊断。该功能包括添加一个诊断性的Cortex R5F

CPU,该CPU与应用程序CPU组合成一个1001d(带有诊断通道的单通道)配置。应用程序CPU和诊断CPU都得到相同的输入信号,这导致两个CPU都运行相同的软件。诊断cpu和应用程序cpu应该生成相同的输出。CPU比较模块(CCMR5)比较CPU输出并标记所有与ESM的错误比较。

从模块复位开始,同步诊断将持续运行。当CPU被置于停止调试状态时,锁步检查被禁用,并且只能在随后的重置后恢复到操作状态。在执行CCMR5的自检检查功能时,也可以暂时禁用锁步功能

在复位后的第一个CPU操作周期中,有必要执行一个简短的初始化代码,将所有CPU寄存器设置为已知状态。这个代码序列可以在特定于设备的数据表中找到。执行这个代码序列作为重置的第一个指令是强制性的。

CCMR5逻辑通过软件触发硬件提供自我测试和错误强制能力。自检确保CCMR5比较逻辑正常工作。错误强制功能允许您测试对同步错误比较的系统级响应

- 内存ECC

ECC是一种通过允许检测和纠正单比特错误和检测双比特错误来提供增强的软错误保护的机制。ECC存储器总是防止数据中的单比特错误。内存的地址解码逻辑不包含在内存ECC逻辑中。模块内部有一个ECC聚合模块,它将来自ECC存储器的状态聚合到主机的单个中断中。聚合器还支持ECC单/双比特错误的软件可读状态,以及错误的RAM地址和数据位等相关信息

- 内存奇偶校验

奇偶校验是一种在内存寄存器中提供防止单比特错误的机制,无论是永久性的还是暂时性的(软错误)。在受保护的内存寄存器中检测到的奇偶校验错误将导致断言一个事件,以指示检测到错误,并将识别错误位置的信息记录下来,供软件在诊断中使用。共享模块接口(称为ECC聚合器)为系统集成商提供了访问错误检测状态和日志信息的权限

- MMU

MMU (Memory Management

Unit)对内存访问应用属性,将虚拟地址重新映射为物理地址,并根据配置拒绝对某些区域的访问。如果CPU由于错误计算了一个地址,并且该地址访问了一个由于MMU编程而被阻塞的区域,则MMU通过识别错误的地址提供诊断覆盖

- MPU

MMU逻辑可用于在设备内存中提供软件任务的空间分离。期望操作系统控制MMU,并根据每个任务的需要更改MMU的设置。违反配置的内存保护策略将导致CPU中止。

MMU还可以配置内存系统的内存排序策略。默认情况下,所有外设访问都是强排序的——这意味着所有按顺序完成的事务都被发出,没有写事务被缓冲。如果需要,操作系统可以将访问配置为设备-

这意味着写入是缓冲的。这可以提高强有序模型的性能,但代价是一定的确定性。强烈建议将系统模块和其他被认为具有关键配置的模块设置为强有序访问模型。

LBIST自检控制器(Self-Test Controller, STC)诊断在MMU执行CPU测试时提供对MMU的检查

- 软件测试和按需软件功能测试,包括I/O检查

软件测试可以用来测试基本功能,以及注入诊断错误和检查正确的错误响应。这样的测试可以在启动时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义。

通用输入/输出(GPIO)模块不支持不同的I/O环回模式。但是,可以使用正常功能支持I/O检查。要做到这一点,软件生成输出,读取并检查输入寄存器中的相同值。这实现了类似于其他模块中的模拟环回的功能。为了获得最佳结果,GPIO功能的任何测试都应该包括I/O环回。

MCAN模块不支持不同的I/O环回模式。但是,可以使用正常功能支持I/O检查

- 使用PMU在线分析

A72 CPU包含一个PMU (performance monitoring

unit)。此逻辑旨在用于调试和代码分析目的,但它也可以用作安全机制。PMU包括一个CPU周期计数器以及三个额外的计数器,可以编程来计算许多不同的CPU事件。

可以监控的CPU事件示例包括:

•CPU诊断检测到ECC或奇偶校验错误的周期数

•CPU处于活锁状态的周期数

•执行的指令数

•异常发生的周期数

有了这些信息,就可以生成一个软件例程,定期检查PMU计数器的值,并将这些值与正常操作期间期望的配置文件进行比较。PMU默认不使能,必须通过软件配置。可以通过执行LBIST诊断来检查PMU诊断。使用PMU进行在线诊断分析是可选的

- PCIe高级错误报告

为了确保数据路径能够正确传输数据,软件可以在远端实现一组参考数据,并对已知的参考数据执行带比较的读操作。必要的软件需求由系统集成商实现的软件定义

- 周期性回读静态寄存器

软件应该定期读取MMA中的静态配置寄存器,并与参考值进行比较,以确保检测到导致预期奇偶校验值的损坏

- 定时重初始化

软件应该定期重新初始化MMA,以确保错误不会在未受保护的状态元素中积累

- 软件定时回读PHY寄存器

PHY中寄存器的定期回读可以提供诊断,以确定PHY是否在接收的数据中看到y位错误

- 软件定期检查邮箱状态

当一个FIFO非满或非空中断应该触发,但不是由于故障,这可以通过独立的软件以固定的间隔读回邮箱状态来检测,例如,如果在一段固定的时间后,软件读取它正在使用的邮箱的状态,发现它是满的,但非空中断没有触发。本质上是邮箱上的软件看门狗。错误响应、诊断可测试性和任何必要的附加软件需求都由系统集成商实现的软件定义

- 软件周期性读取中断源状态寄存器

主机定期读取中断源模块的状态寄存器可以提供诊断,以确保没有未在主机端作为中断接收的中断状态处于挂起状态。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商实现的软件定义

- 周期性软件回读配置寄存器(遥控器/相机)

配置寄存器的定期回读可以为这些寄存器的无意写入或干扰提供诊断。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商实现的软件定义

- MMR写保护机制软件周期测试

软件测试可以用来测试内部逻辑的基本功能,以防止无意的MMR值更新。这包括违反LOCK-

UNLOCK序列和利用CLAIM/信号量功能来限制对特定SOC主机的写更新。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商实现的软件定义。建议使用配置寄存器的回读机制

- 软件定时触发和检查中断

软件测试可以作为诊断来实现,以检测错过的或无意的中断。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商实现的软件定义

- 图像渲染后检查

在使用显示引擎进行最终构图和显示之前,软件可以对绘制的图像进行检查(CRC,图像分析)

- 程序序列监控

程序序列监控(时间和逻辑)是ISO 26262- 5:18 18附件D和IEC 61508-7附件a中描述的软件方法,具体实现由系统集成商确定。

许多应用程序通过代码都知道预期的执行路径。在执行代码时,将构造所取路径的记录,并将其与软件循环执行结束时的期望值(或一组合法值)进行比较。例如,软件可以跟踪循环迭代的次数或调用了哪些子函数。

该诊断的有效性高度依赖于应用程序和诊断实现。有效性可以通过使用软件仪器测试来评估。软件可能通过使用软件来代理影响软件执行中任意数量的中间步骤的硬件错误而造成不匹配。例如,软件可能有意跳过预期的函数调用,并证明程序序列监视捕获了错误

- PWM跳闸检测

PWM模块具有跳闸/安全状态。软件可以根据pr_pwm_pwm_trip_in(其中k = 0 ~ 2, n = 0 ~

3)的输入来配置PWM块进入该Trip/Safe状态的条件。有几个PRU_ICSSG CFG

MMRs允许软件定制什么被认为是PWM跳闸条件。用户必须为他们的用例确定适当的配置

- 读写字节监控

PDMA保持已写入字节数的运行计数,当读取字节时,软件可以依次减少字节数。虽然软件不能知道实时预期的字节数,但它可以大致知道给定预期通信的预期数据量,并且能够确定是否比预期传输了更多或更少的字节,或者是否丢失或未传输预期的字节

- 软件的互反比较

软件对等比较是ISO 26262-5:2018附件D和IEC 61508-7附件a中描述的软件方法,其具体实施由系统集成商确定。

两个独立的内核交换和比较数据。如果发生不匹配,软件将采取缓解措施或发出故障检测状态的信号。

该诊断的有效性高度依赖于应用程序和诊断实现。有效性可以通过使用软件仪器测试来评估。软件可能通过使用软件来代理影响软件执行中任意数量的中间步骤的硬件错误而造成不匹配。例如,软件可能故意将两个不正确的数字相加,以模拟CPU加法器中的错误,并演示比较代码捕获错误

- ECC/CRC错误远程检测和纠错

远程设备可以检测到DSI

TX是否通过应用于报头的ECC和/或在有效负载上计算的CRC发送了一个畸形的DSI数据包。检测到畸形数据包时,系统软件应该运行整体诊断程序和/或进行系统重置。诊断重置后的诊断传输可用于清除由于已检测到的瞬态故障引起的任何问题

- 运行时PBIST检查内存

PBIST逻辑支持一组非常小的指令,允许用户进行内存测试。主要假设是,可以将PBIST完全或部分初始化为任何状态,然后启用它来执行一小组指令。目前它最多可以容纳16条指令。这对于我们目前正在进行的大多数测试来说已经足够了。配置PBIST逻辑可分为两个步骤。第一步是通过参数设置软RTL的最大硬件需求。这里定义了条目数、最大管道延迟等参数。第二步涉及编程特定于ram的需求和内存测试算法。此测试基于用户软件触发器按需完成

328-423 软件相关机制

- 软件检查设备配置完整性

应用软件初始启动后,在系统从安全状态释放之前,应用软件需要对设备配置进行全面检查,以确认设备配置状态是运行安全功能的预期配置。

- 软件控制对同一数据多次读取

信息传递两次及以上并进行比较。这是传输冗余仅用于检测瞬态故障。错误响应、诊断科测试性和软件需求都由系统集成商定义

- 软件控制对同一数据多次读/写

通过软件进行传输冗余,作为存储在内存中信息模块进行额外的运行时诊断。错误响应、诊断科测试性和软件需求都由系统集成商定义

- 软件多样化冗余

创建两个冗余的软件实现,每个实现使用不同的软件路径或算法。这些软件输出相互比较,在不匹配的情况下,软件采取缓解措施或发出故障检测状态的信号。

该诊断的有效性高度依赖于应用程序和诊断实现。有效性可以通过使用软件仪器测试来评估。软件可能通过使用软件来代理影响软件执行中任意数量的中间步骤的硬件错误而造成不匹配。例如,软件可能故意将两个不正确的数字相加,以模拟CPU加法器中的错误,并演示比较代码捕获错误

- 软件冻结帧检测

DSS可配置多个帧周期内处理相同的帧数据,这将触发硬件冻结帧检测事件。DSS还可以为连续的帧处理不同的帧数据进行配置,这不会触发硬件冻结帧检测事件。错误响应、诊断科测试性和软件需求都由系统集成商定义

-

软件HPD事件中断服务

-

软件中断生成检查

对硬件中断生成进行周期性或启动检查,确保中断事件到CPU的路径完整性。软件可以使能/不使能屏蔽,设置/清楚中断事件并检查正确的中断生成和DP状态报告

-

DMPAC事件的软件监控

-

DMPAC UTC通道TR完成软件监控

-

软件监控事件事件的准确性

-

软件监控硬件状态

TX/RX调试/状态寄存器提供有关PDMA操作的信息。通过软件监测这些信息可以提供PDMA工作状态的指示。在PDMA成为卡住的情况下,软件负责重置PDMA通道以恢复操作。错误响应和任何必要的软件需求由系统集成商定义

-

软件监控VPAC事件

-

软件监控VPAC UTC通道TR的完成

-

软件处理一帧内或帧间的像素

-

执行软件进度跟踪

在启动过程的执行中,启动软件跟踪执行的顺序和进度

- 时钟门控或复位转换的软件回读(包含超时 )

在时钟门控事件或复位转换之后,软件应该回读PSC的状态,以确保它已达到所需的状态。建议对该测试设置一个超时时间

- 网络接口上的数据进行软件回读

可以通过软件测试回读MDMA和CFG端口传输的数据。这些数据附带的纠错检查将能够检测到原始数据中的意外变化。必要的软件需求由系统集成商实现的软件定义

- 内存中已知数据的软件回读(即JEDEC设备ID )

通过从内存中读取已知数据(如JEDEC设备ID),可以利用软件测试来检查相关内存设备的基本可访问性

- 传输数据的软件回读

信息在写入后被回读,并与原始数据进行比较。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商定义

- 写配置的软件回读

为了确保模块中内存映射控制寄存器的正确配置,强烈建议软件实现一个测试,以确认所有控制寄存器写入的正确操作。为了支持此软件测试,强烈建议使用CPU的内存保护单元(MPU)或内存管理单元(MMU)将目标内存空间配置为CPU的强有序、不可缓冲的内存区域。这确保了在开始回读之前,寄存器的写操作已经完成

- 通过应用程序CPU对写配置的软件回读

为了确保模块中内存映射控制寄存器的正确配置,强烈建议软件实现一个测试,以确认所有控制寄存器写入的正确操作。为了支持此软件测试,强烈建议使用CPU的内存保护单元(MPU)或内存管理单元(MMU)将目标内存空间配置为CPU的强有序、不可缓冲的内存区域。这确保了在开始回读之前,寄存器的写操作已经完成

Ø强有序不可缓冲的内存区域:a strongly ordered,non-bufferable memory region

vMPU可以配置保护 16个内存区域 ,每个区域都是 独立配置 ,每个区域还配置为 8个子区域 ,

通过寄存器对应的Bit使能 。

v 配置MPU的目的是使用cache

,第一部分是配置MPU的内存地址,第二部分是配置Cache的读写规则,第三部分设置保护规则。内部SRAM的AXI SRAM块。

P.S.

这里要考虑cache本身的特性,计算机中所有的指令和数据都是从存储器中取出来执行的,因此存储器的容量和性能应当随着处理器的速度和性能的提高而提高,从而保持系统性能的平衡。cache的特性是容量小速度快,由快速的SRAM组成。在CPU和主存之间设置cache。

ARM memory type分为 Device Type Memory 和 Normal type memory

Normal type memory分为:

1. Non-cacheable Non bufferable,是 AXI的Memory类型

,该类型可以看出是不能cache缓存和allocate数据的,并且写响应要从最终节点返回

2. Non-cacheable

Bufferable,该种类型是不能被cache缓存和allocate数据的,但写响应可以从中间节点(如POC或POS)返回的

3. Non-snoopable WriteBack No-

allocate,这种类型不是Snoopable属性,但支持cache缓存数据的,不支持allocate,在写数据发生cache

miss下,直接将数据写到下游去,不需要allocate到本级cache

4. Non-snoopable WriteBack

Allocate,这种类型不是Snoopable属性,但支持cache缓存数据的,且也允许allocate数据,在写数据发生cache

miss下,需要将下游数据读到本级cache中,然后再往cache中写入该数据

5. Snoopable WriteBack No-

allocate,支持Snoopable,且支持cache缓存数据的,不支持allocate,在写数据发生cache

miss下,直接将数据写到下游去,不需要allocate到本级cache

6. Snoopable WriteBack

Allocate,支持Snoopable,且支持cache缓存数据的,且也允许allocate数据,在写数据发生cache

miss下,需要将下游数据读到本级cache中,然后再往cache中写入该数据

- 通过DMSC对写配置的软件回读

同上

- 写入数据的软件回读

为了确保数据被正确地写入内存的关键部分,软件可以实现关键内存的回读,并与最初写入的数据进行比较。必要的软件需求由系统集成商实现的软件定义

- 软件在写操作后立即回读数据

同上

- 软件回读电源状态转换(包含超时)

电源状态转换后,软件应该回读PSC的状态,以确保它已达到所需的状态。建议对该测试设置一个超时时间

- 软件刷新 查找表 内存每个帧

这是一种故障避免机制,软件在每帧结束时刷新查找表内存(如VSYNC中断-

VSYNC_IRQ所示)。如果在帧的末尾进行,这样的操作不会干扰DSS的正常功能操作。此操作将删除那些内存中发生的任何比特位单位损坏,以避免将错误传播到连续的输出图像中

- 软件刷新MMR寄存器每帧(通过影子工作机制)

这是一种故障避免机制,软件刷新MMR寄存器每帧。由于DSS

MMR寄存器有一个在每帧结束时同步的影子和工作副本,这样的刷新可以无缝地发生,不会干扰DSS的正常功能操作。此操作将删除这些寄存器中发生的任何损坏

补充:MMR是DSP中的,存储器映射寄存器

-

对相同的读数据软件重新触发ELM

-

软件ROM校验和

ROM内容包括一个已知的校验和,并且可以完成ROM的校验和,以验证ROM的内容没有被损坏

- 软件签名检查

软件可以提供与硬件签名逻辑创建的签名匹配的参考签名,以及与硬件签名逻辑不匹配的修改签名,以测试硬件签名逻辑。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商定义

- 软件自检

软件应该从MMA库中运行自检。此测试会返回一个通过或者失败。

- 软件执行AES重复检测

AES加密算法

- 软件检测基本功能,包括错误测试

软件测试可以用来测试基本功能,以及注入诊断错误和检查正确的错误响应。这样的测试可以在启动boot时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义

此软件测试可以用来检测GPU(图形处理单元)的基本功能,例如注入故障和正确的故障响应。此测试使用参考图像,并检查参考输出图像和执行的时间窗口。此测试可以启动时执行或周期性执行。

- 软件测试基本功能

同上

-

MSMC基础功能用软件测试

-

使用数字I/O回环的基本功能软件测试

软件测试基本功能、注入故障、正确的故障响应。可以在启动时执行或周期性执行,软件需求由软件集成商实现的软件定义

- 使用外部闪存执行基本功能的软件测试

软件通过向外部闪存flash的选定区域写入数据并从这些区域中读取数据来测试基础功能。可以在启动时执行或周期性执行,软件需求由软件集成商实现的软件定义

- 使 用外部闪存和SRAM进行基础功能的软件测试

同上

- 使用外部回环包括ping到远程节点来进行基础功能的软件测试

同上

- 使用外部内存memory执行基础功能的软件测试

同上

通用内存控制器GPMC包括测试控制器的ECC逻辑的功能、相关的错误定位模块ELM(error location module)

- 使用内部数字回环执行软件测试的基本功能

同上

- 总线奇偶校验软件测试

对校验保护机制进行初始化或周期性检测,通过在奇偶校验输入中注入故障到核心,以确保校验错误能够被正确检测。未能接收预期的中断表明在奇偶校验中存在问题,可能需要客户端系统软件运行整体的诊断步骤或一个系统重置reset

- CRC软件测试

对操作模式通过软件进行一个CRC基本功能测试(包括错误中断的生成)。故障可以插入到正在执行CRC检测的信息模块中,也可以插入到提供给PSA签名寄存器的签名中。

- CSI协议软件测试

可以通过软件测试CSI协议检查

- 软件测试DCC运行

DCC双时钟比较器的基本功能测试通过软件编译一系列好的和坏的预期时钟比率,并用软件执行DCC操作来确认预期结果

- DRAM ECC的软件测试

DDR控制器支持基于软件的方法在写入DRAM的数据上注入错误。这可以用于在特定数据位上注入错误,以测试DDR控制器的ECC功能

- 软件测试DSI协议故障检查

在DSI TX

IP中,像素接口协议错误检查器可以在系统中进行如下测试:编程配置IP为标称模式;恢复操作;以不同于编程配置的格式提供视频数据。例如,编程为800x600

RGB888,发送640x480

RGB565,反之亦然。这应该在初始化时执行,以检测先前存在的错误,然后周期性检测新的卡滞错误。对于瞬态故障,由于检测间隔时间较长,很难检测到持续时间较短的瞬态事件,因此该机制不适用于瞬态故障检测

- 软件测试DSI协议 ECC/CRC

ECC或CRC的故障可以通过外部测试功能来测试内部ECC/CRC诊断度量(D1012)是否功能正常。例如,故障可以通过测试功能注入,从显示外设通过LPDT-

RX数据路径通信返回DSI,或者通过在DPHY和DSI控制器之间的LP接收路径中包含一个小型测试功能模块

- 软件测试ECC逻辑

可以通过将ECC故障强制输入内存的数据输出来测试ECC检测逻辑的功能,并查看ECC检测逻辑是否报告故障。共享模块接口(称为ECC聚合器)为系统集成商提供了配置逻辑和强制故障的权限。报告强制故障使用与报告非强制故障相同的机制

- 软件测试ECC-奇偶校验逻辑

同上,ECC故障输入被保护的总线

-

软件功能测试

-

使用回环软件功能测试

该测试可以识别固定故障stuck-at falut,在UFS设备进行读/写操作之前触发。软件需求由系统集成商实现的软件定义

- 使用I/O回环软件功能测试

外设的模拟回环测试导致信号遍历I/O引脚多路复用逻辑到I/O

pad,并提供I/O引脚多路复用的诊断覆盖。模拟回环测试信号路径从模块到输出驱动被禁用的I/O单元。复位时不启用I/O环回。软件是配置和执行诊断所必需的。错误响应由软件管理

- 使 用从属设备软件功能测试

为了检测各种固定故障,在目标应用程序系统中FTTI时间间隔内周期性触发此测试。错误响应、软件需求等由系统集成商定义

- 对远端通信进行软件功能测试

建立软件测试信息方案,通过与远端(主机到设备或设备到主机)的通信来测试基本功能。成功接收并确认返回近端提供连接检查。此测试可以在启动时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义。

- 软件测试 GIC功能,包括故障检测

此测试可以在启动时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义。

- 硬件事务超时监控器的软件测试

通过对接口超时机制进行初始化或周期性测试,以及设置一个低值并期望从诊断中得到结果中断。这允许使用短时超时测试超时函数,以确保预期的中断发生

-

非法操作进和指令捕获的软件测试,包括错误测试

-

内部逻辑奇偶校验软件测试

通过将故障强制注入被保护的总线,并查看检测逻辑是否报告故障,来测试奇偶检测逻辑的功能。共享模块接口(称为ECC聚合器)为系统集成商提供了配置逻辑和强制故障的权限。报告强制故障与报告非强制故障使用相同的机制

- 内存 ECC软件测试

同上

- 内部硬件诊断软件测试

软件可以在SRAM或AXI和APB接口中注入故障,并可以指导ECC是否能够检测到这些故障或超时是否已经真正发生。必要的软件需求由系统集成商实现的软件定义

- 软件测试中断

中断可以使用软件来测试,以引起中断条件。此测试可以在启动时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义。

- 软件测试内存

内存可以使用软件测试技术进行测试,例如棋盘模式。错误响应、软件需求等由系统集成商定义

- 内存奇偶校验软件测试

作为诊断测试,可以通过将奇偶错误强制注入数据或奇偶RAM来测试奇偶错误检测逻辑的功能,并查看奇偶错误检测逻辑是否报告错误。(基于ECC聚合器的实现)

- 内存奇偶校验和 ECC软件测试

通过强制一个Bit位错误注入数据,从内存输出并查看奇偶校验和ECC检测逻辑是否报告故障。共享模块接口(称为ECC聚合器)为系统集成商提供了配置逻辑和强制故障的权限。报告强制故障与报告非强制故障使用相同的机制

-

MMR奇偶校验软件测试

-

软件测试MMR时间戳和断电灰码值

-

软件测试MMU功能,包括错误测试

-

软件测试MPU功能,包括故障测试

软件测试可以用来测试内存保护单元MPU的基本功能以及注入故障和检查正确的故障响应。此测试可以在启动时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义。

- 软件测试多相ECC

通过将故障强制注入被保护的总线,并查看检测逻辑是否报告故障,来测试奇偶检测逻辑的功能。共享模块接口(称为ECC聚合器)为系统集成商提供了配置逻辑和强制故障的权限。报告强制故障与报告非强制故障使用相同的机制

- 软件测试-PBIST

通过选择一个可能失败的算法来配置PBIST逻辑,并查看此情况下PBIST逻辑是否报告故障。例如在只读内存上进行读写测试,以确保报告故障。另一种方案是对具有比目标内存中实际存在的更多Bit位的内存运行测试

- 软件测试-PHY接口I/O回环

BIST模式可以通过配置回环模式对CPSW PHY进行传输和检查。回环配置在IO pad或IO缓冲区之前。此测试可以在启动时执行,也可以周期性执行

- 软件测试-像素接口协议故障检查

在CSI2TX

IP中,像素接口协议错误检查器可以在系统中进行如下测试:编程将IP配置为标称模式;恢复操作;以不同于已编程配置的格式提供像素数据。例如,程序为800x600

RAW12和发送400x300

RAW8。这应该在初始化时执行,以检测先前存在的错误,然后定期检测新的卡在错误上。对于暂态故障,由于检测间隔时间较长,很难检测到持续时间较短的暂态事件,因此该机制不适用于暂态故障检测

-

软件测试-PMU监视器

-

软件测试-POK监视器

软件可以通过调整监测阈值来测试POK功能,监测阈值低于被监测的电压水平,以模拟欠压状态或高于过压状态

- 软件测试-正交quadrature看门狗功能

软件测试可用于测试正交看门狗的基本功能,以及注入诊断错误和检查正确的错误响应。此测试可以在启动时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义。

- 软件测试-状态奇偶校验

通过将故障强制注入被保护的总线,并查看检测逻辑是否报告故障,来测试奇偶检测逻辑的功能。共享模块接口(称为ECC聚合器)为系统集成商提供了配置逻辑和强制故障的权限。报告强制故障与报告非强制故障使用相同的机制

- 软件测试-流引擎故障监视

软件测试可以用来检测流引擎中的错误。此测试可以在启动时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义。

-

软件测试-SYNCLOST

-

软件超时检测

通过对接口超时机制进行初始化或周期性测试,以及设置一个低值并期望从诊断中得到结果中断。这允许使用短时超时测试超时函数,以确保预期的中断发生。未能接收到预期的中断表明超时诊断有问题,需要客户端系统软件运行整个诊断过程或进行系统重置(复位)。诊断重置后的诊断传输用于清楚由于检测到瞬态故障引起的任何问题。

- 软件测试-TS功能包括故障测试

软件测试可以用来测试TS功能的基本功能,以及注入错误和检查正确的错误响应。此测试可以在启动时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义。

- 软件测试-USB2 PHY BIST模式

USB 2.0 PHY支持BIST测试,包括TX到RX的环回和比较。可以使用PHY_TEST包装器MMR配置和运行PHY

BIST。运行BIST时,PHY传输各种字节的数据,并在内部将数据循环回传给RX逻辑。然后,它将接收到的数据与传输的数据进行比较,如果存在不匹配,则指出错误

-

软件测试- VIM 功能包括故障测试

-

软件测试 -可写配置寄存器

为了验证IP的可写配置/控制寄存器的状态,这些寄存器的检查程序应该作为启动测试来实现。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商定义

- 软件看门狗{SOF/EOF/SOL/EOL}在{CSI_IN,VP_OUT,DMA_OUT}的使用

CSI提供发生在数据流指定位置的系统事件(帧开始(SOF)、帧结束(EOF)、行开始(SOL)和行结束(EOL))。这些事件可以在管道中的不同点(CSI_IN、VP_OUT、DMA_OUT)提供。由于视频系统以帧速率工作,这些事件的预期时间可以由软件监控。错误响应、诊断可测试性和任何必要的软件需求都由系统集成商定义。

- 软件测试-回写管道

用于诊断回写管道(DSS13)的测试。当video_lite# 4不被任何活动显示器使用时,回写管道可以连接到video_lite#

4视频管道,并且可以编程为将一帧写入存储器。这被称为回写管道的内存到内存操作模式。然后,软件可以周期性地通过video_#

4发送一帧,通过回写管道将其写回内存,然后比较这两帧是否存在操作中引入的任何错误

- 栈底溢出检测

软件测试可以用来检测堆栈溢出。这样的测试可以在启动时执行,也可以周期性执行。必要的软件需求由系统集成商实现的软件定义

- VBLANK期间DSC自检测试

系统软件使用Self Check Test寄存器(ASF_SELF_CHK_TEST)来损坏Self

Check期望的CRC值(每个CRC位都可以单独损坏)。不可纠正中断“asf_int_uncorr”预计会上升。这个测试需要在编码器对帧进行编码时运行。执行此测试不会导致DSC编码器输出上的损坏。因为这个测试在2帧之间运行,反应时间小于2帧时间

- 测试中断消息

可以对硬件中断生成进行定期和/或启动检查,以确保中断事件到CPU的路径完整性。软件可以启用/禁用掩码,设置/清除中断事件,并检查适当的中断生成和状态报告

- CAN时间戳一致性检查

MCAN实现了接收和发送消息的时间戳。CAN

FD消息需要一个外部时间戳计数器。MCAN提供的时间戳计数器配备了一个预分频器,用于在分辨率和环绕周期之间进行权衡。时间戳计数器值存储在每个发送或接收消息的消息缓冲区中。软件可以对消息执行完整性检查以确定

消息是否按照系统所期望的顺序发送作为诊断。例如,由于CAN协议一次只能携带一条消息,因此不期望具有相同时间戳的多条消息(考虑到环绕时间)。端到端安全(包括消息编号)可用于指示软件可以验证的线性增量时间戳

学习计划安排

我一共划分了六个阶段,但并不是说你得学完全部才能上手工作,对于一些初级岗位,学到第三四个阶段就足矣~

这里我整合并且整理成了一份【282G】的网络安全从零基础入门到进阶资料包,需要的小伙伴可以扫描下方CSDN官方合作二维码免费领取哦,无偿分享!!!

如果你对网络安全入门感兴趣,那么你需要的话可以

点击这里👉网络安全重磅福利:入门&进阶全套282G学习资源包免费分享!

①网络安全学习路线

②上百份渗透测试电子书

③安全攻防357页笔记

④50份安全攻防面试指南

⑤安全红队渗透工具包

⑥HW护网行动经验总结

⑦100个漏洞实战案例

⑧安全大厂内部视频资源

⑨历年CTF夺旗赛题解析

6104

6104

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?