前言

接上一篇《Calibre xRC生成spectre后仿网表流程》,本篇中还是假设主网表中Top cell名称为yyy,三个生成的网表名称分别为"xxx",“xxx.pex”,“xxx.yyy.pxi”,其中"xxx"为主网表。

注意:xxx、yyy等都是大小写敏感的,所以一定不要搞乱了。

另外, 本博客中使用spectre view进行仿真,另一种方式是使用calibre view生成包含寄生的schematic进行后仿(参考这里,建议将该文章中的Device Placement方式更改为Arrayed)。这两种方式的区别是:

- 使用

spectre view会比较麻烦一些,但是在网表较大时这种方式有优势; - 而使用

calibre view对小电路相对而言很方便,但是当电路太大时,calibre view生成schematic的过程会相当慢(我的经验是500多MB的网表用了一个晚上也没有生成成功,后来就选择使用spectre view的方式了)。

生成symbol

如果你有所需仿真的电路的schematic,那么直接从schematic生成symbol即可。如果你没有所需仿真的电路的schematic,那么就手动画一个,只要端口对得上就行了,当然美观一些更好。

因为用Calibre xRC生成的网表中的电路的端口都是大写的,而spectre语法对大小写是敏感的,所以建议将symbol中的端口名都改为大写,这样后面ADE L生成的名为的“input.scs”的网表就可以直接用而不需要手动修改了。

生成spectre view

在Library Manager的View栏中选中刚刚生成的symbol,右键-Copy,将To栏中的View由symbol改为spectre。点击ok完成复制。

编辑CDF

在virtuoso主界面-Tools-CDF-Edit,之后在弹出的Edit CDF界面中选择所需要仿真的"Library Name"和"Cell Name"。

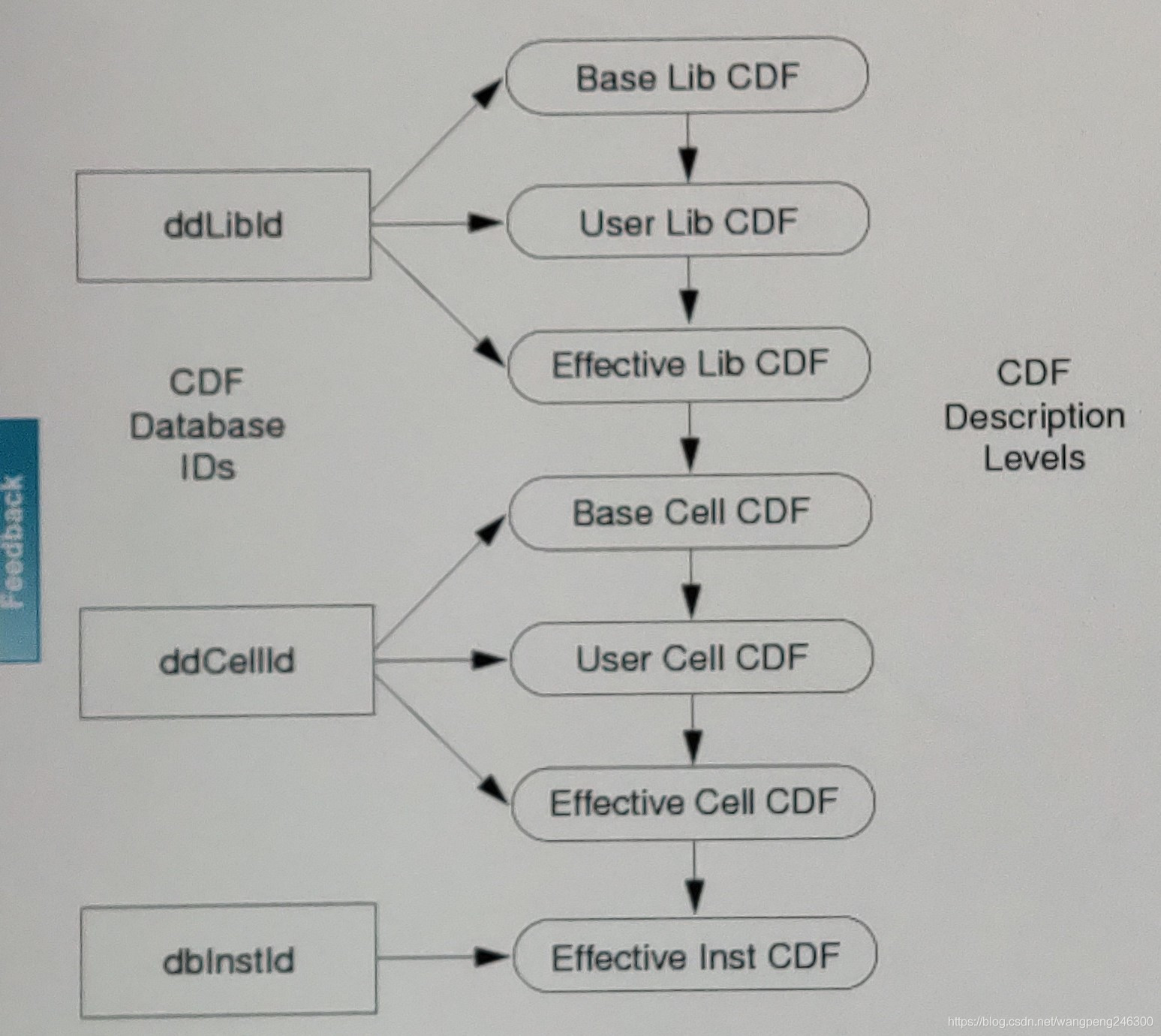

编辑CDF时有3种作用层次(base, user, effective)可选,它们的区别如下,可根据自己的需要选择:

然后在Simulation Infomation栏中将下拉框的值选为spectre,修改"otherParameters"为model;"componentName"为Top Cell名称,假设为yyy;修改"termOrder"为主网表xxx中的端口名称和顺序,每个端口名加上英文双引号,端口之间用空格分开,如果主网表xxx中的端口名中含有转义用的\,也记得将其删除。点击Apply或OK完成。

例如,主网表的内容为:

subckt yyy ( PIN\<1\> PIN\<2\> VDD VSS )

则填入"termOrder"中的内容为:

"PIN<1>" "PIN<2>" "VDD" "VSS"

新建测试schematic

根据自己的需求新建测试用schematic,在此schematic中调用之前复制的spectre view。

并确保新建的schematic中与调用的spectre view各个端口连接的Net Name或者说Wire Name与spectre view中的PIN Name相同。

开始仿真

schematic电路画好之后就可以启动ADE L进行仿真了。

在ADE L-Setup-Model Libraries中添加生成的后仿主网表。

其它的仿真设置根据自己需求选择即可,Enjoy~

如何返回前仿?

- 返回前仿的方法是在

ADE L-Setup-Enviroment选项中将switch view list一栏内schematic的位置更换到最前,即将原来默认的spectre cmos_sch cmos.sch schematic veriloga更改为:schematic spectre cmos_sch cmos.sch veriloga,其它不变。schematic中的spectre view不需要改为symbol view。如果想变回后仿,将switch view list改回默认值即可。 - 另一种比较推荐的切换前后仿的方式是使用

configview,具体方式可以参考这里。

3186

3186

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?