Flexbus 是一种比较灵活的总线,本文将自己的学习心得做个总结。

同事Jicheng在其两篇blog:说说K60的FlexBus外扩SRAM接口电路 和从零入手Kinetis系统开发(十一)之FlexBus模块 对Flexbus做了比较详细的说明,可以先阅读看看。光看还不行,自己实际动手操作感触才会理解的更深刻。

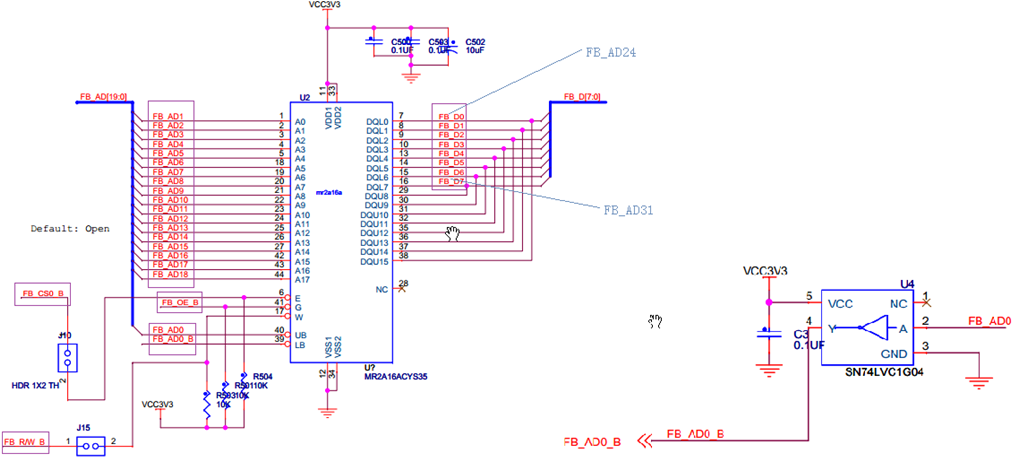

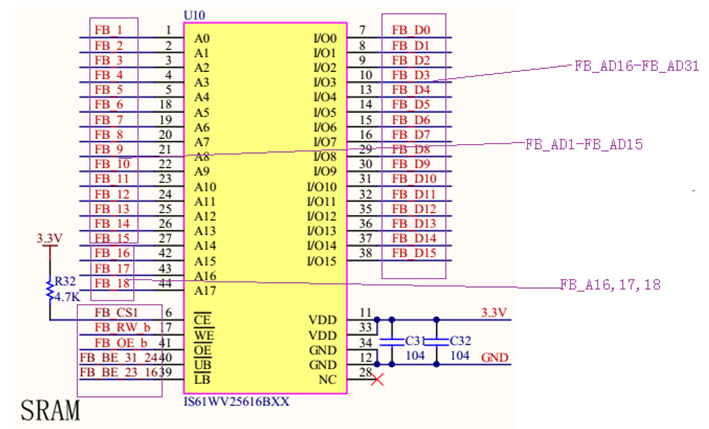

以官方TWR_MEM的原理图为例来分析:

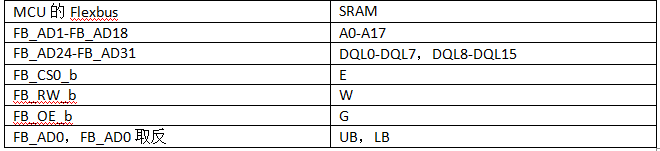

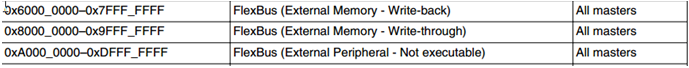

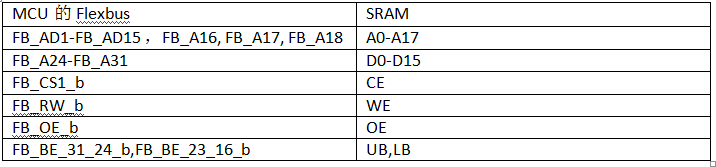

硬件连接如下:

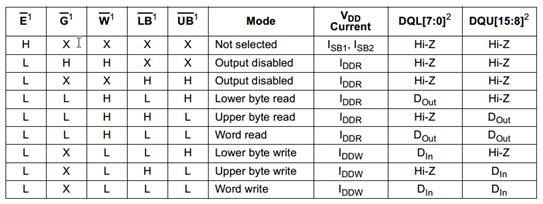

SRAM的真值表如下:

关于硬件上的几点说明:

1)SRAM的A0连接的是FB_AD1,为什么没有和FB_AD0相连接呢?为什么错开了一位?

关于为什么要这么接可以参考这篇博文:http://blog.csdn.net/xiangyuqxq/article/details/7269697

根本原因是因为SRAM的数据总线是16位导致的。

2)这个设计的数据线的高八位是和低八位并连在一起的,只用了8根数据线。这样可以节省8条线。

2)为什么将FB_A0连接到SRAM的UB(Upper byte select),它取反之后的FB_A0_B连接到SRAM的LB(Lower byte select)?

原因是:ARM corte-M4芯片默认是小端存储模式,即低地址存放高字节数据,所以放FB_A0 为0时,访问的高字节数据,当FB_A0为1访问的是低地址数据。

看完硬件,再来分析软件:

1)打开Flexbus的Clock Gate,设置security level

#define OFF_CHIP_ACCESS_ALLOW 3

SIM_MemMapPtr sim = SIM_BASE_PTR;

/* Enable clock to FlexBus module */

sim->SCGC7 |= SIM_SCGC7_FLEXBUS_MASK;

sim->SOPT2 |= SIM_SOPT2_FBSL(OFF_CHIP_ACCESS_ALLOW); // Flexbus security level2)分配好地址线和数据线,控制线

// 地址线 FB_AD1~FB_AD18连接SRAM的A0~A17

PORTD_PCR5 = PORT_PCR_MUX(5); // FB_AD1

PORTD_PCR4 = PORT_PCR_MUX(5); // FB_AD2

PORTD_PCR3 = PORT_PCR_MUX(5); // FB_AD3

PORTD_PCR2 = PORT_PCR_MUX(5); // FB_AD4

PORTC_PCR10 = PORT_PCR_MUX(5); // FB_AD5

PORTC_PCR9 = PORT_PCR_MUX(5); // FB_AD6

PORTC_PCR8 = PORT_PCR_MUX(5); // FB_AD7

PORTC_PCR7 = PORT_PCR_MUX(5); // FB_AD8

PORTC_PCR6 = PORT_PCR_MUX(5); // FB_AD9

PORTC_PCR5 = PORT_PCR_MUX(5); // FB_AD10

PORTC_PCR4 = PORT_PCR_MUX(5); // FB_AD11

PORTC_PCR2 = PORT_PCR_MUX(5); // FB_AD12

PORTC_PCR1 = PORT_PCR_MUX(5); // FB_AD13

PORTC_PCR0 = PORT_PCR_MUX(5); // FB_AD14

PORTB_PCR18 = PORT_PCR_MUX(5); // FB_AD15

PORTB_PCR17 = PORT_PCR_MUX(5); // FB_AD16

PORTB_PCR16 = PORT_PCR_MUX(5); // FB_AD17

PORTB_PCR11 = PORT_PCR_MUX(5); // FB_AD18

// 数据线 FB_AD24~FB_AD31连接SRAM的低八位数据线DQL0~DQL7

PORTC_PCR15 = PORT_PCR_MUX(5); // FB_AD24 used as DQL7

PORTC_PCR14 = PORT_PCR_MUX(5); // FB_AD25 used as DQL6

PORTC_PCR13 = PORT_PCR_MUX(5); // FB_AD26 used as DQL5

PORTC_PCR12 = PORT_PCR_MUX(5); // FB_AD27 used as DQL4

PORTB_PCR23 = PORT_PCR_MUX(5); // FB_AD28 used as DQL3

PORTB_PCR22 = PORT_PCR_MUX(5); // FB_AD29 used as DQL2

PORTB_PCR21 = PORT_PCR_MUX(5); // FB_AD30 used as DQL1

PORTB_PCR20 = PORT_PCR_MUX(5); // FB_AD31 used as DQL0

// 控制线

// PORTC_PCR3 = PORT_PCR_MUX(5); // CLKOUT , FB_CLK optional

PORTD_PCR1 = PORT_PCR_MUX(5); // FB_CS0_b 连接SRAM的 Chip enable端

PORTC_PCR11 = PORT_PCR_MUX(5); // FB_RW_b 连接SRAM的 Write enable端

PORTB_PCR19 = PORT_PCR_MUX(5); // FB_OE_b 连接SRAM的 Output enable端

PORTD_PCR6 = PORT_PCR_MUX(5); // FB_AD0 连接SRAM的 Upper byte select端这里并没有使用PTC3/CLKOUT,因为操作SRAM不需要时钟。

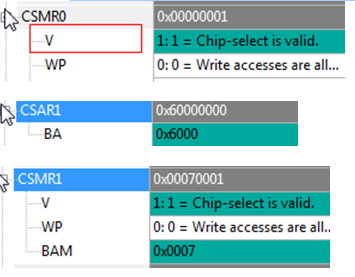

3)设置Flexbus相关的四个寄存器,FB_CSARn,FB_CSMRn,FB_CSCRn,FB_CSPMCR

a).__先把FB_CSMR0的V位置1!!

FB_CSMR0 |= FB_CSMR_V_MASK; // we must set V in FB_CSMRn, because it act as a global CS之后设置的寄存器中的 n取决于实际中用的是哪个CS

b).__设置FB_CSARn中的BA

// Chip select address resgister ,FB_CSARn

FB_CSAR0 = FLEX_BUS_BASE_ADDRESS; // Base AddressFLEX_BUS_BASE_ADDRESS的值为:

#define FLEX_BUS_BASE_ADDRESS 0x60000000c).__设置FB_CSMRn

// Chip select mask register, FB_CSMR0

FB_CSMR0 = FB_CSMR_V_MASK | FB_CSMR_BAM(0) ;

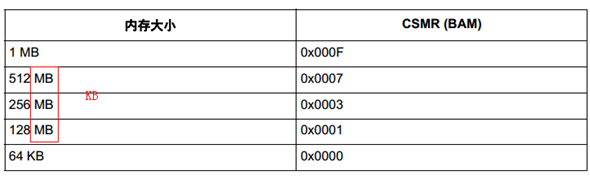

BAM=0x0000 表示0x6000_0000~0x6000_FFFF的64KB范围内都是有效

BAM=0x0001,表示0x6000_0000~0x6001_FFFF的128KB范围内都是有效

BAM=0x0003,表示0x6000_0000~0x6003_FFFF的256KB范围内都是有效

BAM=0x0007,表示0x6000_0000~0x6007_FFFF的512Kb范围内都是有效

BAM=0x0004,表示0x6000_0000~0x6000_FFFF和0x6004_0000~0x6004_FFFF这两个不连续的128KB的空间

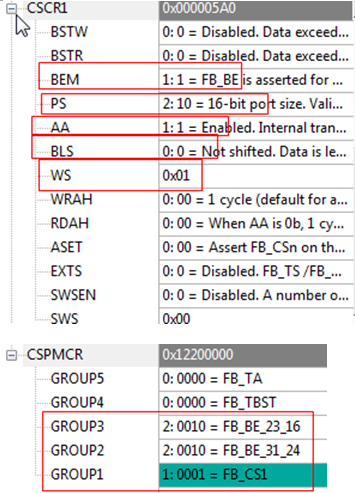

d).__设置FB_CSCRn

FB_CSCR0 = FB_CSCR_PS(1) /* Set port size , 8-bit port*/

| FB_CSCR_AA_MASK /* auto-acknowledge(这位设置很重要,非阻塞,数据传输完成(或者等待n个

waite states)自动终结时钟周期,如果FB_TA不被使能,该位必须置位。) */

// | FB_CSCR_BLS_MASK /* Data is left-aligned on FB_AD,一般就设置为0,这样地址和数据总线不复用 */

/* 8-bit port size ---FB_D[31:24] ,16-bit port size--16-bit port size. */

| FB_CSCR_BEM_MASK /* Byte-Enable Mode */

| FB_CSCR_WS(0x2) /* 2 wait state - may need more wait states depending on the bus speed 1 不行 */

| FB_CSCR_ASET(0x1) /* assert chip select on second clock edge after address is asserted

- may be changed if need */

| FB_CSCR_RDAH(0x0)

| FB_CSCR_WRAH(0x0) ;

这里数据线是8bit,所以PS设置为1,BLS默认是左对齐,就是数据在高位。

e).__设置FB_CSPMCR,这个根据实际使用的flexbus线来设置。

// Chip select port multiplexing control register, 对于本demo可以不做设置,因为没有用到相关的线

FB_CSPMCR = FB_CSPMCR_GROUP1(1) /* FB_CS1 */

| FB_CSPMCR_GROUP2(0) /* FB_CS4 */

| FB_CSPMCR_GROUP3(0) /* FB_CS5 */

| FB_CSPMCR_GROUP4(1) /* FB_CS2 */

| FB_CSPMCR_GROUP5(1) ; /* FB_CS3 */

之后就可以操作SRAM了

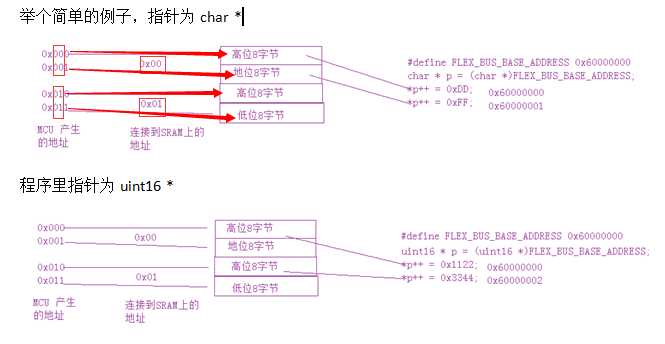

程序里:*address = value,自动产生一定的时序,地址(映射到FB_AD0—FB_AD18)+数据(映射到FB_AD24-FB_AD31),这样就完成了对SRAM的写操作。其实不管程序里指针类型是什么,都可以自动的完成数据的读写。

void main (void)

{

char * p = (char *)FLEX_BUS_BASE_ADDRESS; printf("***********************************************\n");

printf("FLEX BUS test, you need to connect the \n");

printf("TWR-MEM board and add jumper at J15 and J10 \n");

printf("to test the code.\n");

printf("***********************************************\n");

flex_bus_init();

printf("write to SRAM on flex bus, 0x11, 0x22, 0x33, 0x44\n");

*p++ = 0x11;

*p++ = 0x22;

*p++ = 0x33;

*p++ = 0x44;

p = (char *)FLEX_BUS_BASE_ADDRESS;

printf("reading SRAM from flex bus: %x,%x,%x,%x\n", p[0],p[1],p[2],p[3]);

}再附上完整的初始化代码:

void flex_bus_init(void)

{

#define OFF_CHIP_ACCESS_ALLOW 3

SIM_MemMapPtr sim = SIM_BASE_PTR;

/* Enable clock to FlexBus module */

sim->SCGC7 |= SIM_SCGC7_FLEXBUS_MASK;

sim->SOPT2 |= SIM_SOPT2_FBSL(OFF_CHIP_ACCESS_ALLOW); // Flexbus security level

//////////////////////////////////////////////////////////////////////////

// 地址线 FB_AD1~FB_AD18连接SRAM的A0~A17

PORTD_PCR5 = PORT_PCR_MUX(5); // FB_AD1

PORTD_PCR4 = PORT_PCR_MUX(5); // FB_AD2

PORTD_PCR3 = PORT_PCR_MUX(5); // FB_AD3

PORTD_PCR2 = PORT_PCR_MUX(5); // FB_AD4

PORTC_PCR10 = PORT_PCR_MUX(5); // FB_AD5

PORTC_PCR9 = PORT_PCR_MUX(5); // FB_AD6

PORTC_PCR8 = PORT_PCR_MUX(5); // FB_AD7

PORTC_PCR7 = PORT_PCR_MUX(5); // FB_AD8

PORTC_PCR6 = PORT_PCR_MUX(5); // FB_AD9

PORTC_PCR5 = PORT_PCR_MUX(5); // FB_AD10

PORTC_PCR4 = PORT_PCR_MUX(5); // FB_AD11

PORTC_PCR2 = PORT_PCR_MUX(5); // FB_AD12

PORTC_PCR1 = PORT_PCR_MUX(5); // FB_AD13

PORTC_PCR0 = PORT_PCR_MUX(5); // FB_AD14

PORTB_PCR18 = PORT_PCR_MUX(5); // FB_AD15

PORTB_PCR17 = PORT_PCR_MUX(5); // FB_AD16

PORTB_PCR16 = PORT_PCR_MUX(5); // FB_AD17

PORTB_PCR11 = PORT_PCR_MUX(5); // FB_AD18

// 数据线 FB_AD24~FB_AD31连接SRAM的低八位数据线DQL0~DQL7

PORTC_PCR15 = PORT_PCR_MUX(5); // FB_AD24 used as DQL7

PORTC_PCR14 = PORT_PCR_MUX(5); // FB_AD25 used as DQL6

PORTC_PCR13 = PORT_PCR_MUX(5); // FB_AD26 used as DQL5

PORTC_PCR12 = PORT_PCR_MUX(5); // FB_AD27 used as DQL4

PORTB_PCR23 = PORT_PCR_MUX(5); // FB_AD28 used as DQL3

PORTB_PCR22 = PORT_PCR_MUX(5); // FB_AD29 used as DQL2

PORTB_PCR21 = PORT_PCR_MUX(5); // FB_AD30 used as DQL1

PORTB_PCR20 = PORT_PCR_MUX(5); // FB_AD31 used as DQL0

// 控制线

// PORTC_PCR3 = PORT_PCR_MUX(5); // CLKOUT , FB_CLK optional

PORTD_PCR1 = PORT_PCR_MUX(5); // FB_CS0_b 连接SRAM的 Chip enable端

PORTC_PCR11 = PORT_PCR_MUX(5); // FB_RW_b 连接SRAM的 Write enable端

PORTB_PCR19 = PORT_PCR_MUX(5); // FB_OE_b 连接SRAM的 Output enable端

PORTD_PCR6 = PORT_PCR_MUX(5); // FB_AD0 连接SRAM的 Upper byte select端

////////////////////////////////////////////////////////////////////////

// 设置Flexbus相关的四个寄存器 FB_CSARn,FB_CSMRn,FB_CSCRn,FB_CSPMCR,n取决于实际中用的是哪个CS

FB_CSMR0 |= FB_CSMR_V_MASK; // we must set V in FB_CSMRn, because it act as a global CS

// Chip select address resgister ,FB_CSARn

FB_CSAR0 = FLEX_BUS_BASE_ADDRESS; // Base Address

// Chip select mask register, FB_CSMR0

FB_CSMR0 = FB_CSMR_V_MASK | FB_CSMR_BAM(0) ;

FB_CSCR0 = FB_CSCR_PS(1) /* Set port size , 8-bit port*/

| FB_CSCR_AA_MASK /* auto-acknowledge(这位设置很重要,非阻塞,数据传输完成(或者等待n个

waite states)自动终结时钟周期,如果FB_TA不被使能,该位必须置位。) */

// | FB_CSCR_BLS_MASK /* Data is left-aligned on FB_AD,一般就设置为0,这样地址和数据总线不复用 */

/* 8-bit port size ---FB_D[31:24] ,16-bit port size--16-bit port size. */

| FB_CSCR_BEM_MASK /* Byte-Enable Mode */

| FB_CSCR_WS(0x2) /* 2 wait state - may need more wait states depending on the bus speed 1 不行 */

| FB_CSCR_ASET(0x1) /* assert chip select on second clock edge after address is asserted

- may be changed if need */

| FB_CSCR_RDAH(0x0)

| FB_CSCR_WRAH(0x0) ;

// Chip select port multiplexing control register, 对于本demo可以不做设置,因为没有用到相关的线

FB_CSPMCR = FB_CSPMCR_GROUP1(1) /* FB_CS1 */

| FB_CSPMCR_GROUP2(0) /* FB_CS4 */

| FB_CSPMCR_GROUP3(0) /* FB_CS5 */

| FB_CSPMCR_GROUP4(1) /* FB_CS2 */

| FB_CSPMCR_GROUP5(1) ; /* FB_CS3 */

}分析完这个例子,让我们再来看一个用Flexbus 操作SRAM的例子,

原理图如下:

接口如下:

这个接法和第一种接法有以下不同:

1)用到了16位数据线

2)MCU由于FB_AD线不够用,用了FB_A16,A17,A18

关于这个接法的可以参考:http://www.freescaleic.org/module/forum/forum.php?mod=viewthread&tid=589170&extra=page%3D&page=1

这个其实可以这么理解,FB_A16只能用来做地址线,你可能会好奇它和FB_AD16 有什么区别,其实区别就是FB_A16只能做地址线,FB_AD16既可以做地址线也可以做数据线。在这个例子中,其实是把FB_AD1到FB_AD15只用作地址线,相当于非复用模式。

3)这里没用到FB_AD0,所以程序中就没配置它。FB_AD0(PTD6)就可以用作其他功能了。SRAM高低位控制信号接的是Flexbus的FB_BE_31_24_b和FB_BE_23_16_b。

软件流程类似:

void SRAM_Init(void)

{

/* set SRAM pinMux */

SIM->SCGC5 |= (SIM_SCGC5_PORTA_MASK | SIM_SCGC5_PORTB_MASK | SIM_SCGC5_PORTC_MASK | SIM_SCGC5_PORTD_MASK | SIM_SCGC5_PORTE_MASK);

/* flexbus clock output(optional, use for debug) */

PORTC->PCR[3] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_CLKOUT

/*control signals */

PORTB->PCR[19] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_OE

PORTC->PCR[11] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_RW

PORTD->PCR[0] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // CS1

PORTC->PCR[16] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_BE_23_16

PORTC->PCR[17] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_BE_31-24

/* address signal */

PORTD->PCR[10] = PORT_PCR_MUX(6)|PORT_PCR_DSE_MASK; // FB_A18

PORTD->PCR[9] = PORT_PCR_MUX(6)|PORT_PCR_DSE_MASK; // FB_A17

PORTD->PCR[8] = PORT_PCR_MUX(6)|PORT_PCR_DSE_MASK; // FB_A16

PORTB->PCR[18] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A15

PORTC->PCR[0] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A14

PORTC->PCR[1] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A13

PORTC->PCR[2] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A12

PORTC->PCR[4] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A11

PORTC->PCR[5] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A10

PORTC->PCR[6] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A9

PORTC->PCR[7] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A8

PORTC->PCR[8] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A7

PORTC->PCR[9] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A6

PORTC->PCR[10] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A5

PORTD->PCR[2] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A4

PORTD->PCR[3] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A3

PORTD->PCR[4] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A2

PORTD->PCR[5] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_A1

/* data signal */

PORTB->PCR[17] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD16

PORTB->PCR[16] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD17

PORTB->PCR[11] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD18

PORTB->PCR[10] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD19

PORTB->PCR[9] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD20

PORTB->PCR[8] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD21

PORTB->PCR[7] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD22

PORTB->PCR[6] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD23

PORTC->PCR[15] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD24

PORTC->PCR[14] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD25

PORTC->PCR[13] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD26

PORTC->PCR[12] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD27

PORTB->PCR[23] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD28

PORTB->PCR[22] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD29

PORTB->PCR[21] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD30

PORTB->PCR[20] = PORT_PCR_MUX(5)|PORT_PCR_DSE_MASK; // FB_AD31

/* enable flexbus */

FLEXBUS_InitTypeDef FLEXBUS_InitStruct;

FLEXBUS_InitStruct.ADSpaceMask = kFLEXBUS_ADSpace_512KByte; /*内存地址范围512Kb

*/

FLEXBUS_InitStruct.autoAckMode = kFLEXBUS_AutoAckEnable; /*启动自动应答*/

FLEXBUS_InitStruct.CSn = kFLEXBUS_CS1; /*使用CS1片选信号 */

FLEXBUS_InitStruct.dataAlignMode = kFLEXBUS_DataLeftAligned; /*数据左对齐 */

FLEXBUS_InitStruct.dataWidth = kFLEXBUS_PortSize_8Bit; /*数据位宽16位 */

FLEXBUS_InitStruct.baseAddress = SRAM_ADDRESS_BASE; /* 基地址 */

FLEXBUS_InitStruct.ByteEnableMode = kFLEXBUS_BE_AssertedReadWrite; /* 在读写操作的时候都插入位使能型号 */

FLEXBUS_InitStruct.div = 0;

FLEXBUS_Init(&FLEXBUS_InitStruct);

/* config Flexbus SRAM pinmux */

FLEXBUS_PortMuxConfig(kFLEXBUS_CSPMCR_Group3, kFLEXBUS_CSPMCR_GROUP3_BE_23_16);

FLEXBUS_PortMuxConfig(kFLEXBUS_CSPMCR_Group2, kFLEXBUS_CSPMCR_GROUP2_BE_31_24);

FLEXBUS_PortMuxConfig(kFLEXBUS_CSPMCR_Group1, kFLEXBUS_CSPMCR_GROUP1_CS1);

}Flexbus相关的四个寄存器,FB_CSARn,FB_CSMRn,FB_CSCRn,FB_CSPMCR如下:

常见问题:

1)Flexbus上可否挂接多个外设?

答:可以,每个外设接不通的CS,首先得设置好寄存器FB_CSARn,FB_CSMRn,FB_CSCRn,FB_CSPMCR,一个cs对应一个地址范围,然后会根据不同的地址,自动产生相应的时序操作相应的器件。

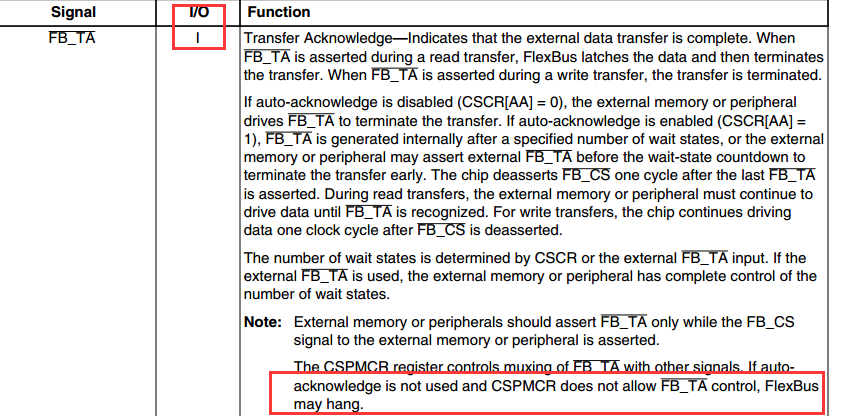

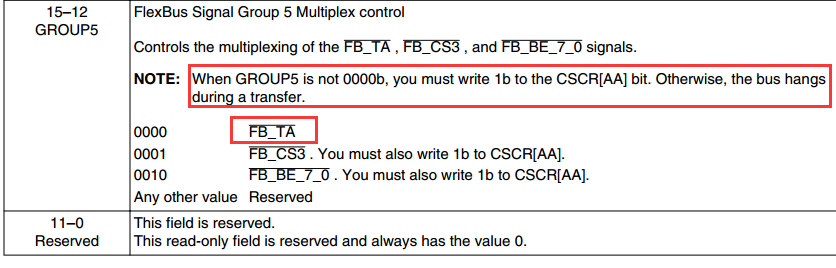

2)FB_CSCR中的AA位到底什么作用?

答:这个会关联到FB_TA信号线,

FB_TA 信号使用与否受FB_CSPMCR的GROUP5决定

可以这么理解,Flexbus通讯过程必须要有应答信号来指示read或者write完成。如果外部器件有这个信号线并且连接到了FB_T上了,这时GROUP5设置的为0,那么AA可以不打开。如果AA也打开,等待FB_CSCR中的WS时间后,产生一个内部的应带信号,如果外部先来应答,那么就提前结束。 如果外部没接应答线,那么AA必须打开,WS的设置很重要。

3)flexbus相关的信号线很多,如果只用其中一部分,其他的信号线会不会也有数据产生?

答:只要软件里没有pinmux使能flexbus功能,就不会有影响。

两个例子的源代码如下链接:http://download.csdn.net/detail/wangwenxue1989/8951969

1404

1404

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?