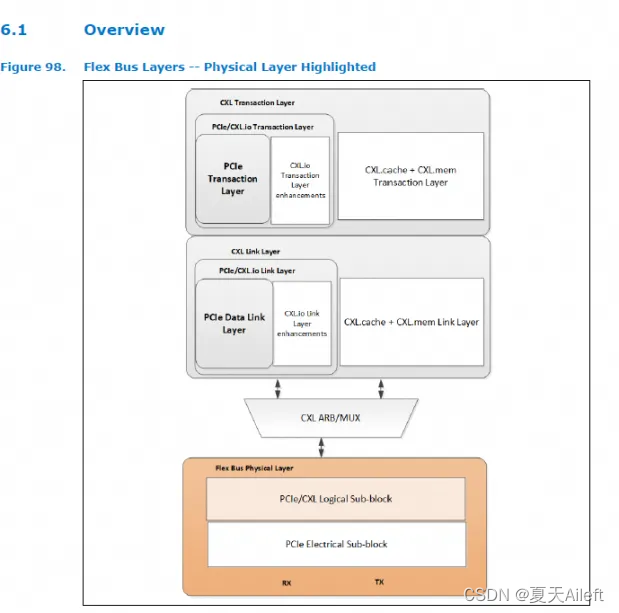

6.1 概览

在传输端,Flex Bus物理层准备从PCIe链路层或CXL ARB/MUX接收的数据,以便通过Flex Bus链路进行传输。在接收端,Flex Bus物理层对Flex Bus链路上接收的数据进行串并转换,并将其转换为适当的格式,以转发到PCIe链路层或ARB/MUX。

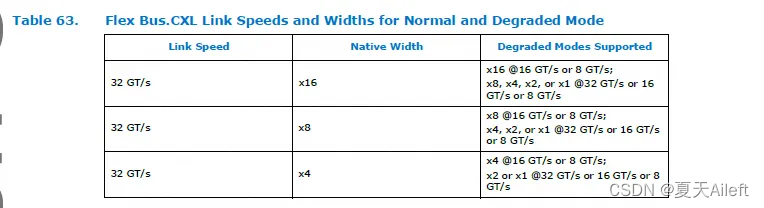

在初始链路训练期间,逻辑PHY在PCIe模式下工作,在训练至2.5 GT/s后,根据备用模式协商的结果,在适当的情况下切换到CXL模式。在CXL模式下,正常操作在本机链路宽度和32 GT/s链路速度下进行。降级运行模式包括8 GT/s或16 GT/s链路速度,和较小的x2和x1链路宽度。下表总结了协议支持的CXL链路宽度和链路速度组合。

6.2 Flex Bus的CXL帧和数据

6.2.1 有序集块和数据块

有序集块(Ordered Set Block)和数据块(Data Block)是PCIe里面的概念。有序集块用于训练、进入和退出电气空闲、转换到数据块,以及时钟容差补偿等,这个放到讲PCIe的时候再说。数据块用于传输从CXL链路层接收的flit。16-bit协议ID字段与从链路层接收到的每个528-bit(512-bit数据负载+16-bit CRC) flit相关联。

6.2.2 Protocol ID[15:0]

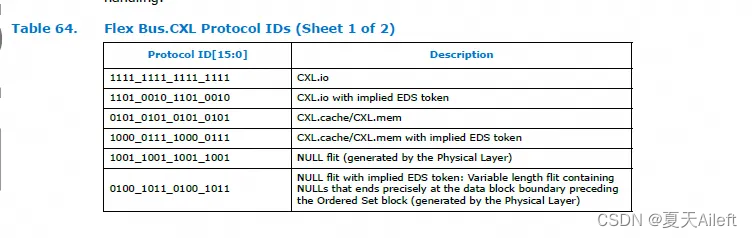

16位协议ID字段指定传输的flit是CXL.io、CXL.cache/CXL.mem还是其他有效负载。

协议ID字段(16位):传输的flit(流控制单元)中的该字段指示所承载的有效负载的类型。 它可以指定 flit 是用于 CXL.io、CXL.cache/CXL.mem 还是任何其他类型的有效负载。 该文档可能提供了有效协议 ID 编码的表。

隐含的 EDS 令牌:某些编码表示有序集块位于当前数据块之后,这由隐含的 EDS 令牌指示。 这只能发生在数据块中的最后一个 flit 中。

NULL Flits:当链路层没有可用的有效 flits 时,这些由物理层插入。 带有隐含 EDS 令牌的 NULL flit 恰好在有序集块之前的数据块边界处结束。 它们的长度可能有所不同,但旨在快速过渡到有序集块。

错误保护:协议 ID 字段的 16 位编码使用两个 8 位编码组,每个编码组的汉明距离为 4,以防止位翻转的错误保护。 如果一组不正确,可以更正; 如果两者都不正确,则会记录一个不可纠正的错误,该 flit 会被丢弃,并且该链路会进行恢复。

意外的协议 ID:物理层负责丢弃具有无效或意外协议 ID 的 flits。 如果由于意外的协议 ID 导致 flit 被丢弃,则会在特定状态寄存器中记录错误。

错误检测和处理:本节参考第 6.2.9 小节,了解有关如何检测和管理与协议 ID 相关的错误的更多详细信息。

当链路层没有有效flit时,物理层插入NULL flit到数据流中。

(Flit 是流控制传输单元(Flow Control Unit)的缩写,它是数据传输中的一个基本单位。在CXL协议中,一个flit是信息传递的最小单元,用于在链路层进行数据传输。

有效flit指的是包含有效负载或者控制信息的flit,即那些需要被传输的实际数据。

当链路层没有有效flit可发送时,意味着没有数据或者控制信息需要在此时刻传输。

物理层插入NULL flit(空flit或者无效flit)到数据流中是指在没有数据需要发送的时刻,物理层会插入一个特定的flit,这个flit不含任何有效的信息或负载。这样做的目的是为了维持链路的同步和稳定,保持链路的活跃状态,并为潜在的流控制和信号完整性提供支持。)

6.2.3 x16数据包

下图显示了x16链接的数据包布局。首先,16-bit传输协议ID被分成两个8-bit,在Lane 0和Lane 1上传输;随后是528-bit flit的传输,同样是按照8-bit粒度拆分。

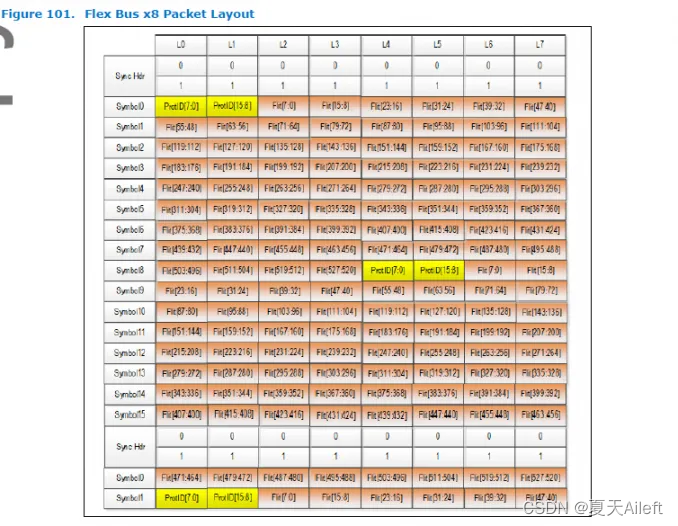

6.2.4 x8数据包

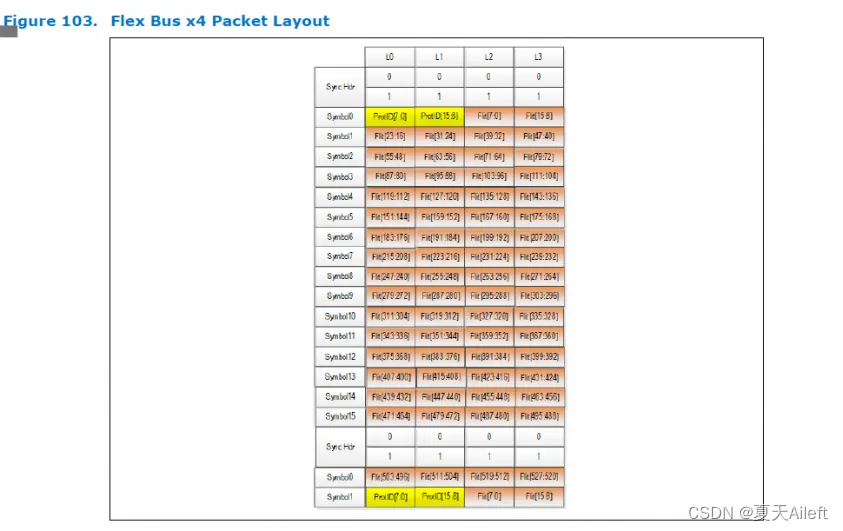

6.2.5 x4数据包

6.2.6 x2数据包

x2数据包布局与x4数据包布局非常相似,协议ID与通道0对齐。16-bit协议ID和528-bit flit以8-bit粒度在两条Lane上传输。

6.2.7 x1数据包

x1数据包布局仅在降级模式下使用。16-bit协议ID后跟528-bit flit在一条Lane上传输。

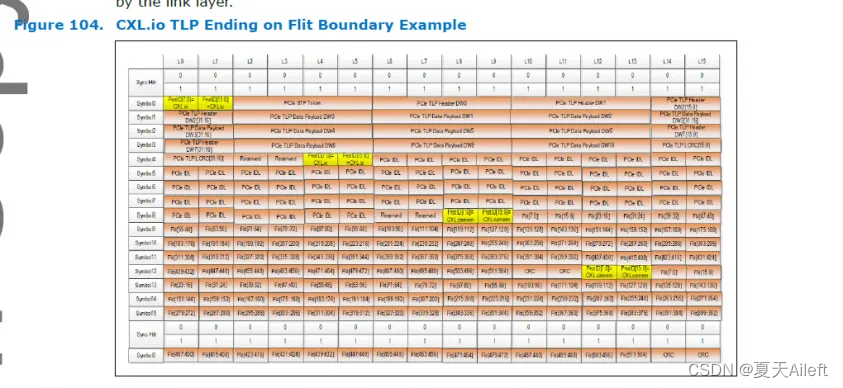

6.2.8 特殊情况:CXL.io – 何时TLP在Flit边界上结束

对于CXL.io,如果TLP在flit边界上结束,且没有额外的CXL.io数据包要发送,但接收端仍然需要随后的EDB(EnD Bad)指示,或IDLE flit,或DLLP,以在处理TLP之前确认此TLP是完好的还是无效的。

下图展示了这种场景,第一个CXL.io flit刚好封装了一个TLP。为保证接收端正确处理,发送端需要在发送一个包含PCIe IDLE令牌的CXL.io flit。

6.2.9 帧错误

物理层负责检测帧错误,并随后启动Recovery以重新训练链路。以下是物理层检测到的帧错误:

● 同步头错误

● 协议ID帧错误

● EDS插入错误

● 528-bit的CXL.io flit中存在PCIe帧错误

协议 ID 帧错误在第 6.2.2 节中进行了描述,并在下面进行了总结表 65. CXL 规范中定义的协议 ID 值是

被视为有效的协议 ID。有效的协议 ID 要么是预期的,要么是意外的。一个预期的协议 ID 是与在期间启用的协议相对应的协议 ID谈判。意外的协议 ID 是与之前的协议相对应的协议 ID。协商期间未启用。协议 ID 的值未在 CXL 中定义规范被认为是无效的协议 ID。每当一个飞行物被丢弃时由于意外的协议 ID 帧错误或不可纠正的协议ID帧错误,物理层进入LTSSM恢复重新训练链路并通知链路层进入恢复状态,如果适用的话,启动链路级重试。

6.3 链路训练

6.3.1 PCIe vs Flex Bus.CXL

当LTSSM从Detect状态退出后,Flex Bus链路开始训练,并根据PCIe LTSSM规则完成链路宽度协商和速度协商。在链路训练期间,下游端口通过PCIe备用模式协商机制启动Flex Bus模式协商。在以2.5 GT/s的速度进入L0之前,完成Flex Bus模式协商。

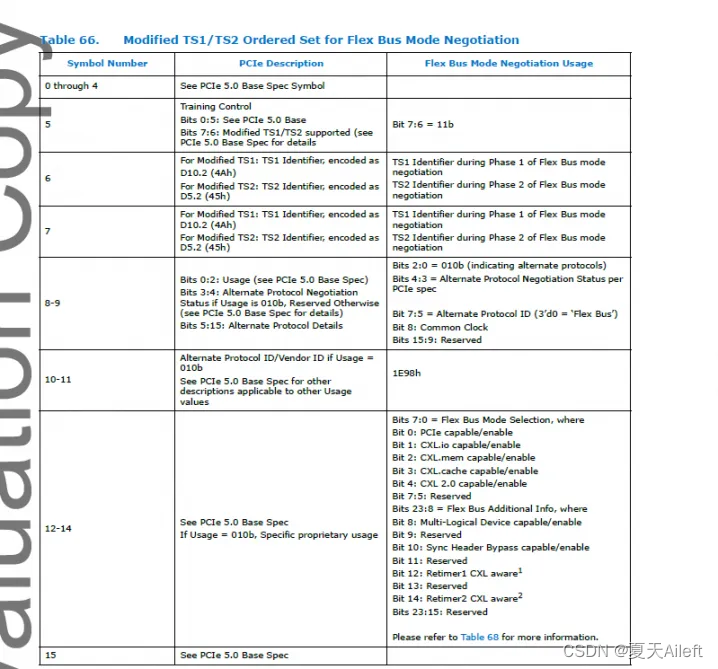

Flex Bus模式的动态硬件协商发生在LTSSM的Configuration状态下的链路训练期间,通过交换PCIe 5.0基本规范定义的Modified TS1和TS2有序集来促进。

6.3.1.1 硬件自主模式协商

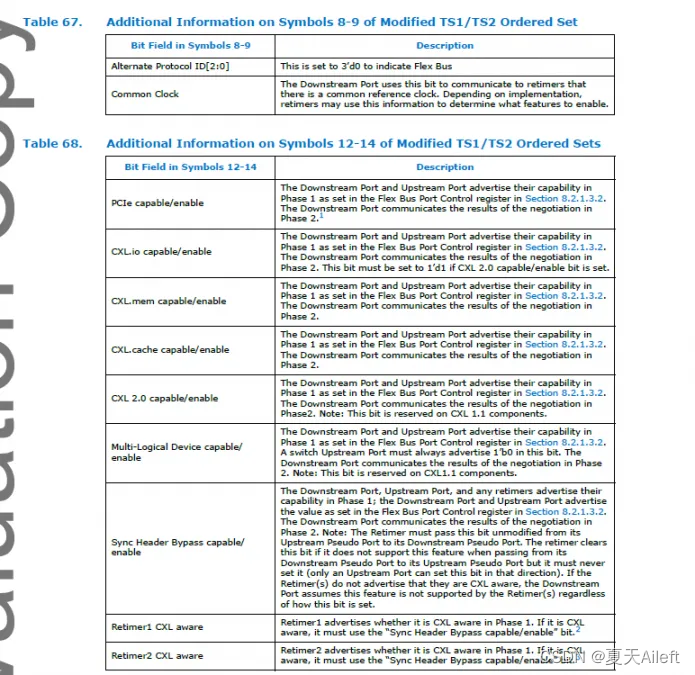

Flex Bus 模式的动态硬件协商发生在链路训练期间使用备用通道以 Gen1 速度进入 L0 之前的 LTSSM 配置状态协议协商机制,通过交换修改后的 TS1 和 TS2 来促进PCIe 5.0 基本规范定义的有序集。 下游端口通过发送 TS1 有序集通告其 Flex 总线来启动协商过程能力。 上游端口根据自身能力响应提案以及主办方宣传的内容。 主办方传达最终决定通过在之前或期间发送修改后的 TS2 有序集来启用的功能配置。完成。请参阅 PCIe 5.0 基本规范,详细了解各个领域如何修改后的 TS1/TS2 OS 已设置。 表 66 显示了如何使用修改后的 TS1/TS2 OS用于 Flex 总线模式协商。 “Flex 总线模式协商使用”专栏描述了适用于 PCIe 基本规范定义的增量Flex 总线模式协商。 表 68 提供了额外的解释。必须将重定时器 1 和重定时器 2 的存在编程到 Flex 总线端口 DVSEC 中在谈判开始前通过软件进行; 如果存在重定时器,则相关的重定时器使用修改后的 TS1/TS2 OS 中的位。

Note:

1.Retimer1相当于PCI Express规范中的Retimer X或Retimer Z

2. Retimer2相当于PCI Express规范中的Retimer Y

NOTES:

- 当下游端口在阶段 2 中传达协商结果时,PCIe 模式和 CXL 模式是互斥的。

- Retimer1相当于PCI Express规范中的Retimer X或Retimer Z

- Retimer2相当于PCI Express规范中的Retimer Y

(在PCIe设备初始化和链接训练过程中,有多个阶段。其中,在阶段 2中,设备或端口会传达它们关于链接速率和模式的协商结果。PCIe模式是传统的PCI Express通信模式,而CXL模式是专为处理器与加速器或内存扩展设备间的通信设计的新模式。互斥意味着在一个给定的链接上,只能使用PCIe模式或CXL模式中的一个,不能同时使用。这是因为两种模式有不同的架构和通信要求,不能共存于同一个链接上。)

6.3.1.3 Flex Bus.CXL 协商,支持的最大链路速度为 8GT/s 或 16GT/s

如果 CXL1.1 物理层实现仅支持最大速度为 8GT/s 或 16GT/s 的 Flex Bus.CXL 操作,则它仍然必须通告 在 2.5GT/s 链路训练期间支持 32GT/s 速度,以使用修改后的协议执行备用协议协商

TS1 和 TS2 有序集。 一旦备用协议协商完成,Flex Bus 逻辑 PHY 就可以根据 PCIe 规范公布其支持的真实最大链路速度。 强烈建议CXL2.0设备支持32GT/s链路速率; 然而,CXL2.0 设备被允许使用所描述的算法

如果不支持 32 GT/s 链路速率,请在本节中启用 CXL 备用协议协商。

实施说明

在早期训练中宣传支持 32GT/s 的 CXL 设备,实际上并不真正支持 32 GT/s 链路速率,可能存在 Config.LinkWidthStart 中的 Polling.Compliance 和 Loopback 条目的兼容性问题。 请参阅 PCIe 规范

更多细节。 执行此操作的设备必须确保它们提供一种机制来禁用此行为,以实现轮询合规性和环回测试场景。

6.4 Recovery.Idle和Config.Idle转换到L0

PCIe规范要求从Recovery.Idle切换到L0,或从Config.Idle切换到L0,链路双方需要传输和接收特定数量的连续空闲数据符号。当Flex Bus的逻辑PHY处于CXL模式时,会监测NULL flits而不是空闲字符来启动到L0的转换。当处于CXL模式下Recovery.Idle或Config.Idle时,如果接收到四个连续的NULL flit并且在接收到一个NULL flit之后发送了八个NULL flit时,则下一个状态为L0。

6.5 L1中止场景

由于 CXL ARB/MUX 虚拟化链路层看到的链路状态,并且仅在链路层一致时请求物理层转换到 L1,因此可能存在导致 L1 中止场景的竞争条件。 在这种情况下,当 ARB/MUX 不再请求进入 L1 时,物理层可以接收 EIOS 或检测到电气空闲。 在这种情况下,物理层需要启动链路恢复,将其恢复到L0。

6.6 Recovery退出

退出恢复后,接收器假定在恢复进入之前发送的任何部分 TLP 都已终止,并且必须通过链路级重试完全重新发送。 部分 TLP 包括在进入恢复之前未接收到后续 EDB、空闲或有效帧令牌的 TLP。 发射机必须满足

使接收者能够做出此假设的任何要求。

6.7 Retimer和低延迟模式

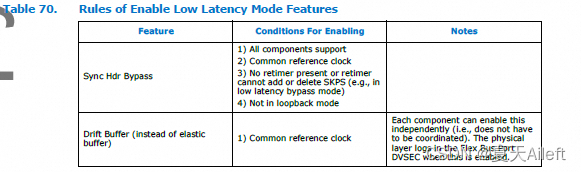

CXL 规范支持以下功能,可以启用这些功能来优化延迟:绕过同步 hdr 插入以及使用漂移缓冲区而不是弹性缓冲区。 同步 hdr 旁路的启用是在第 6.3.1.1 节中描述的 Flex Bus 模式协商过程中协商的。 下游端口、上游端口和任何重定时器在阶段 1 期间通告其同步 hdr 旁路功能; 下游端口传达是否在阶段 2 期间启用同步标头旁路的最终决定。漂移缓冲区模式由每个组件在本地决定。 表 70 总结了启用每个功能的规则; 这些规则预计将由硬件执行。

Sync Hdr Bypass:

All components support:

这意味着链路中所有组件必须支持Sync Hdr Bypass模式。如果链路中的任何设备或组件不支持这种模式,那么不能使用Sync Hdr Bypass。

Common reference clock:

这是指链路上的所有设备都必须使用同一个参考时钟(common reference clock)。在PCIe系统中,设备可以使用独立的参考时钟(separate reference clocks,SRC)或公共的参考时钟(common reference clock,CRC)。Sync Hdr Bypass模式要求所有组件使用CRC,这可能是为了确保链路上的时钟同步和简化时钟域转换。

No retimer present or retimer cannot add or delete SKP ordered sets (e.g., in low latency bypass mode):

这个条件指出在使用Sync Hdr Bypass模式时,不能有重定时器(retimer)存在于链路中,或者存在的重定时器不能增加或删除SKIP(SKP)有序集。SKP有序集是用于链路流控制的特殊数据包,用来保持链路的完整性和数据的正确传输。如果重定时器在低延迟旁路模式下操作,并且不能添加或删除SKP有序集,那么可以使用Sync Hdr Bypass模式。

Not in loopback mode:

这表示链路不能处于回环测试模式(loopback mode)。在PCIe中,回环模式是一个用于测试和诊断链路的功能,其中设备会发送并接收自己的数据。Sync Hdr Bypass模式要求链路不在这种模式下,可能是因为回环模式与该模式的同步要求不兼容。

6.7.1 SKP 有序集频率和 L1/恢复条目

在 Flex Bus.CXL 模式下,如果启用同步标头旁路,则适用以下规则:

• 在SDS 之后,物理层必须在每340 个数据块之后调度一个控制SKP 有序集或SKP 有序集,除非它正在退出数据流。 笔记:

控制 SKP OS 与常规 SKP OS 以 16 GT/s 或更高速度交替; 在 8 GT/s 时,仅调度常规 SKP 操作系统。

• 当退出数据流时,物理层必须用EIOS(对于L1 进入)或EIEOS(对于包括恢复在内的所有其他情况)替换调度控制SKP OS(或SKP OS)。

当启用同步 hdr 旁路优化时,重定时器依靠上述机制来了解 L1/恢复条目何时发生。 当同步 hdr 旁路未启用时,重定时器不得依赖上述机制。 虽然上述算法规定了数据流内的控制 SKP OS 和 SKP OS 频率,但应该注意的是,CXL 设备仍然必须满足控制 SKP OS 和 SKP OS 插入的 PCIe 基本规范要求,这至少是

当不在 SRIS 中运行时,每 370 到 375 个块更新一次。

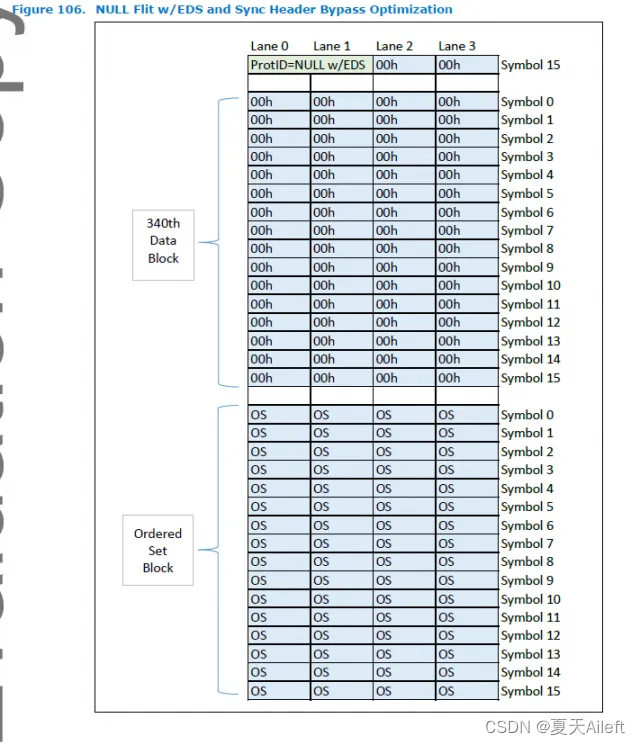

图 106 说明了一种场景,其中在启用同步 hdr 旁路的情况下,在退出数据流之前将带有隐含 EDS 令牌的 NULL flit 作为最后一个 flit 发送。 在此示例中,在第 339 个块末尾附近,链路层没有要发送的 flits,因此物理层插入 NULL flit。 因为之前正好有一瞬间的时间

必须发送下一个有序集,使用带有隐含 EDS 令牌的 NULL flit。 在这种情况下,带有 EDS 令牌的可变长度 NULL flit 跨越块边界并包含 528 位零负载。

图 107 说明了一种场景,其中在使用 128/130b 编码的情况下,在退出数据流之前将带有隐含 EDS 令牌的 NULL flit 作为最后一个 flit 发送。 在此示例中,NULL flit 仅包含 16 位零负载。

本文详细阐述了FlexBus在CXL协议中的作用,涉及物理层的数据接收和转发、链路训练过程中的协议ID处理、帧错误检测与恢复机制,以及低延迟模式下的优化策略。

本文详细阐述了FlexBus在CXL协议中的作用,涉及物理层的数据接收和转发、链路训练过程中的协议ID处理、帧错误检测与恢复机制,以及低延迟模式下的优化策略。

55

55

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?