--------------------------------- 资料获取方式 ---------------------------------

仅代码:

链接:https://pan.baidu.com/s/1l905Q_YbVH0ivnw35VISmQ

提取码:2233

复制这段内容后打开百度网盘手机App,操作更方便哦

代码以及环境安装包:

链接:https://pan.baidu.com/s/1YauNKEGL8Nq1fcmeKODjDw

提取码:2233

复制这段内容后打开百度网盘手机App,操作更方便哦

-------------------------------------------------------------------------------------------

目录

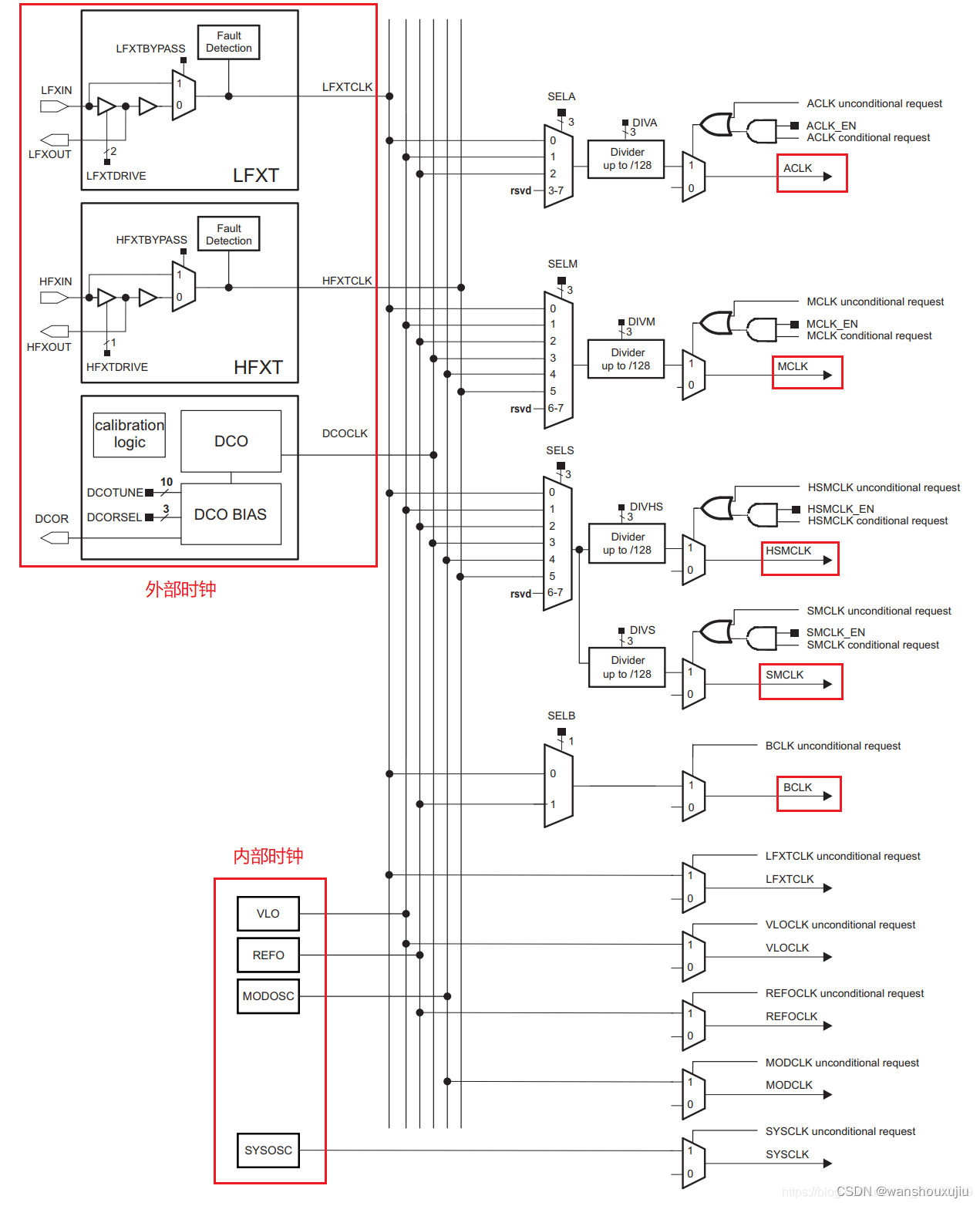

一、整体框图

二、时钟源

1、LFXT(外部低速)

- 一般为32.768kHz

2、HFXT(外部高速)

- 外接 1M 至 48M 的晶振

2、DCO(内部数控振荡器)

- 默认 3M

- 可以软件编程至 48M 或超频至 64M

4、VLO

- 内部极低功率低频振荡器(VLO),典型频率为 9.4khz

5、REFO

- 内部低功率低频振荡器(REFO),可选择 32.768kHz 或 128kHz 的典型频率

6、MODOSC

- 模块振荡器,25M 典型频率的内部低功率振荡器

三、时钟信号

由框图中间部分可知时钟信号可以选择不同的时钟源作为输入

1、ACLK(辅助时钟)

- 最高 128khz

- 有分频器(可被1、2、4、8、16、32、64或128除)

- 可给外设提供时钟

2、MCLK(主时钟)

- 直连CPU

- 有分频器

- 给外设提供时钟

3、HSMCLK(子系统时钟)

- 有分频器

- 给高速外设提供时钟

4、SMCLK(低速子系统时钟)

- 有分频器

- 使用 HSMCLK 分频得到,最高为 HSMCLK 最高时钟的一半

- 给外设提供时钟

5、BCLK

- 最高 32.768 kHz

- 主要用于备份域

6、其他时钟

VLOCLK、REFOCLK、LFXTCLK、MODCLK 和 SYSCLK 是来自时钟模块。其中一些不仅可以作为各种系统时钟的资源,而且可以也可直接用于各种外设模块

四、默认时钟

详情参考技术手册6.2节

- 系统复位或者不进行配置时,内核电压等级0,最高 24Mhz

- ACLK、BCLK 默认连接 LFXT(外部低速)

- LFXT(外部低速)此时禁用,因为引脚设置为了通用引脚,除非设置复用,此时 ACLK、BCLK 连接至 REFO 时钟为 32.768khz

- HFXT(外部高速)也默认禁用

- MCLK、HSMCLK、SMCLK 连接到 DCO(数控时钟源),默认 3M

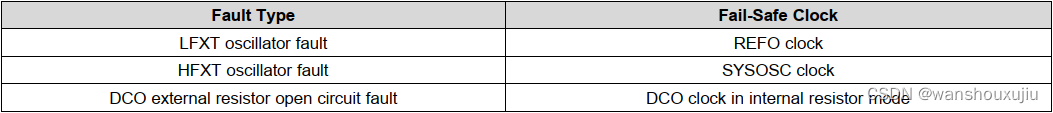

五、故障机制

LFXT、HFXT 故障时连接到 REFO 和 SYSOSC

DCO 外部电阻故障时使用内部电阻

1050

1050

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?