目录

2024.4.18更新

应该不用改Fs,采样是正常的。

大家好,我是魏通。

受刘健老师之托,继上周三讲粗略地讲完傅里叶变换后,这周三我将更全面地为大家讲解电赛2020年E题的实现。

希望对你有所帮助。

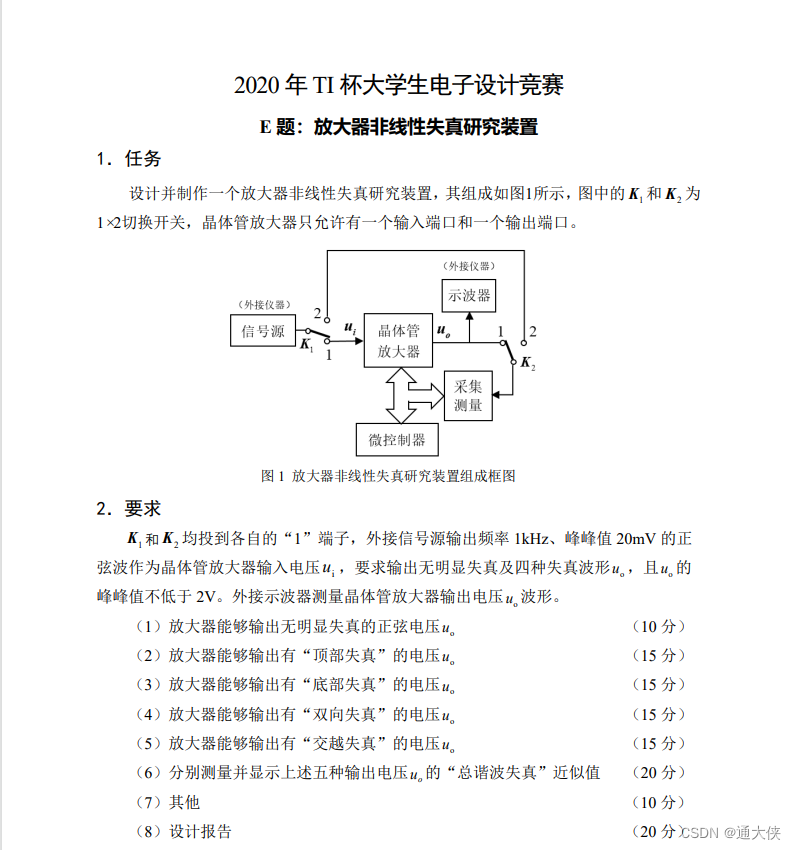

一、比赛题目

作为咱们做的第一道题,难度相对来说肯定是不大的。

概括一下,该题是要求你设计一个三极管电路,要求改电路能输出各种失真波形并用单片机测量波形的电压值。

二、硬件电路

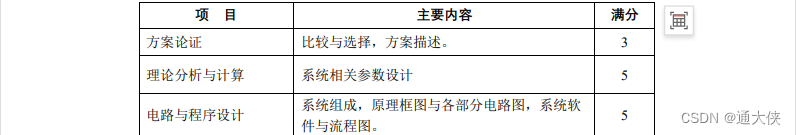

1、仿真阶段

敲代码前肯定是要先把电路焊好,焊电路之前一定要先仿真。

我们来看一下该题核心电路Multisim的电路仿真。

图2.1 核心电路

下面是每一级电路的“特写镜头”。

图2.2 第一级电路

该电路的作用是将信号发生器微小的小信号(Vp=10mV)放大。

图2.3 第二级电路

该级电路的作用是“缓冲”(电压跟随器)。

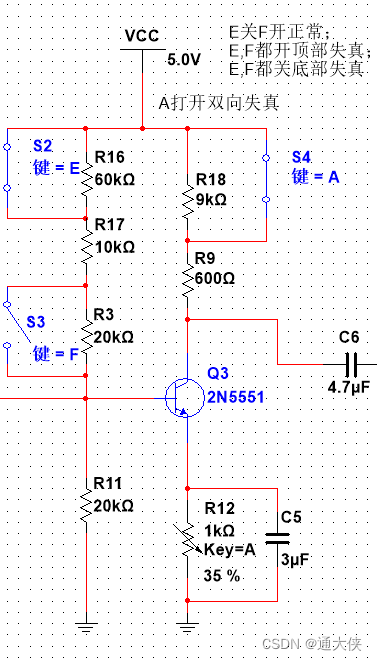

图2.4 第三级电路

该级电路的作用是通过控制开关实现三种失真,分别是:顶部失真、底部失真和双向失真。

注:图中所说的A是指第一个按键A。

图2.5 第四级电路

该级电路的作用是通过开关控制实现交越失真。

让我们来看看效果。

图2.6 演示

2、焊接阶段

焊接就没什么好说的了,基本功,照着电路图仔细一点焊就好。

不过有一点我想提一下:

不要把大部分电路都焊在一个洞洞板上。

不要把大部分电路都焊在一个洞洞板上。

不要把大部分电路都焊在一个洞洞板上。

(当然,如果你用画PCB板当然可以搞集成化,前提是你已经验证过你的电路没有问题。)

我甚至看到有的同学把全部的电路焊在了一个洞洞板上,如图2.7。

图2.7 不推荐的焊接方式

绿色的矩形代表洞洞板。

把所有电路焊在一起有一个最致命的问题是:一旦出错有可能整块板子就废掉了。

所以,我建议你将他们“模块化”,如图2.8。

图2.8 推荐的焊接方式

绿色的矩形代表洞洞板,蓝线、黄线代表飞线。

一定要把每个板的“地”,也就是”GND”连起来。这就是所谓的“共地”。共地很重要,切记。

至于怎么连接两个洞洞板,我推荐以下两种方式:

方式一:xh2.54端子加电子线

图2.9 接线方式一

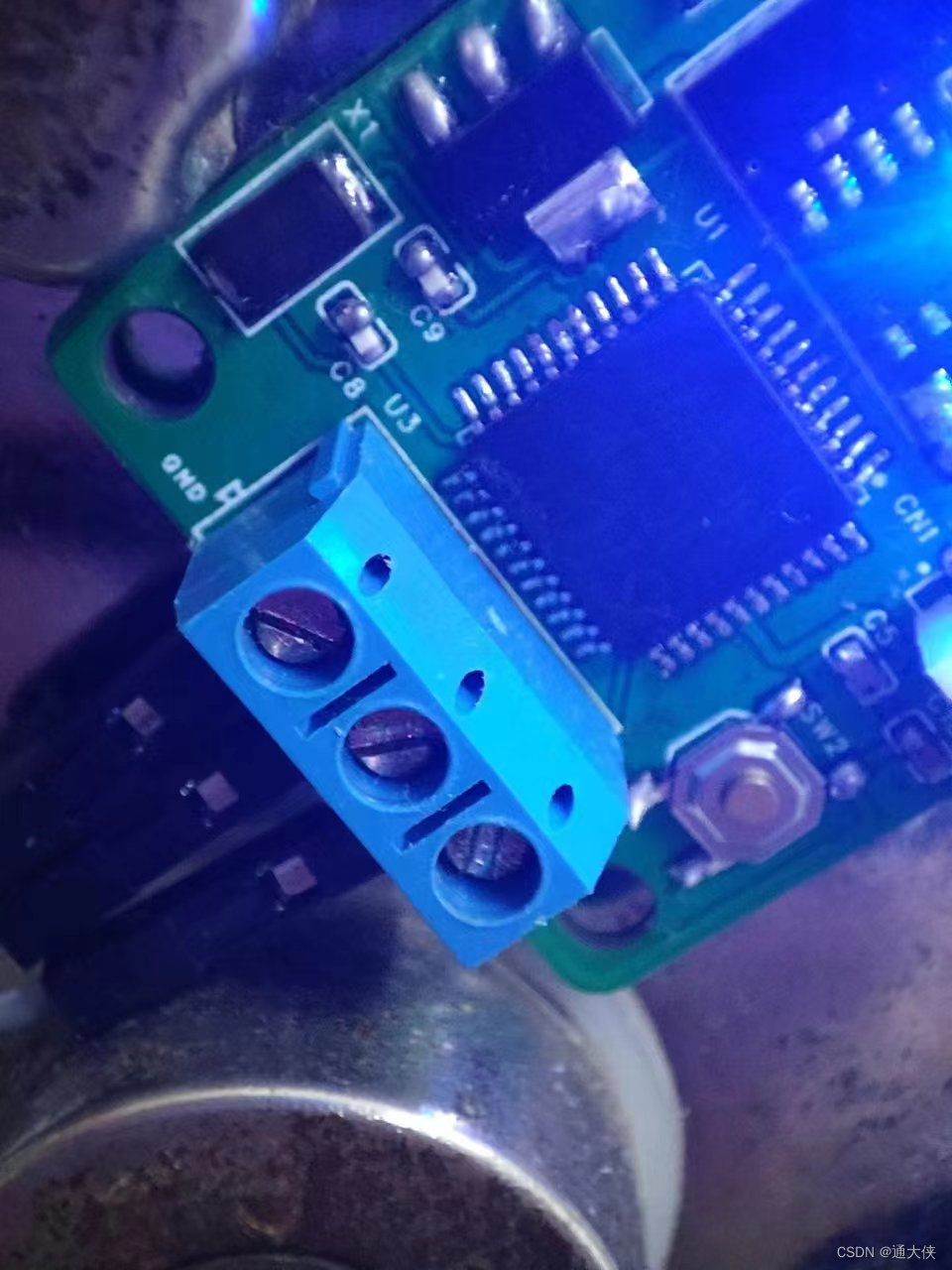

方式二:螺钉式接线端子加杜邦线

图2.10 接线方式二

三、其他

1、继电器

让我们再回头看看核心电路。

我们实现各种失真是通过开/合不同开关实现的,或许你跟我一样,想到了一种开关——继电器。

图3.1 继电器(图片来自网络)

继电器一般有六个引脚,他们分别是:

VCC(电源正极)

GND(地)

IN(信号输入端):用于检测信号,接单片机的GPIO口。

NC(常闭接口):等效开关闭合状态。

COM(公共端)

NO(常开接口):等效开关打开状态。

图3.2 继电器接线图

将COM和NO接入核心电路,代替开关的位置。将VCC、GND、IN与单片机相连接。

此时,当GPIO口输出一个高电平,继电器将会闭合(开关闭合);GPIO口输出一个低电平,继电器将会打开(开关打开)。

2、偏置电路

题目中要求了要让单片机检测各种波形的电压,由于stm32能采集的电压范围是0~3.3V,所以核心电路输出的正弦波负电压部分采集不到。这就需要偏置电路登场了,hahaha。

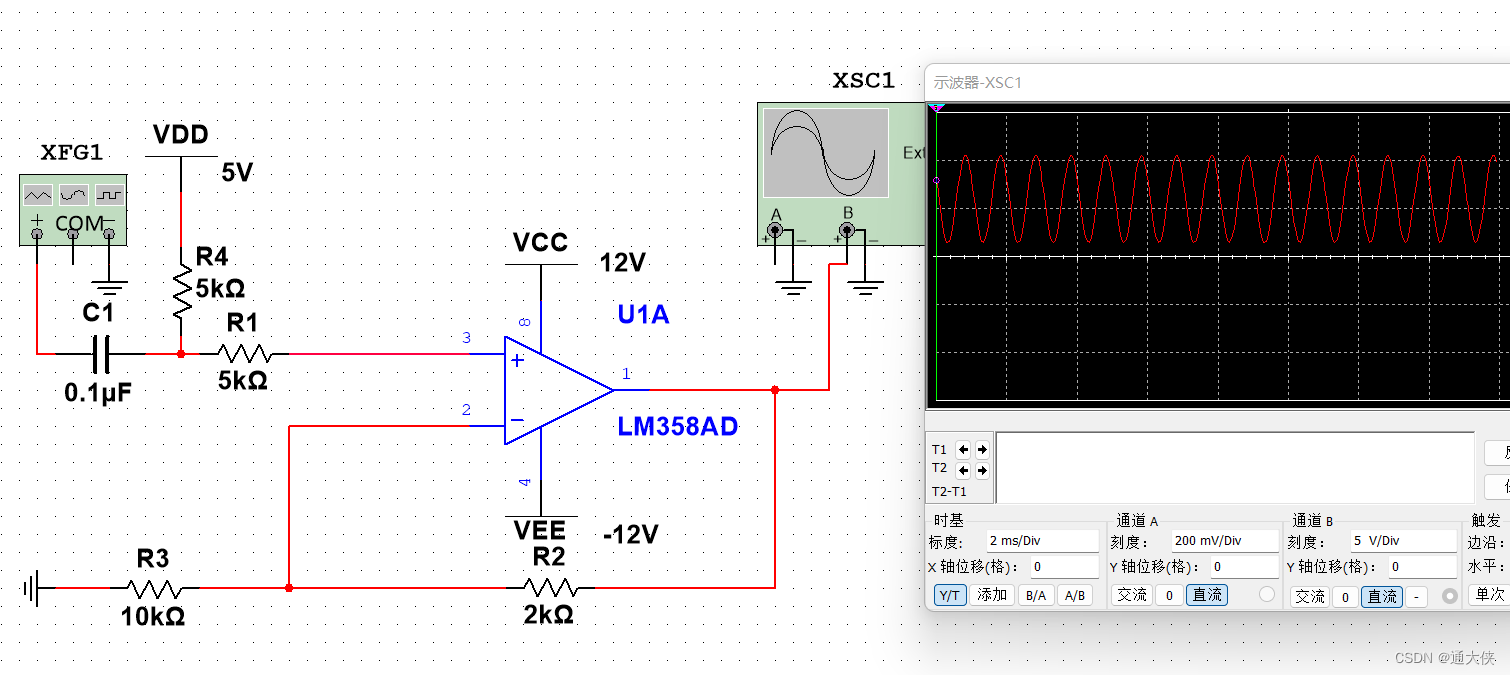

图3.3 偏置电路工作原理

没有负电压,stm32就可以轻松采到电压了。

注意抬升电压不能过高,电压超过3.3V有烧坏单片机的风险。

图3.4 偏置(抬升)电路原理图

VDD可通过电阻分得VCC的电压得到,R2最好是电位器,这样即使输出波形失真仍有挽回的余地。(波形失真是因为放大倍数太大,通过改变R2的阻值可以减小放大倍数)

四、软件部分

本题软件部分相对简单,只需要让stm32正确地采集AD值即可还原波形、计算出电压和THD的值。

下面简单地介绍一下基础外设。

模数转换器ADC

图3.1 ADC基本框图(江协科技绘)

图3.1 ADC基本框图(江协科技绘)

转换时间

Tconv=采样时间+12.5个ADC周期

采样时间短,速度快;采样时间长,抗干扰。

区别时钟频率、采样频率、转换时间

时钟频率:单片机的“心脏”。

采样频率:启动ADC采样的频率,例如每隔1ms采样一次,采样频率是1KHz;每隔1us采样一次,采样频率是1MHz。采样频率由自己设置。

转换时间:转换通道/序列所费时间。

本题我们需要测量的信号的频率是1KHz,即周期为0.001s,也就是1ms。

想要还原出测量的波形,一个周期至少要采20个点。换句话说,采样频率要大于等于20KHz。

上次讲傅里叶变换时我说过:针对该题,我们使用的采样频率Fs是10240Hz(根据香农采样定理,采样频率要大于等于所测信号最频率的两倍)

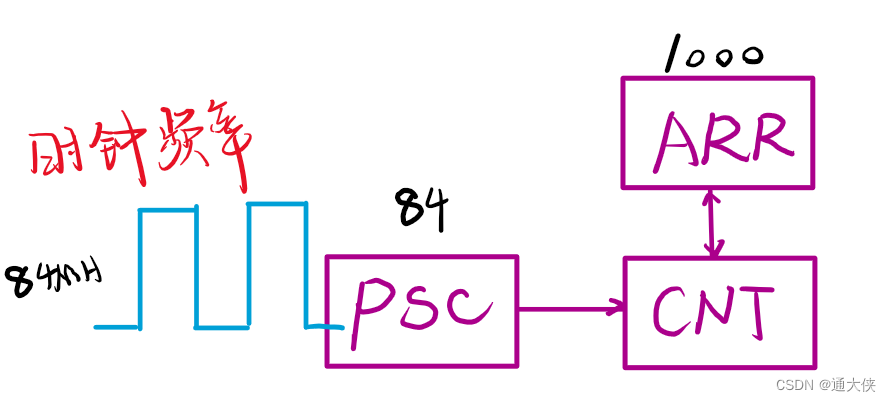

还记得怎么算PSC和ARR吗?

稍作处理,得到

其中,84MHz是指时钟频率,Fs是指采样频率,PSC是指预分频器,ARR是指自动重装载寄存器。

对8203进行因式分解,得到8203=13*631。

定时器TIM

图3.2 时基单元

图3.2所示的时基单元是定时器最基本,同样也是最重要的一部分。

定时器就是计数器。

如果把PSC设置为2,那么输入的时钟频率就会被3分频。每进入一个时钟脉冲,PSC就会记1,直到记到2(记了0,1,2这三个数),PSC才会输出一个脉冲给计数器。

若想实现定时功能,离不开ARR的功劳。

ARR叫做自动重装载寄存器,它的功能是当计数器CNT记到和自己一样的数时,将CNT置0。

想要实现定时中断只需要在CNT置0的同时触发一次更新中断即可。

屏幕

根据老师的要求,要测核心电路输出的电压的同时还要在自己的屏幕上画出波形。由于每个人的屏幕型号各不相同,我就不展开来说了。总而言之,就一句话:采点、连线。

此外,我听说有的同学最终得到的正弦波形有点像三角波,我想或许是采样点过少。

我想能否通过增加采样点个数来解决这个问题。比如由原来的十个点增加到二十个点。

其中N代表采样点数,我们设置为采1024个点。

(所测信号的频率是1KHz)

想要增加到采二十个点只需要把Fs扩大两倍,即

这里需要注意,原先的1KHz的信号经过FFT得到的值会由出现在第一百个点变成出现在第五十个点。(DFT的函数中的*100要改成*50)

想让Fs变为20480Hz,要改一下PSC和ARR。

根据上文,我们知道这样一个公式:

注意一下,如果你用的是其他型号的单片机,时钟频率可能会不同,例如stm32f103,84MHz的位置就应该改成72MHz。

带入Fs = 20480Hz,得

对4151进行因式分解,得到4151 = 3 * 1367 (即得到PSC 和 ARR的值)

该方法我自己没有去做,只是尽可能地给大家提供解决办法。感兴趣的同学可以试试,如有错误或者有其他问题请留言,我会及时改正、回复,谢谢!

参考链接

STM32: ADC采样频率及相应时间的确定![]() https://blog.csdn.net/laifengyuan1/article/details/107481945

https://blog.csdn.net/laifengyuan1/article/details/107481945

STM32 HAL库ADC详细篇(单通道、多通道、DMA方式等)![]() https://blog.csdn.net/dongxiaodongvip/article/details/114498855

https://blog.csdn.net/dongxiaodongvip/article/details/114498855

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?