一般来说,时钟精度、稳定性取决于所采用的时钟源,就MCU S32K来说如内部振荡器SIRC,FIRC,128KLPO,外部晶振等,跟所使用的外设(FTM, LPIT,LPT,RTC等)和哪一路输出时钟(SYS_CLK,BUS_CLK,SPLLDVI1_CLK等)没有直接关系。

由于S32K144提供的时钟源和配置方法比较多,那么如何有效配置得到自己想要的时钟呢?

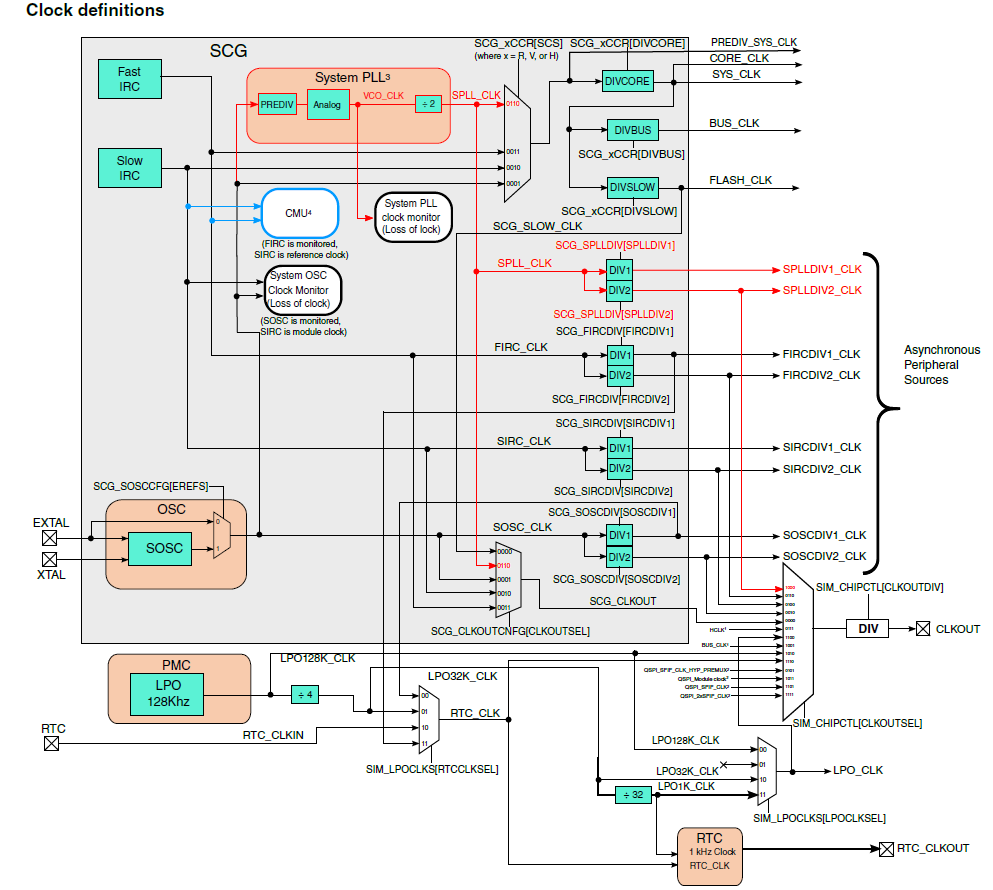

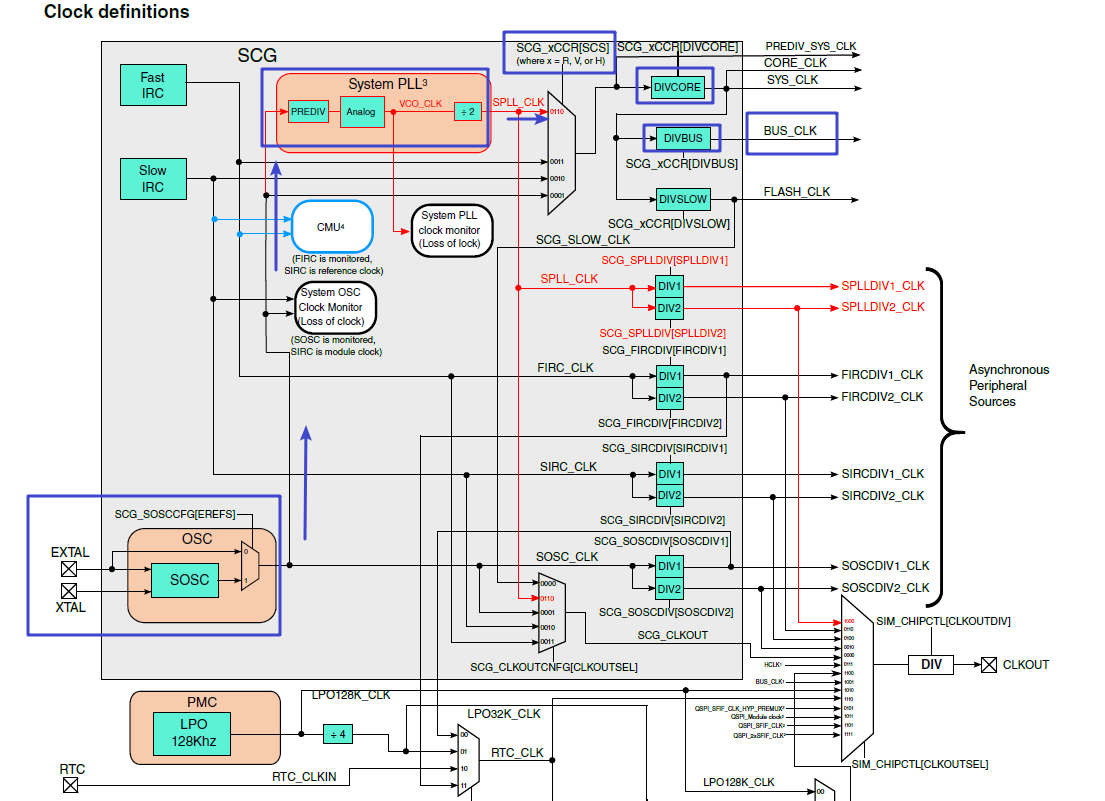

下面以S32K144为例,从时钟定义图开始,逐步介绍如何寻找S32K144时钟(CORE_CLK, BUS_CLK,)合适的配置方法,并根据测试方法验证配置是否有效。

0. 目标

输出目标

clock clock= 80MHz(以下MHz简称M)

bus clock=40MHz, Normal Mode(默认)

注意:只有支持105℃的部分S32K144型号,core clock才能支持到最高112M(HSRUN),其他型号不论HSRUN模式,还是RUN模式,最高支持80M。

测试工具

PCB: S32K144EVB-Q100

IDE: S32DS for ARM 2018.R1

1.时钟定义

配置时钟先从学会看时钟分配图开始,会看图了,配置就成功了一半。

因为能实现目标的路径可能有多种,这里先选中一条配置路径,再判断是否可行(蓝色箭头+框)。

时钟源选择外部晶振8M,即SOSC=8M => SPLL时钟源 SPLL_CLK_SOURCE = SOSC = 8M,

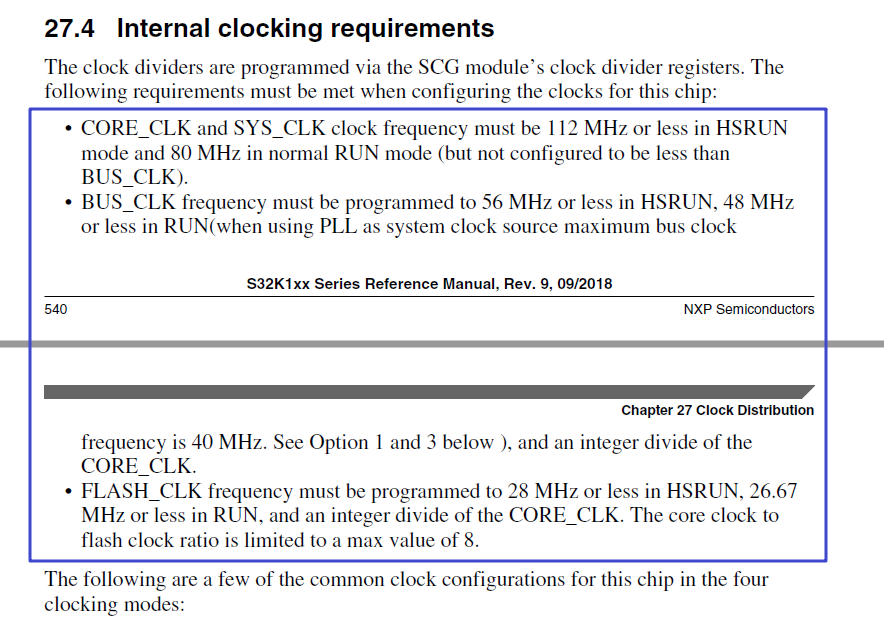

2.确认内部时钟要求

CORE_CLK/ SYS_CLK 最高支持112M(HSRUN) , 80M(RUN),目标@80M符合要求。

不过,BUS_CLK最高支持56M(HSRUN), 48M(RUN),目标@40M符合要求。

3.确认外部晶振 8M

查看S32KEVB-Q100评估板原理图,知外部晶振8M => System PLL输入 SPLL_SOURCE=8M

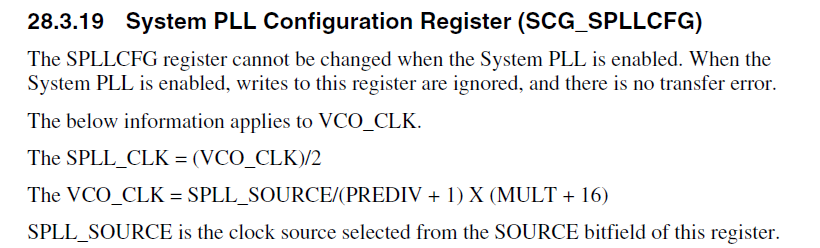

4.确认System PLL分频及倍频

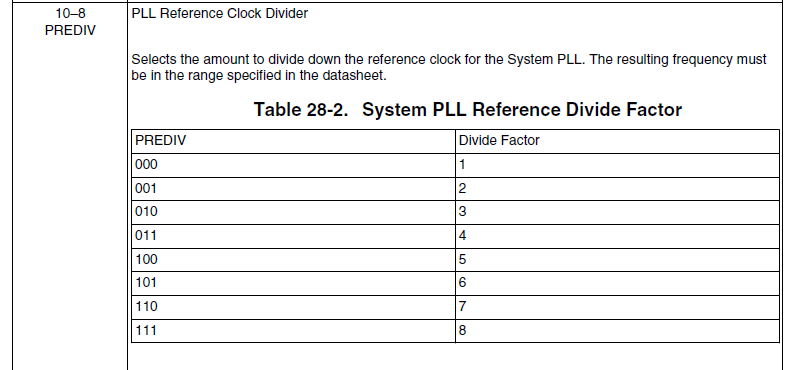

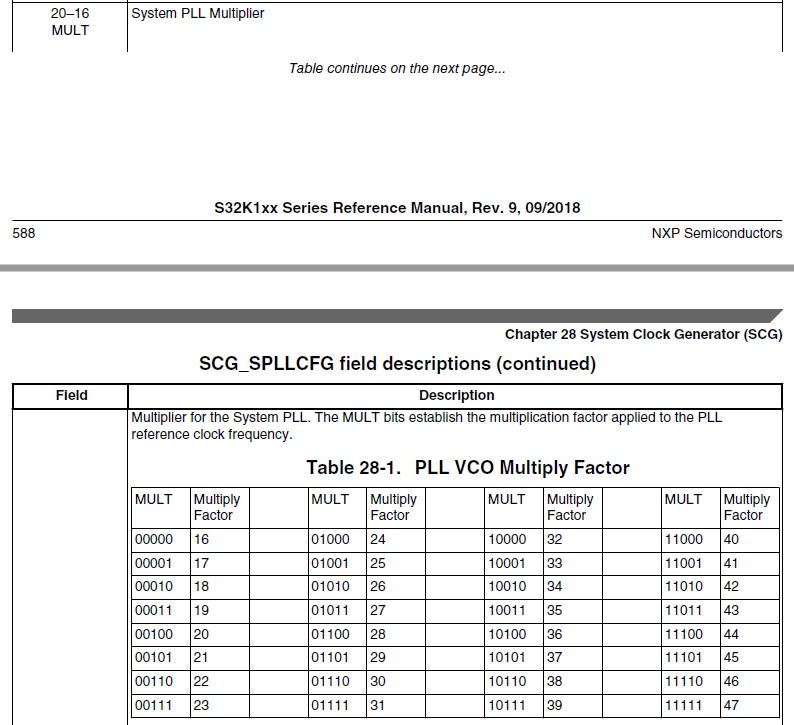

这里选择PREDIV=0, MULT=0b11000 (10进制: 24)

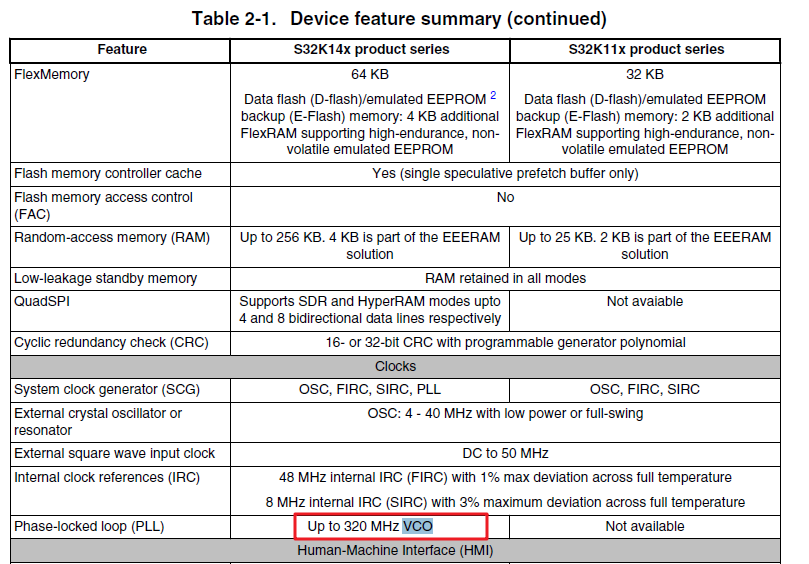

VCO_CLK=8M/(0+1) X (24+16) = 320MHz

SPLL_CLK=(VCO_CLK)/2 = 160MHz

考虑:这里MULTI还可以>24 => 倍频因子>40,那么能不能配置VCO_CLK >320M,而最终CORE_CLK=80M呢?

答案是不行,因为VCO_CLK最高支持到320M,可以参考S32K-RM。

5.具体寄存器配置

可参考RM配置方法

6.设置检测方法

1)初步确定为通过IO口直接输出与总线时钟相关的时钟或者分频后的时钟

2)寻找SCH上是否有可直接利用的MCU引脚

MCU完整型号:FS32K144HRT0VLLT, 封装:LQFP100

查RM附件IO描述表,发现能作为CLKOUT pin的有PTD14, PTE10, PTB5。

如有可用CLKOUT pin,配置相应的pin为CLKOUT功能

1)配置PORT的MUX为CLKOUT对应ALT功能,并使能端口时钟;

2)配置SIM_CHIPCTL选择输出的时钟,

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1647

1647

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?