在FPGA的设计中,避免不了使用厂家的原语。zynq-7020是xilinx的7 series FPGA,参考《UG768-Xilinx 7 Series FPGA Libraries Guide for HDL Designs》查看相应的原语使

永指导

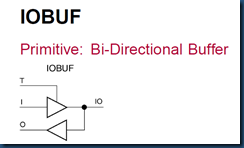

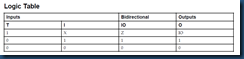

一、IOBUF的介绍

2、example code:

来自xilinx官网论坛

module abcd(

input clk,

inout io_data,

input t,

output reg ext_out,

input in_ext

);

wire data_in;

reg data_out;

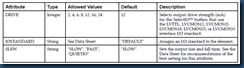

IOBUF #(

.DRIVE(12), // Specify the output drive strength

.IBUF_LOW_PWR("TRUE"), // Low Power - "TRUE", High Performance = "FALSE"

.IOSTANDARD("DEFAULT"), // Specify the I/O standard

.SLEW("SLOW") // Specify the output slew rate

) IOBUF_inst (

.O(data_in), // Buffer output

.IO(io_data), // Buffer inout port (connect directly to top-level port)

.I(data_out), // Buffer input

.T(t) // 3-state enable input, high=input, low=output

);

always @(posedge(clk))

begin

ext_out <= data_in;

data_out <= in_ext;

end

endmodule

综合后:

二、参考资料

1、https://forums.xilinx.com/xlnx/board/crawl_message?board.id=SYNTHBD&message.id=16841

2、UG768-《Xilinx 7 Series FPGA Libraries Guide for HDL Designs》

7155

7155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?