国庆放假休息好几天 现在才发.. 也没敢出京就在北京农村....

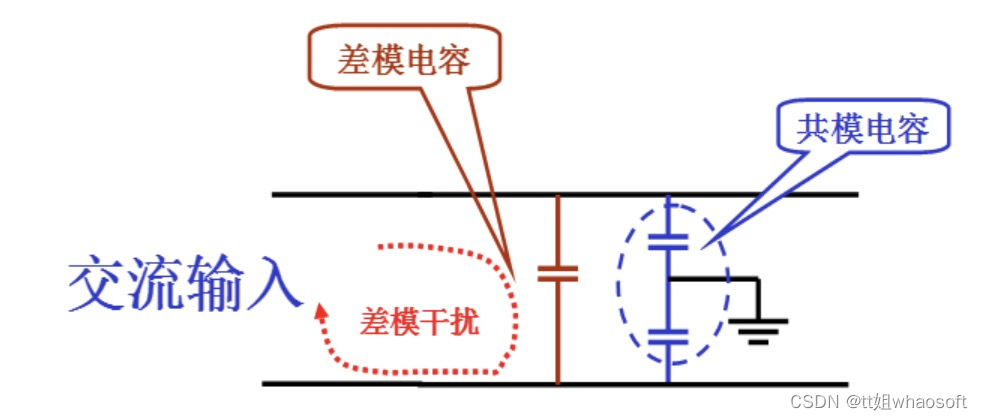

一、 共模干扰和差模干扰

共模干扰和差模干扰,一定不是第一次听说,但是其定义和区别却不一定清楚,今天和大家分享这两个概念。

1、电源线噪声是电网中各种用电设备产生的电磁骚扰沿着电源线传播所造成的。电源线噪声分为两大类:共模干扰、差模干扰。

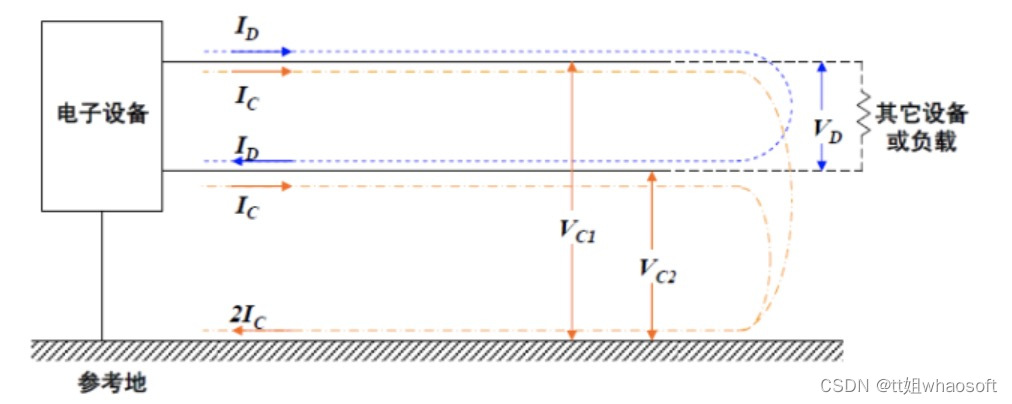

共模干扰定义为任何载流导体与参考地之间的不希望有的电位差;

差模干扰定义为任何两个载流导体之间的不希望有的电位差。

如上图, 蓝色信号是在两根导线内部作往返传输的,我们称之为"差模";黄色信号是在信号与地线之间传输的,我们称之为"共模"。

2.1共模干扰信号

共模干扰的电流大小不一定相等,但是方向(相位)相同的。电气设备对外的干扰多以共模干扰为主,外来的干扰也多以共模干扰为主,共模干扰本身一般不会对设备产生危害,但是如果共模干扰转变为差模干扰,干扰就严重了,因为有用信号都是差模信号。

2.2差模干扰信号

差模干扰的电流大小相等,方向(相位)相反。由于走线的分布电容、电感、信号走线阻抗不连续,以及信号回流路径流过了意料之外的通路等,差模电流会转换成共模电流。

2.3共模干扰产生原因

1. 电网串入共模干扰电压。

2. 辐射干扰(如雷电,设备电弧,附近电台,大功率辐射源)在信号线上感应出共模干扰,原因是交变的磁场产生交变的电流,地线-零线回路面积与地线-火线回路面积不相同,两个回路阻抗不同等原因造成电流大小不同。

3.接地电压不一样,简单的说就电位差而造就了共模干扰。

4.设备内部的线路对电源线造成的共模干扰。

2.4共模干扰电流

共模干扰一般是以共模干扰电流存在的形式出现的,一般情况下共模干扰电流产生的原因有三个方面:

1. 外界电磁场在电路走线中的所有导线上感应出来电压(这个电压相对于大地是等幅和同相的),由这个电压产生的电流。

2. 由于电路走线两端的器件所接的地电位不同,在这个地电位差的驱动下产生的电流。

3. 器件上的电路走线与大地之间有电位差,这样电路走线上会产生共模干扰电流。

2.5注意事项

1.器件如果在其电路走线上产生共模干扰电流,则电路走线会产生强烈的电磁辐射,对电子、电气产品元器件产生电磁干扰,影响产品的性能指标;

2.当电路不平衡时,共模干扰电流会转变为差模干扰电流,差模干扰电流对电路直接产生干扰影响。对于电子、电气产品电路中的信号线及其回路而言:差模干扰电流流过电路中的导线环路时,将引起差模干扰辐射,这种环路相当于小环天线,能向空间辐射磁场,或接收磁场。

3. 共模干扰主要集中在1MHz以上。这是由于共模干扰是通过空间感应到电缆上的,这种感应只有在较高频率时才容易发生。但有一种例外,当电缆从很强的磁场辐射源(例如,开关电源)旁边通过时,也会感应到频率较低的共模干扰。

三、如何抑制共模干扰

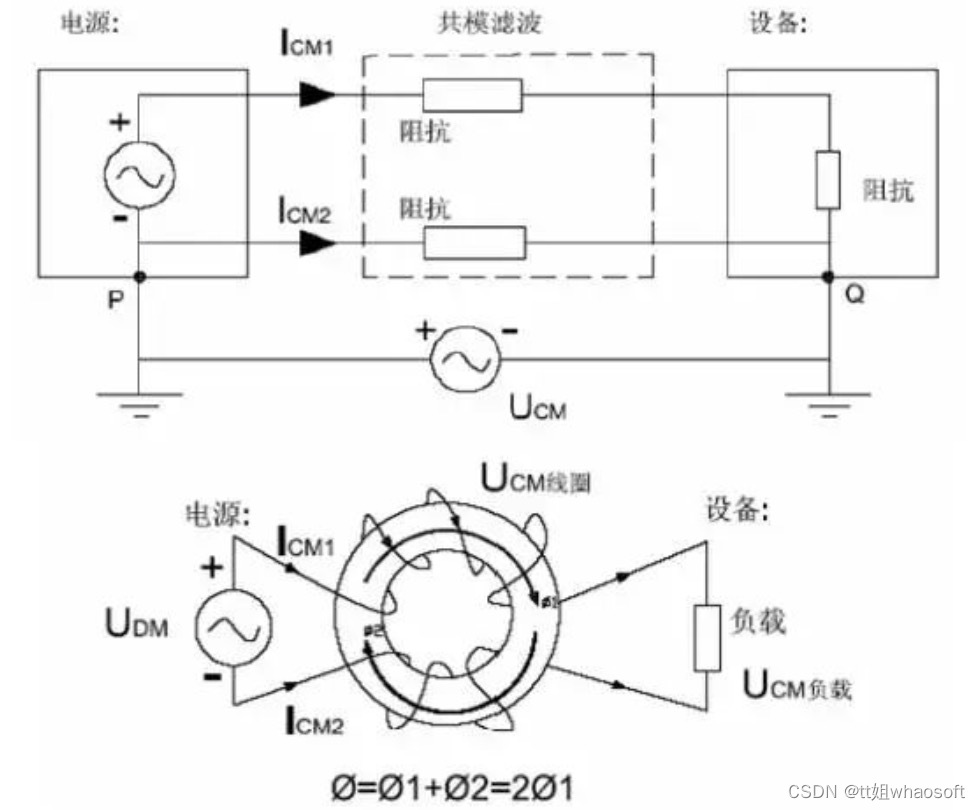

共模干扰作为EMC干扰中最为常见且危害较大的干扰,我们抑制它最直接的方法就是滤波。

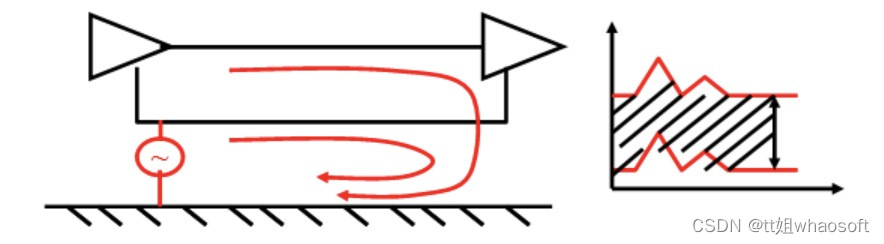

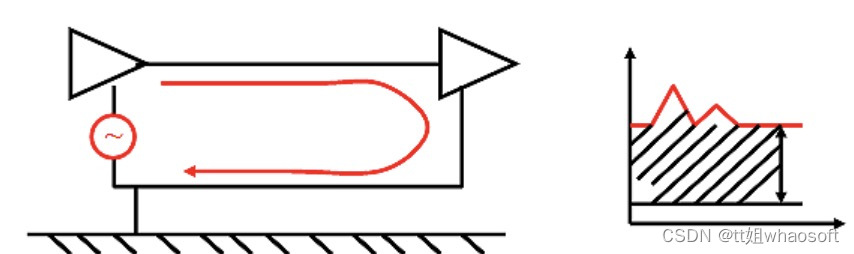

在电路中串入共模电感,当有共模干扰电流流经线圈时,由于共模干扰电流的同向性,会在线圈内产生同向的磁场而增大线圈的感抗,使线圈表现为高阻抗,产生较强的阻尼效果,以此衰减共模干扰电流,达到滤波的目的;当电路中的正常差模电流流经共模电感时,电流在同相绕制的共模电感线圈中产生反向的磁场而相互抵

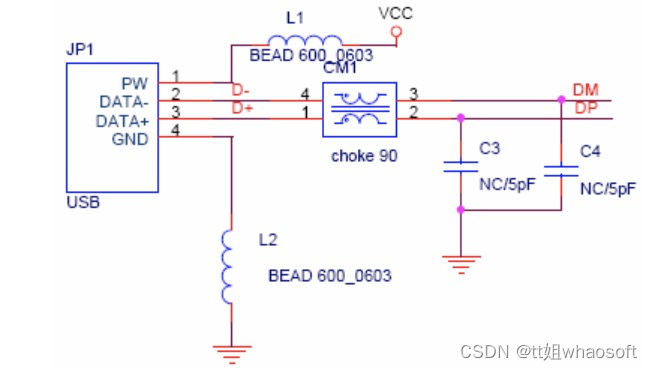

案例 USB 信号上的共模干扰抑制方法

USB 端口的滤波处理-使用共模电感

USB 传输线上的信号是差分信号而干扰源是共模干扰信号,在传输线上串上共模电感能较好的抑制共模干扰,而对有用的差分信号没有任何衰减。

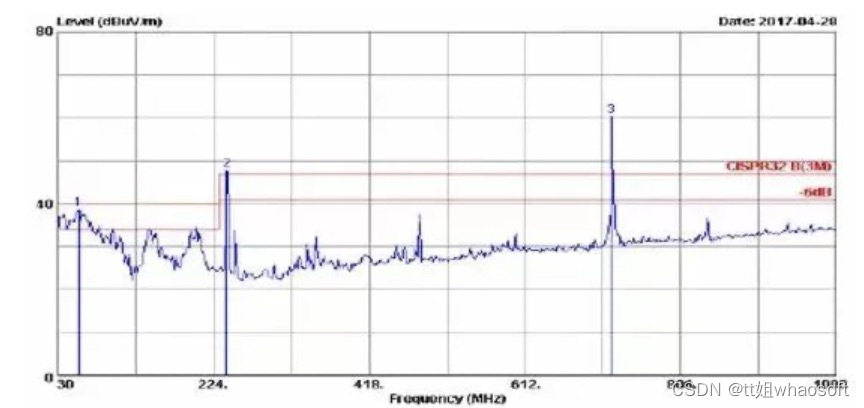

USB 高速运行会在DM/DP信号线上产生很强的共模干扰

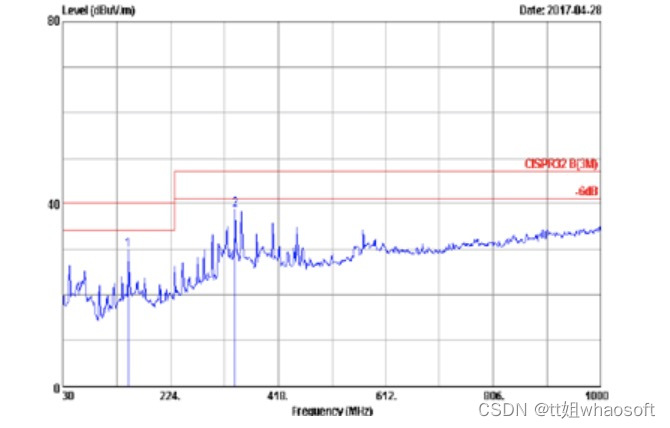

电路中加入滤波器-共模电感后共模干扰信号得到有效抑制,如果共模干扰源是在电源回路,可使用共模电容来抑制干扰信号。

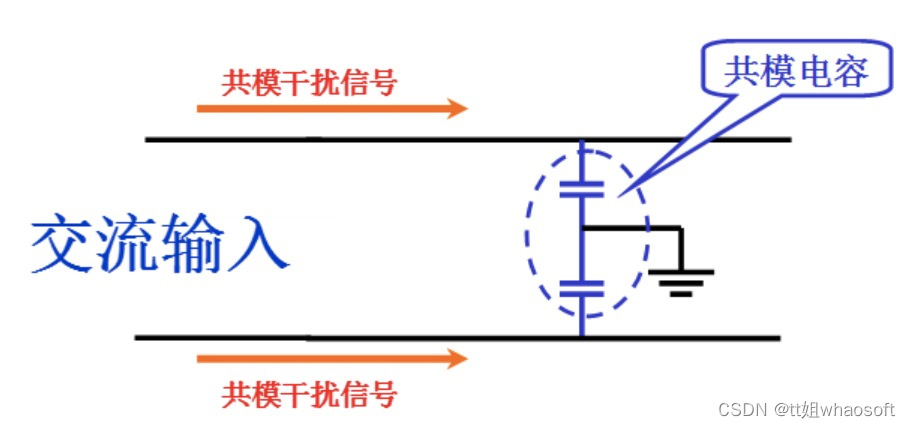

在电路中引入共模电容,则共模电容提供最短的路径使共模干扰信号被旁路,从而抑制共模干扰的产生。如果电源回路同时还存在差模干扰,使用差模电容来抑制干扰。

在电路中引入差模电容,则差模电容提供最短的路径使差模干扰信号被旁路,从而抑制差模干扰的产生。共模干扰作为EMC干扰中最为常见且危害很大的干扰,抑制它的方法除了滤波外,还可以通过对信号线路进行屏蔽,在PCB 板上大面积铺地降低地线阻抗来减少共模信号强度等方法。

二、时钟失效之后,STM32还能运行吗

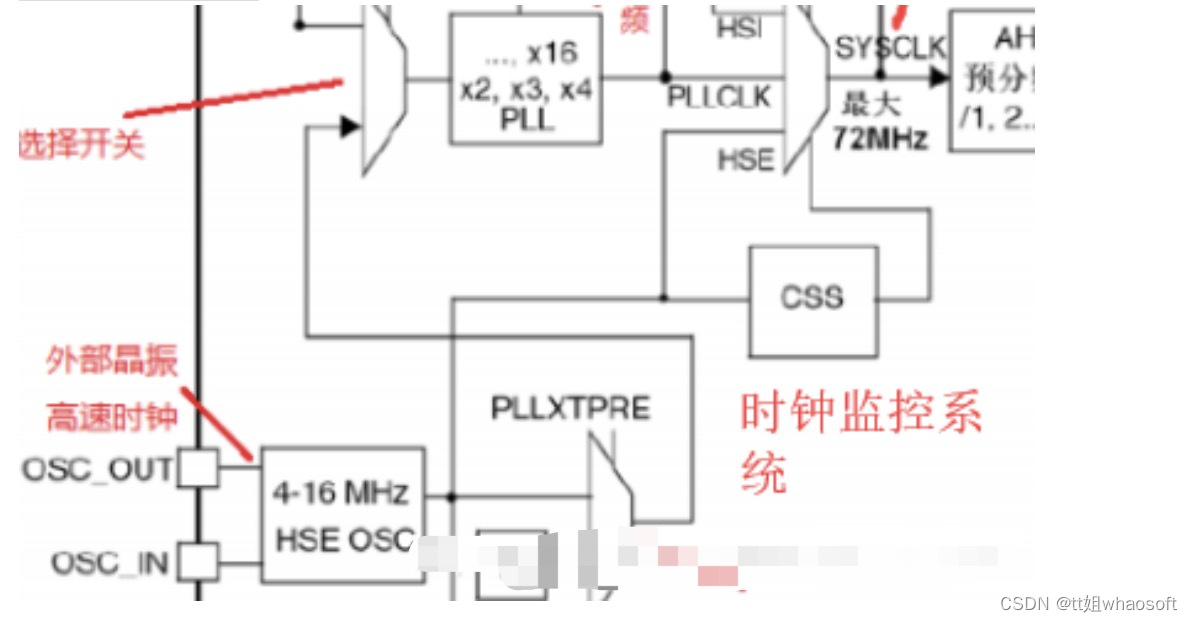

该问题由某客户提出,发生在 STM32F103VDT6 器件上。据其工程师讲述:在其产品的设计中,STM32 的 HSE 外接 8MHz 的晶体产生振荡,然后通过 STM32 内部的PLL 倍频到 72MHz,作为 STM32 的系统时钟,驱动芯片工作。在 STM32 片外有专用的看门狗芯片,监控 STM32 的运行。STM32 内部的软件会在 STM32 的某个管脚上产生脉冲来复位看门狗。一旦 STM32 没有及时的产生脉冲来复位门狗,则看门狗会认为 STM32 运行不正常,从而复位 STM32。在对该产品做可靠性测试时,进行了对看门狗监控时钟失效能力的测试。

测试的方法是:将 HSE 外接的晶体的两个端子接地,使其停止振荡,从而验证看门狗能否做出对 STM32 的做出复位动作。试验结果表明,看门狗没有产生复位动作。进一步测试发现,STM32 在失效情况下仍在向看门狗发送复位脉冲。

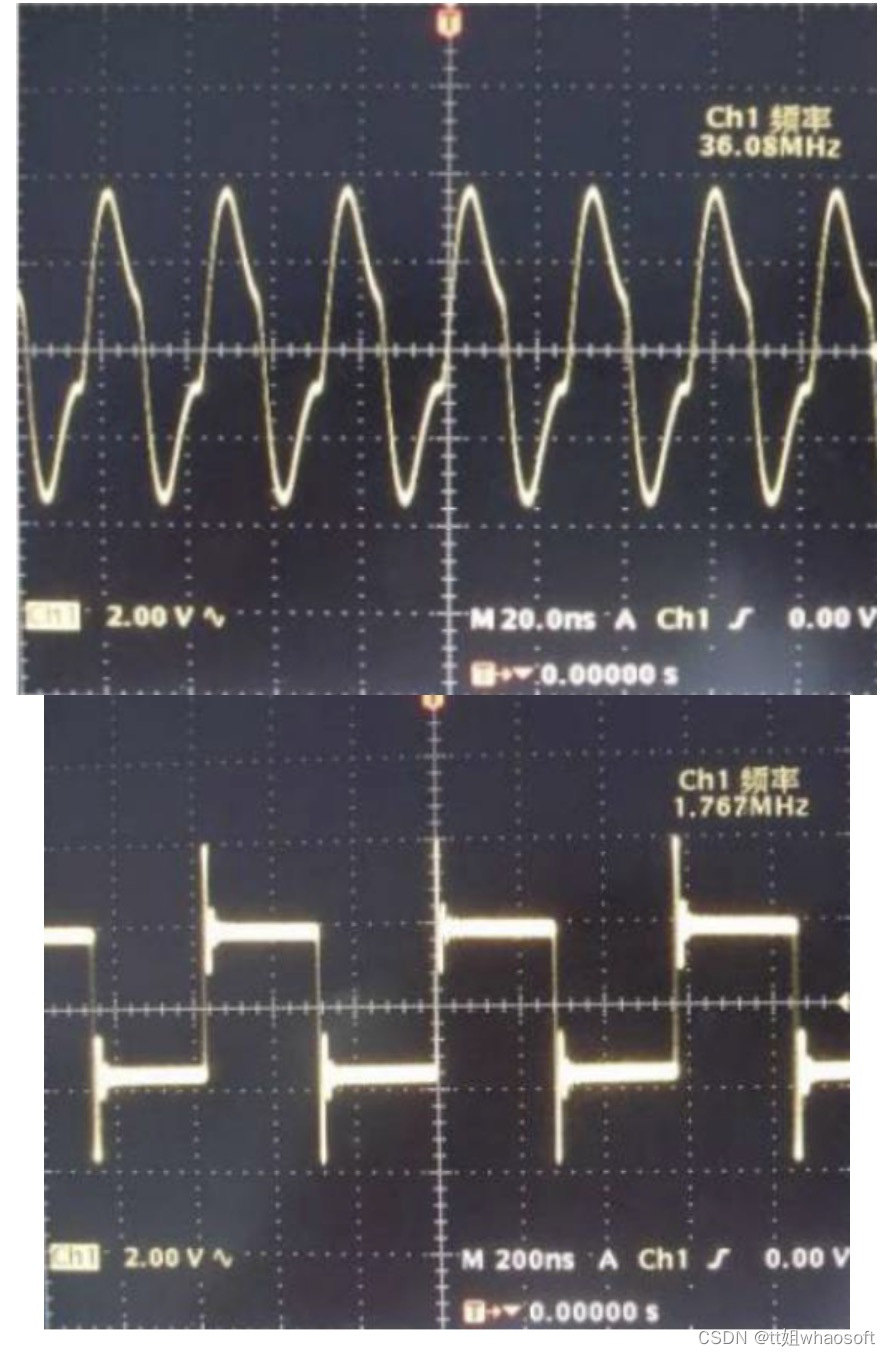

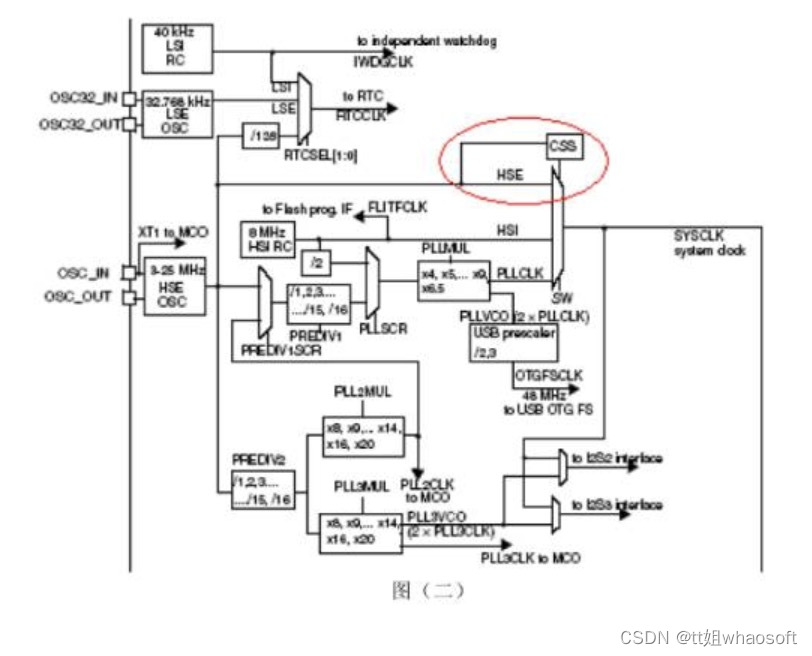

重复测试,确认其所述现象属实。检查软件代码,确认其软件没有开启 STM32 的 CSS功能。修改代码,将 PLL 的二分频从 STM32 的 MCO 管脚送出,以方便用示波器观察。通过控制晶体的管脚是否接地来控制 HSE 是否振荡。当 HSE 正常振荡时,MCO 送出的信号频率为 36MHz,当 HSE 停止振荡时,MCO 送出的信号的频率在 1.7MHz 附近,如图(一)所示:

通过调试器观察寄存器 RCC_CFGR 中的 SWS 控制控制位,其值为[10],说明此时的系统时钟确实来自 PLL 的输出。

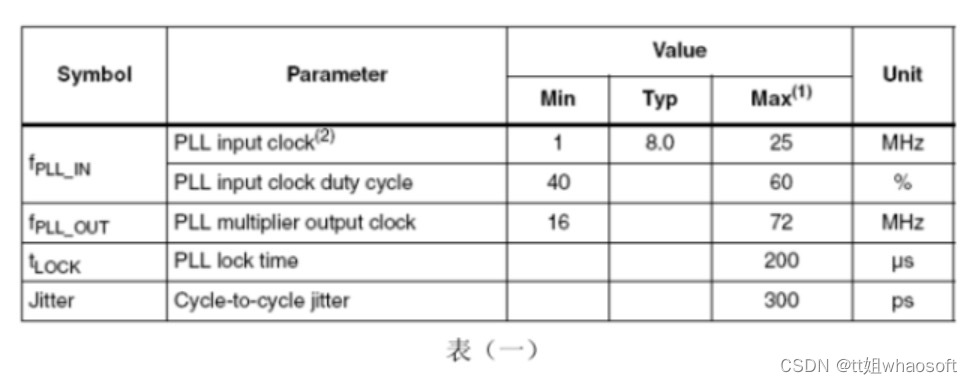

从 STM32F103VD 的数据手册中查找 PLL 相关的参数如表(一):

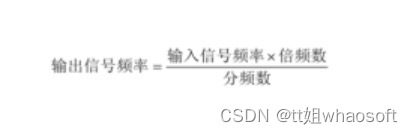

其中,PLL 的输出频率范围是 16MHz – 72MHz。也就是说,PLL 在处于相位锁定的状态下,可以输出 16MHz – 72MHz 的时钟信号。而当输入信号频率过低而导致输出信号频率低于 16MHz 时,将可能处于失锁的状态。在这状态下,它的输出信号的频率与输入信号的频率之间,不一定符合所设定的倍频与分频关系。更确切的说,不能通过公式:

得出“输入信号频率为零时,输出信号频率也为零”这样的结论。这一点与实测的结果相吻合。

结论:

STM32 的 PLL 在没有输入信号的情况下,仍能维持在最低的频点处振荡,产生输出。以至,CPU 及其它外设仍能在 PLL 送出的时钟的驱动下运行。所以,通过判断有无时钟来驱动 CPU 执行指令的方式来判断 HSE 是否失效是行不通的。

处理:

对软件做如下修改:

1. 在软件的初始化部分,开启 STM32 的 CSS 功能;

2. 修改 NMI 中断服务程序,加入 while(1) 陷阱语句;

开启 CSS 功能后,当 HSE 失效时,STM32 会自动开启 HSI,并将系统时钟的来源切换到HSI 的输出,同时产生 NMI 中断。这样,程序的流程将停留在 NMI 中而不能产生复位片外的看门狗的脉冲。当片外看门狗溢出后,就会复位 STM32,使其恢复到正常驻的状。

建议:

STM32 中的 CSS 功能是专门为检测和处理 HSE 失效而设计的。但该功能在 STM32 复位后是被禁止的,须要软件对其使能才会发挥作用。当 CSS 单元检测到 HSE 失效时,它会使能 HSI,并将系统时钟切换到 HSI。同时,它会关闭 HSE,如果 PLL 的输入信号来自 HSE的输出,它也会关闭 PLL。CSS 单元在做时钟调整的同时,也会产生一个 NMI 中断请求,和一个送给高级定时器的刹车信号。NMI 中断请求会产生一个 NMI 中断,以便用户程序可以在中断服务程序中做紧急处理,而刹车信号则是使高级定时器进入刹车状态,以防止由其控制的电机驱动桥臂由于失去控制而过流。用户程序可以在 NMI 中断服务程序中尝试恢复 HSE 及 PLL 的功能,也可以使用陷阱让程序的流程停留在服务程序中,从而等待看门狗复位整个系统。

三、详解STM32的时钟系统

连接上文哦

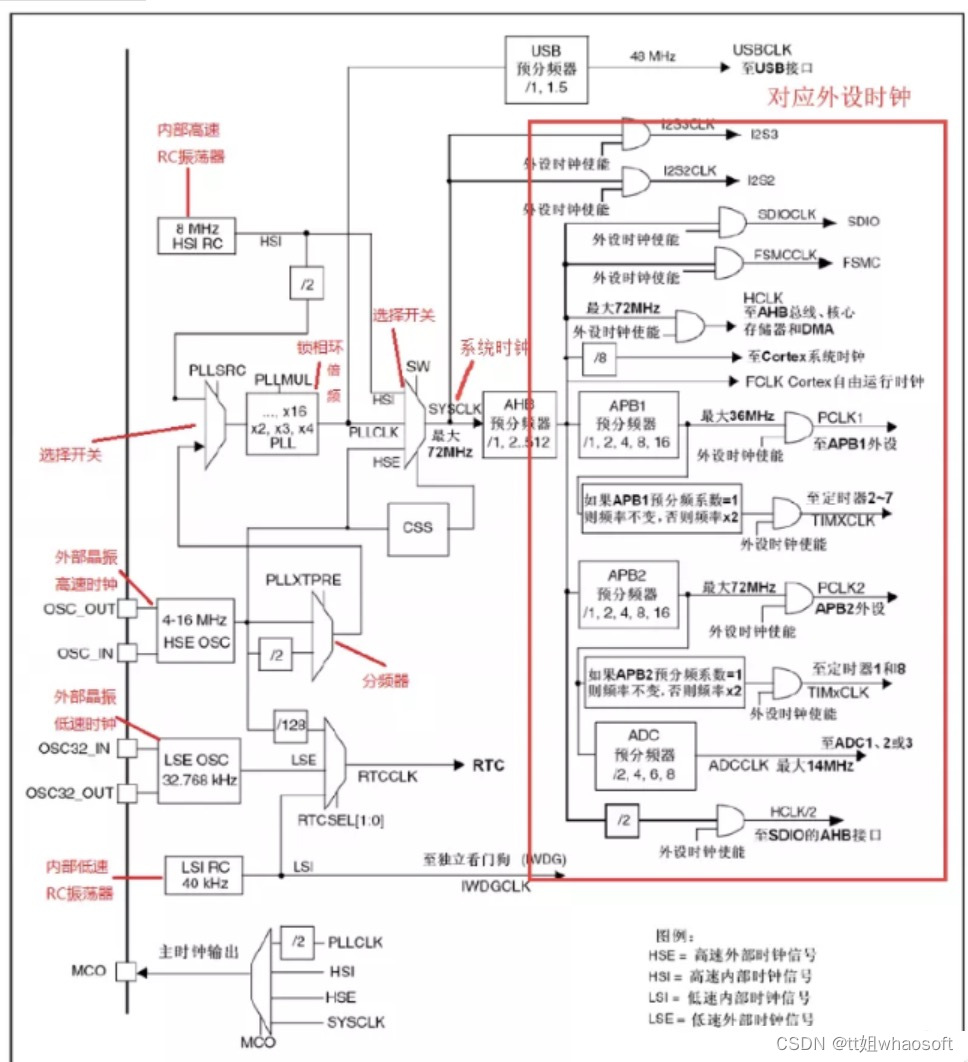

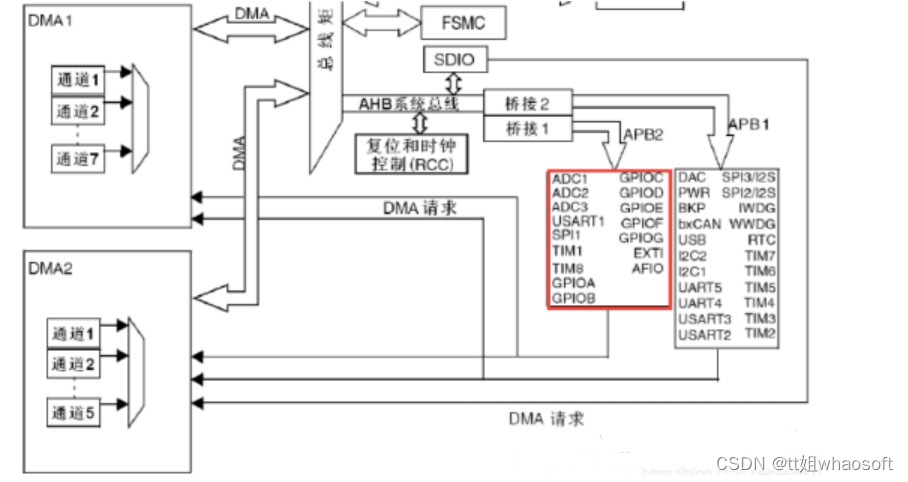

STM32的时钟树

时钟信号推动单片机内各个部分执行相应的指令,时钟就像人的心跳一样。

STM32本身十分复杂,外设非常多,任何外设都需要时钟才能启动,但并不是所有的外设都需要系统时钟那么高的频率,如果都用高速时钟势必造成浪费。同一个电路,时钟越快功耗越大、抗电磁干扰能力越弱。复杂的MCU采用多时钟源的方法来解决这些问题。如下图,是STM32的时钟系统框图。

如上图左边的部分,看到STM32有4个独立时钟源,HSI、HSE、LSI、LSE。

- HSI是高速内部时钟,RC振荡器,频率为8MHz,精度不高。

- HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

- LSI是低速内部时钟,RC振荡器,频率为40kHz,提供低功耗时钟。

- LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

时钟树的右边红色框中,则是系统时钟通过AHB预分频器,给相对应的外设设置相对应的时钟频率。

其中LSI、LSE是作为IWDGCLK(独立看门狗)时钟源和RTC时钟源使用。而HSI、HSE以及PLLCLK经过分频或者倍频作为系统时钟SYSCLK来使用。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。通过倍频之后作为系统时钟的时钟源。

配置时钟

默认时钟

Keil编写程序是默认的时钟为72Mhz,其实是这么来的:

外部高速晶振HSE提供的8MHz(大小与电路板上的晶振相关)通过PLLXTPRE分频器后,进入PLLSRC选择开关,进而通过PLLMUL锁相环进行倍频(x9)后,为系统提供72MHz的系统时钟SYSCLK。之后是AHB预分频器对时钟信号进行分频,然后为低速外设提供时钟。

内部RC振荡器HSI为8MHz,2分频后是4MHz,进入PLLSRC选择开关,通过PLLMUL锁相环进行倍频(最大x16)后为64MHz。

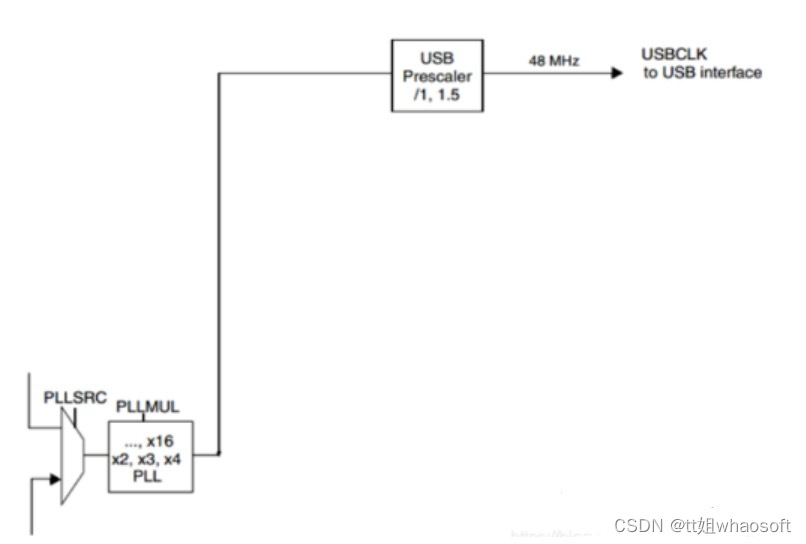

USB时钟

如上图,STM32的USB时钟不能超过48MHz,因此如果时钟源为72MHz,就需要进行1.5分频。

如果时钟源为48MHZ,则进行1分频即可。

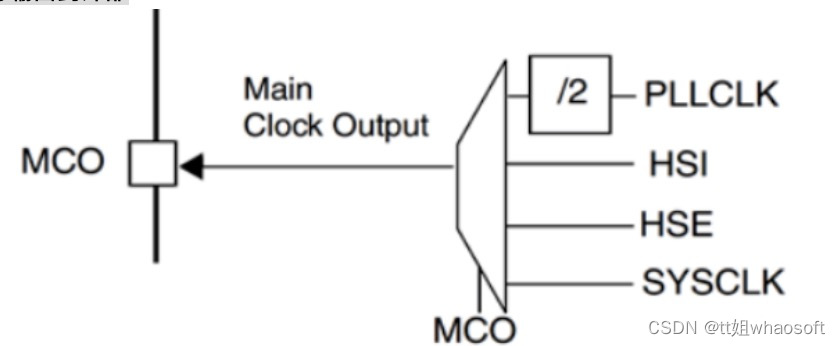

把时钟信号输出到外部

STM32可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟,可以把时钟信号输出供外部使用。

AHB分频器

如时钟树图右边的部分,系统时钟通过AHB分频器给外设提供时钟。从左到右可以简单理解为:

系统时钟->AHB分频器->各个外设分频倍频器->外设时钟的设置。

右边部分为:系统时钟SYSCLK通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。其中AHB分频器输出的时钟送给5大模块使用:

- 内核总线:送给AHB总线、内核、内存和DMA使用的HCLK时钟。

- Tick定时器:通过8分频后送给Cortex的系统定时器时钟。

- I2S总线:直接送给Cortex的空闲运行时钟FCLK。

- APB1外设:送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给通用定时器使用。该倍频器可选择1或者2倍频,时钟输出供定时器2-7使用。

- APB2外设:送给APB2分频器。APB2分频器可选择1、2、4、8、16分频,其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给高级定时器。该倍频器可选择1或者2倍频,时钟输出供定时器1和定时器8使用。另外,APB2分频器还有一路输出供ADC分频器使用,分频后送给ADC模块使用。ADC分频器可选择为2、4、6、8分频。需要注意的是,如果APB预分频器分频系数是1,则定时器时钟频率(TIMxCLK)为PCLKx。否则,定时器时钟频率将为 APB 域的频率的两倍:TIMxCLK = 2xPCLKx。

APB1和APB2的对应外设

F1系列中,APB1上面连接的是低速外设,包括电源接口、备份接口、CAN、USB、I2C1、I2C2、USART2、USART3、UART4、UART5、SPI2、SP3等。

APB2上面连接的是高速外设,包括UART1、SPI1、Timer1、ADC1、ADC2、ADC3、所有的普通I/O口(PA-PE)、第二功能I/O(AFIO)口等。

具体可以在stm32f10x_rcc.h中查看外设挂在哪个时钟下。

时钟监视系统(CSS)

另外,STM32还提供了一个时钟监视系统(CSS),用于监视高速外部时钟(HSE)的工作状态。倘若HSE失效,会自动切换(高速内部时钟)HSI作为系统时钟的输入,保证系统的正常运行。

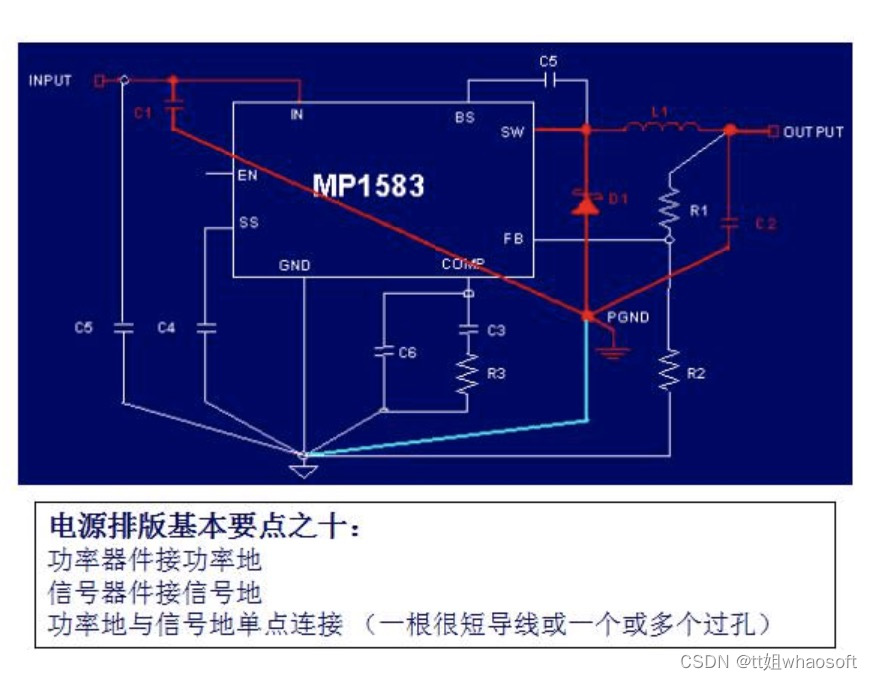

四、10个PCB布板基本法则

这里都是图哦

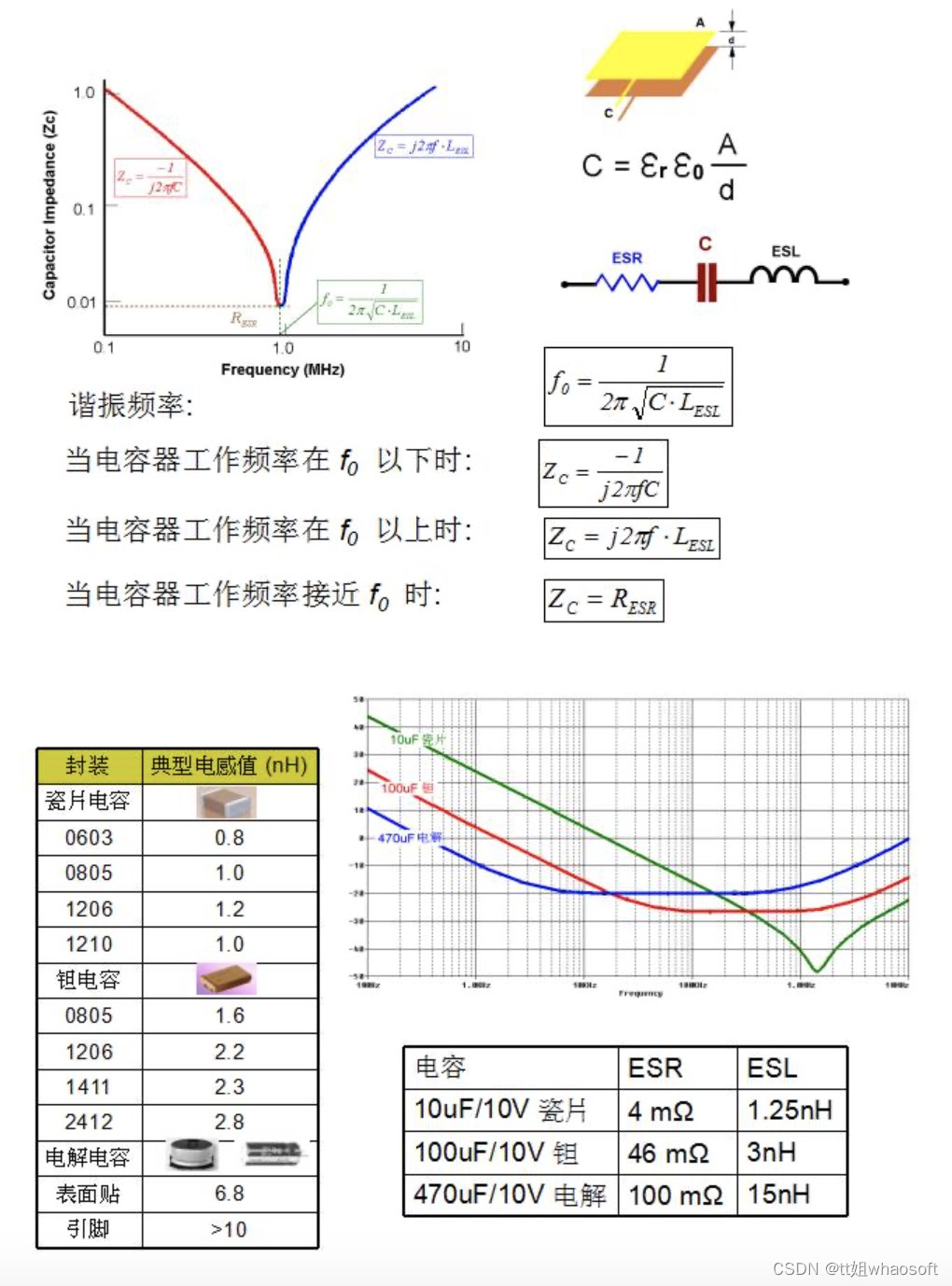

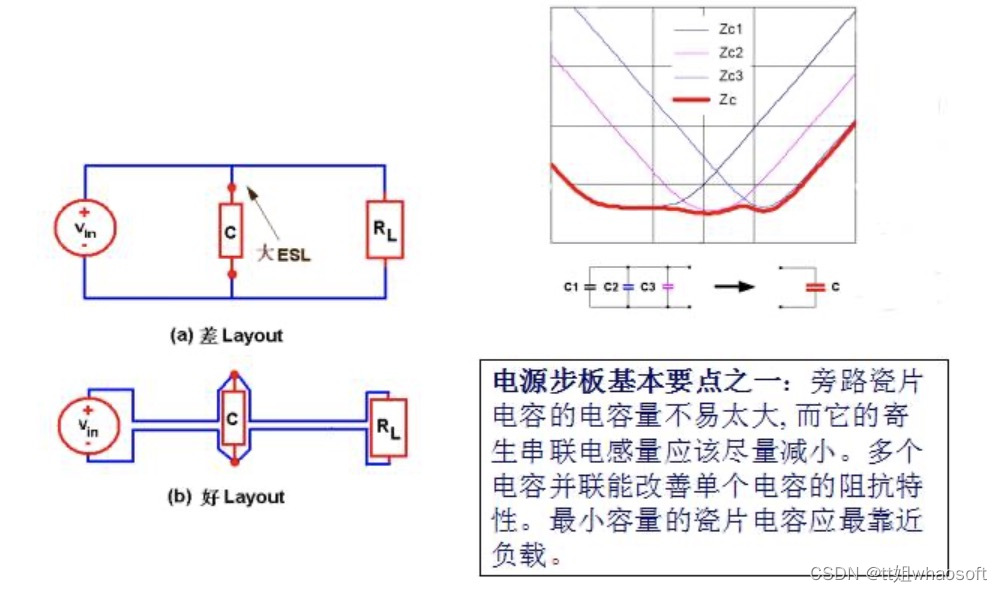

电容模型

电容并联高频特性

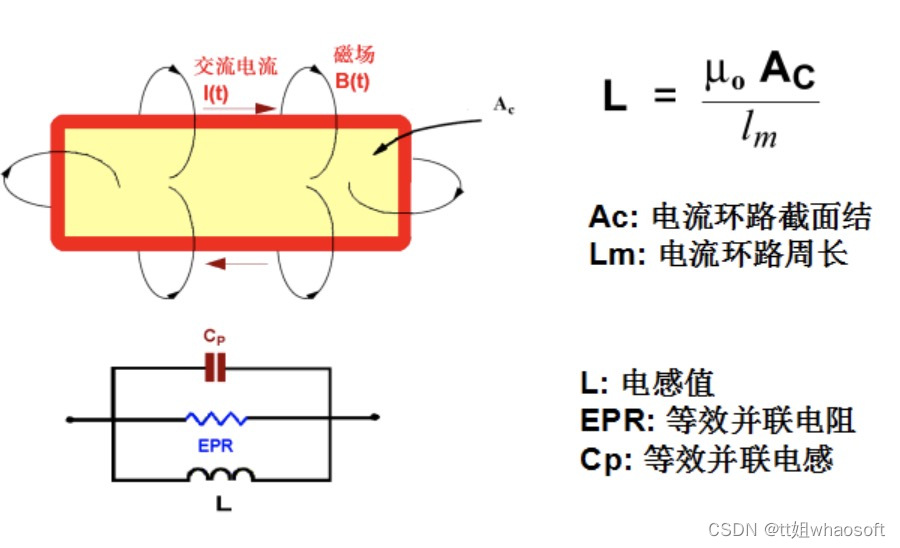

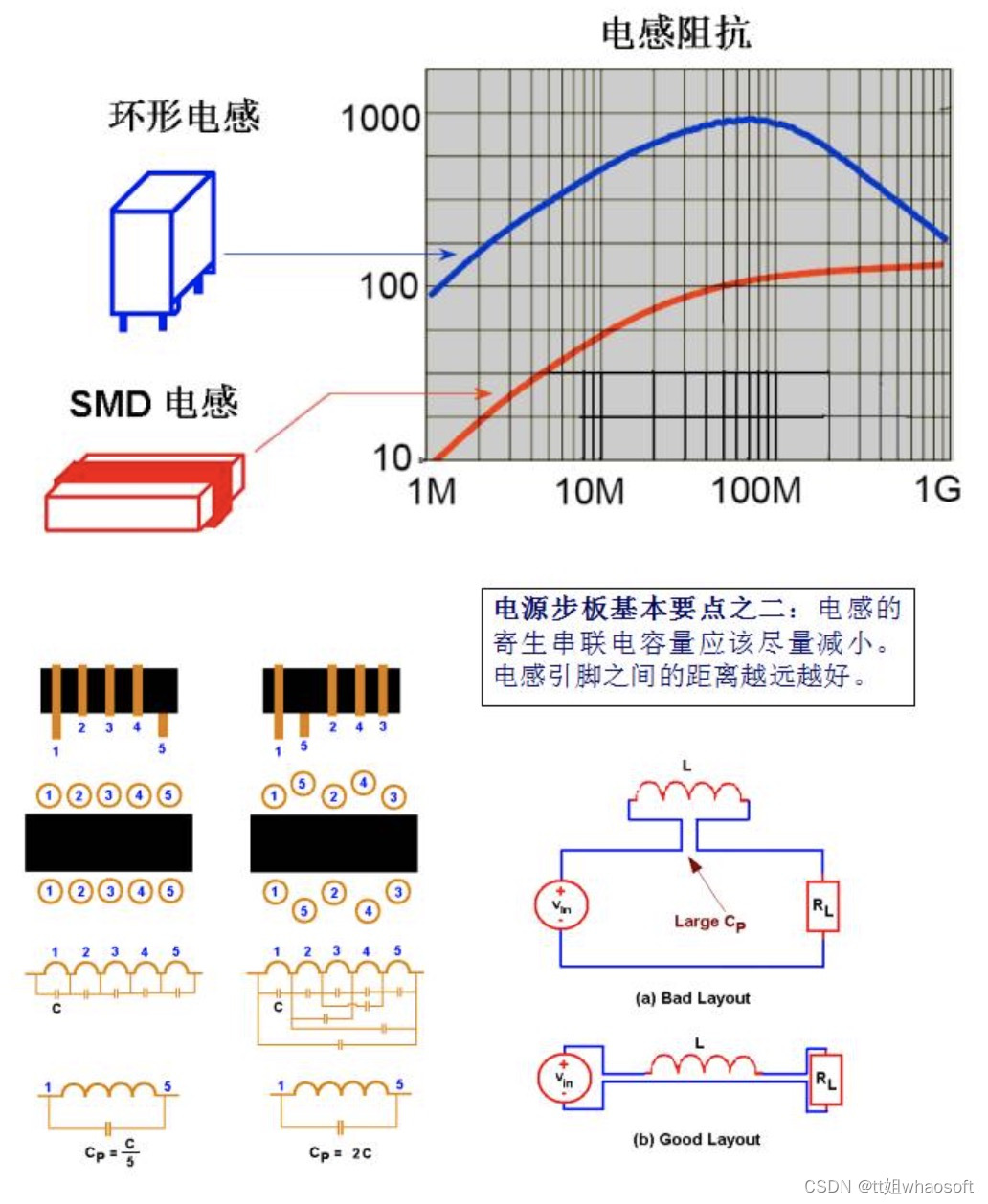

电感模型

电感特性

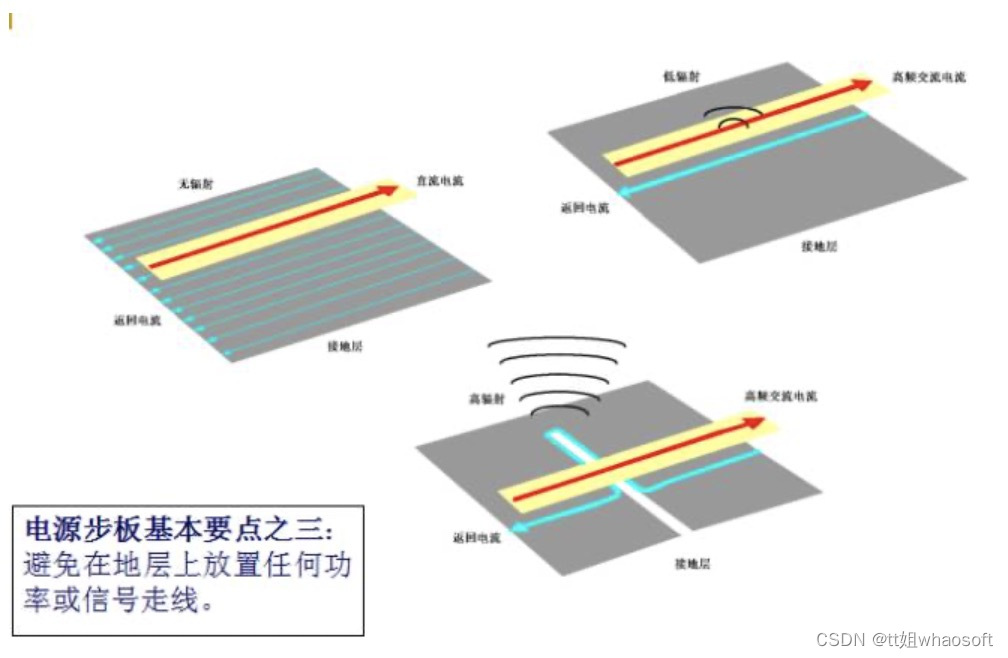

镜象面概念

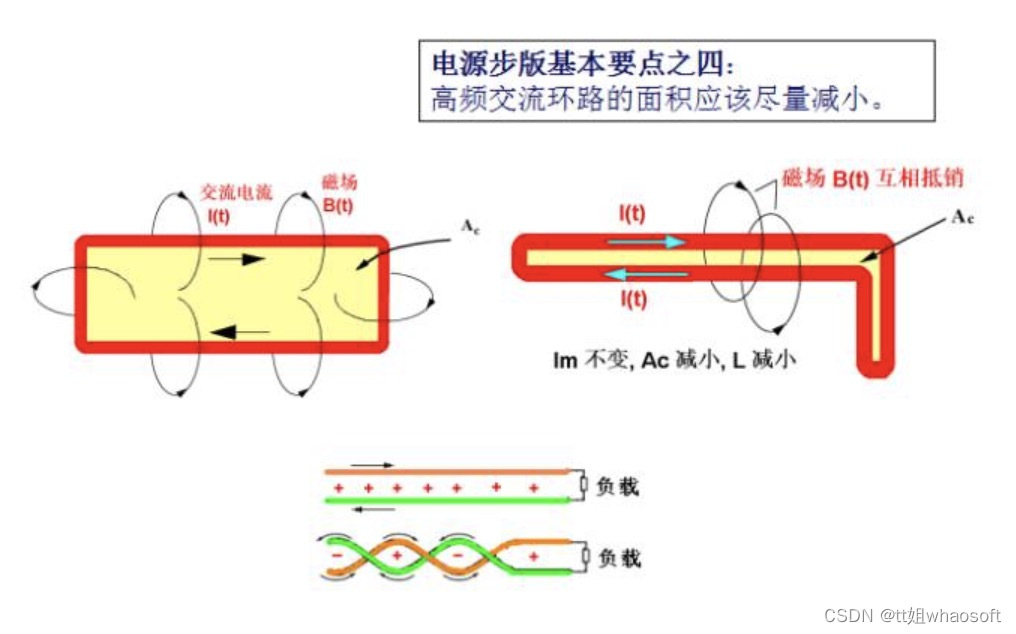

高频交流电流环路

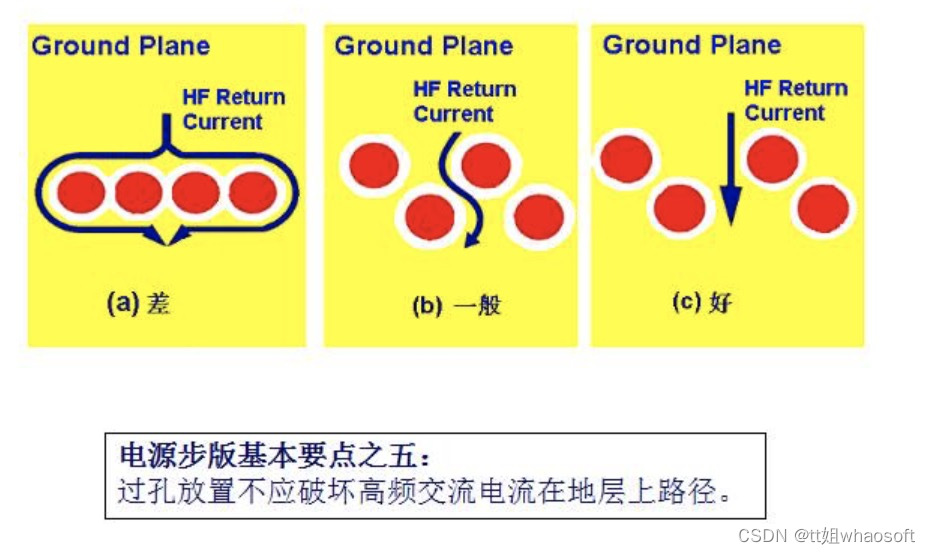

过孔 (VIA) 的例子

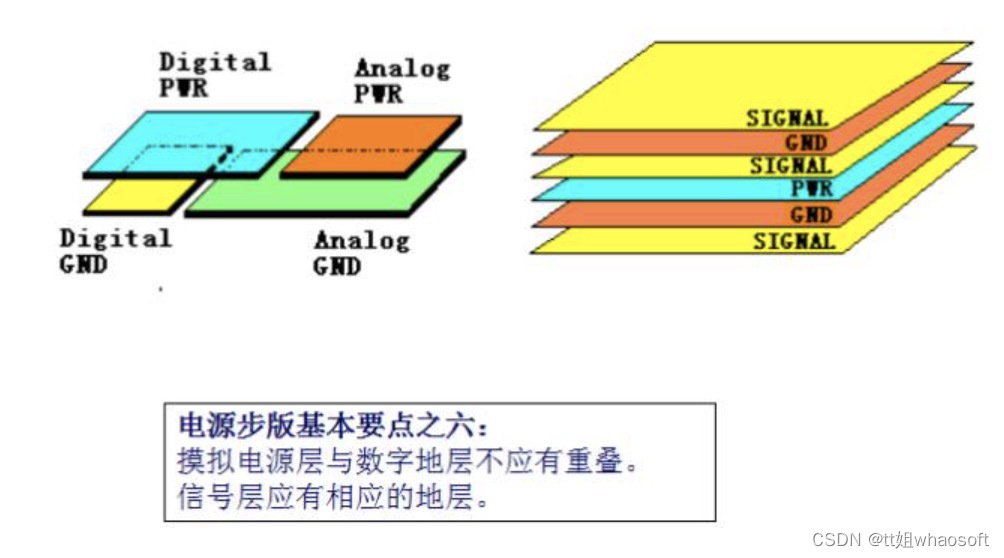

PCB板层分割

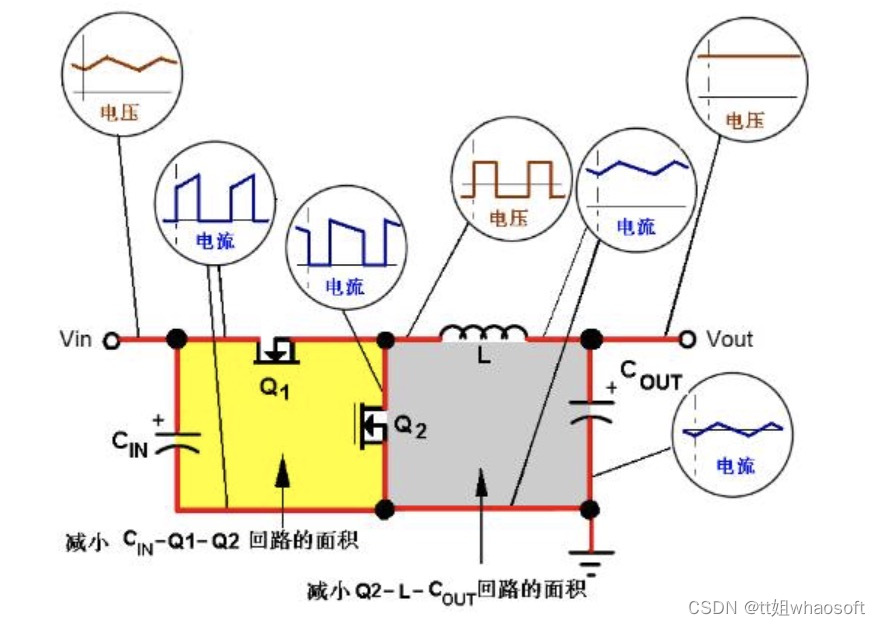

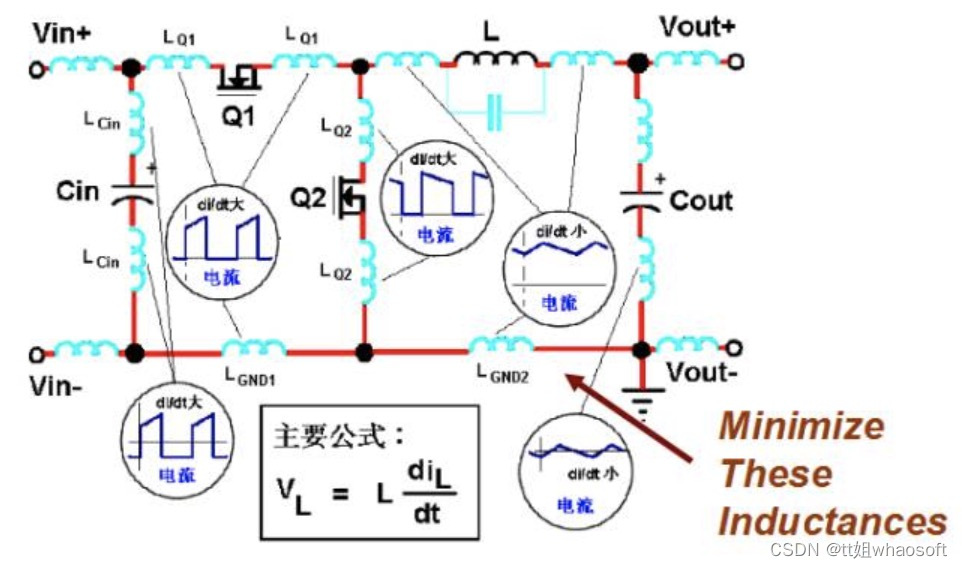

降压式(BUCK)电源:功率部分电流和电压波形

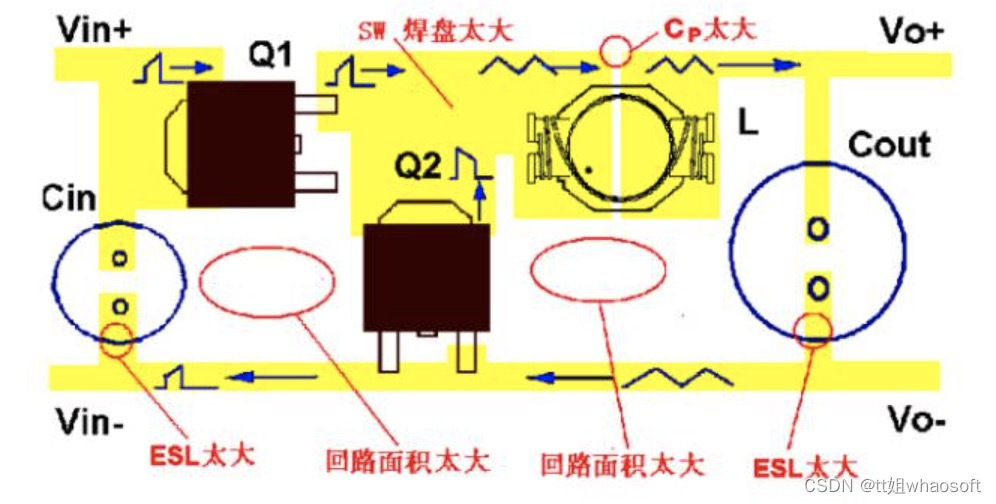

降压式电源排版差的例子

电路等效图

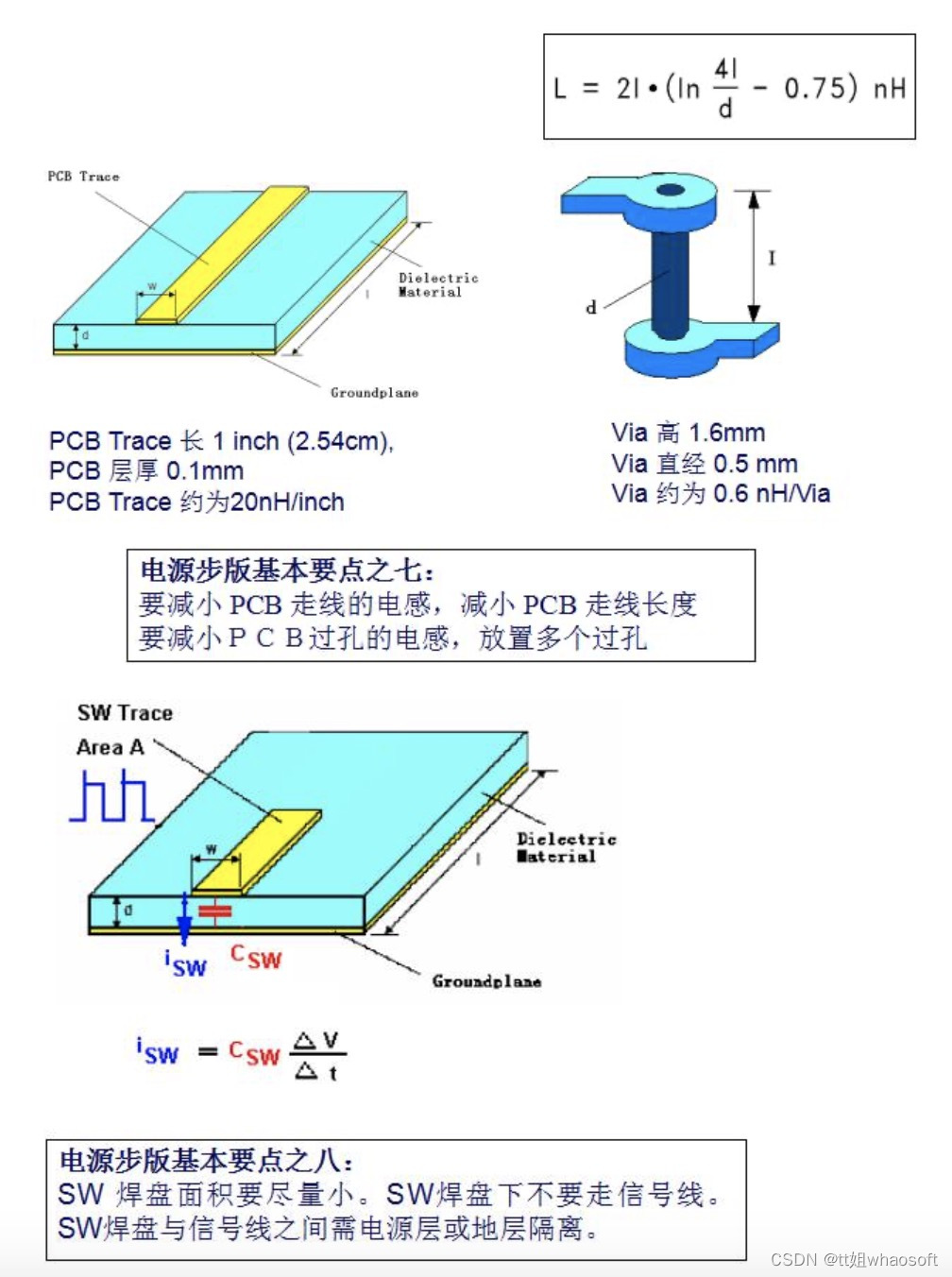

PCB Trace - Via 电感估算

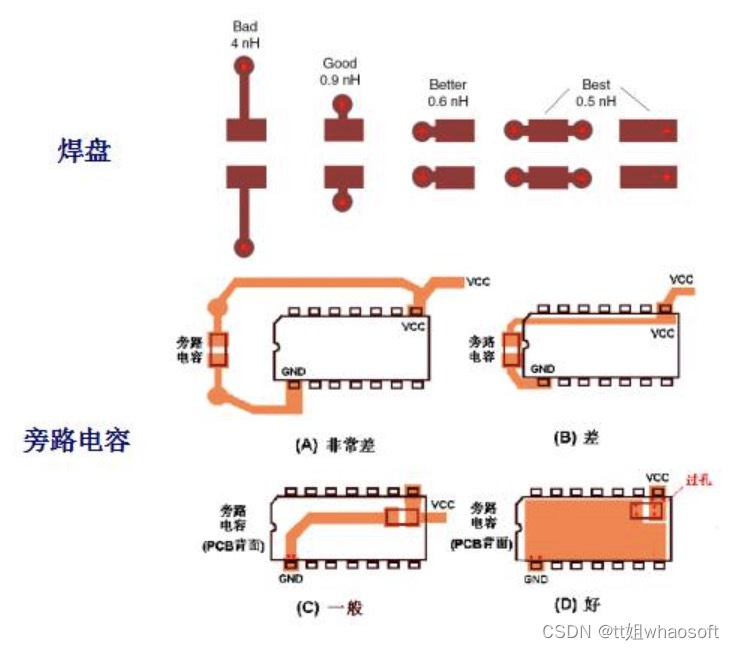

焊盘(PAD)和旁路电容的放置

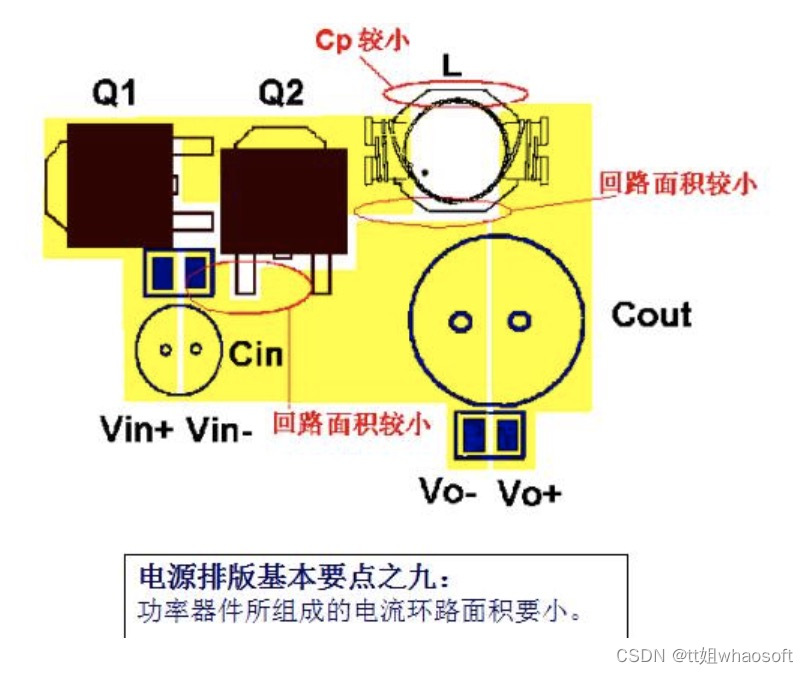

降压式电源排版的例子

降压式电源排版的例子

五、 早期555定时器芯片

由模拟 IC 奇才 Hans Camenzind 设计的 555 被称为有史以来最伟大的芯片之一。据说是世界上最畅销的集成电路,已售出数十亿。

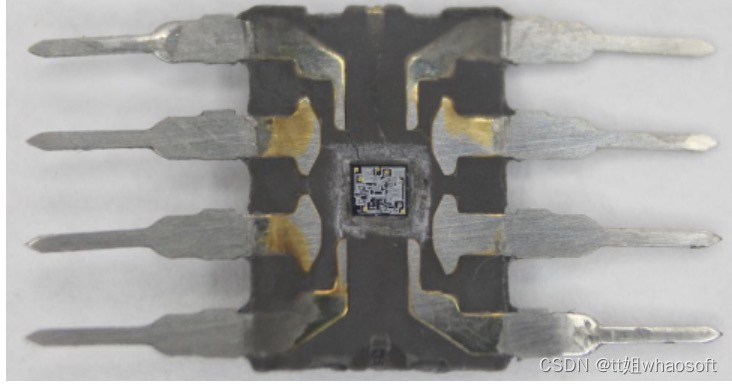

一个带有 Signetics 标志的 8 针 555 定时器。它没有 555 标签,而是标有“52B 01003”和 7304 日期代码,表示 1973 年的第 4 周。

乏味地打磨环氧树脂封装以露出芯片(下图),并确定芯片是 555 定时器。Signetics 在 1972 年年中发布了 555 定时器,下面的芯片有一个 1973 年 1 月的日期代码(7304),所以它一定是最早的 555 定时器之一。奇怪的是,它没有标为 555,所以它可能是原型或内部版本。

我拍摄了详细的模具照片,在这篇博文中进行了讨论。

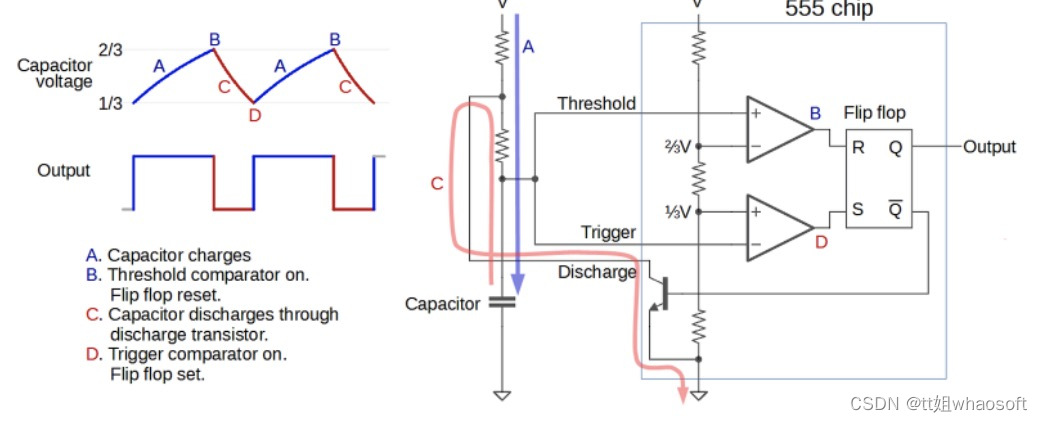

555 定时器的封装被打磨,露出硅芯片,中间的小方块。

555 定时器有数百种应用,从定时器或锁存器到压控振荡器或调制器的任何操作。下图说明了 555 定时器如何作为一个简单的振荡器工作。在 555 芯片内部,三个电阻形成一个分压器,产生 1/3 和 2/3 的电源电压的参考电压。外部电容器将在这些限制之间充电和放电,从而产生振荡。更详细地说,电容器将通过外部电阻器缓慢充电 (A),直到其电压达到 2/3 参考电压。在该点 (B),上(阈值)比较器关闭触发器并关闭输出。这会打开放电晶体管,使电容器 (C) 缓慢放电。当电容器上的电压达到 1/3 参考电压 (D) 时,较低(触发)比较器打开,设置触发器和输出,循环重复。电阻器和电容器的值控制时间,从微秒到几小时。

显示 555 定时器如何作为振荡器工作的图表。在 555 定时器的控制下,外部电容器通过外部电阻器进行充电和放电。

总而言之,555 定时器的关键组件是检测电压上限和下限的比较器、设置这些限制的三电阻分压器以及跟踪电路是充电还是放电的触发器。555 定时器还有两个我上面没有提到的引脚(复位和控制电压),它们可用于更复杂的电路。

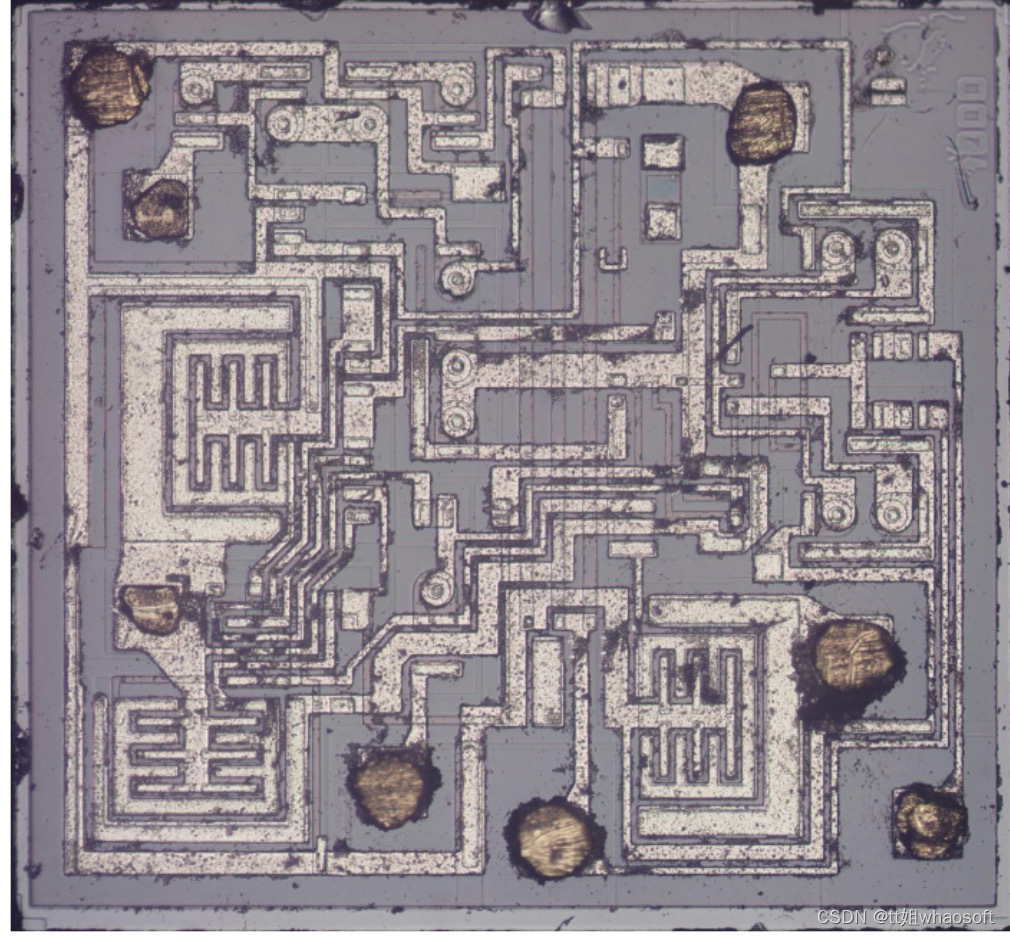

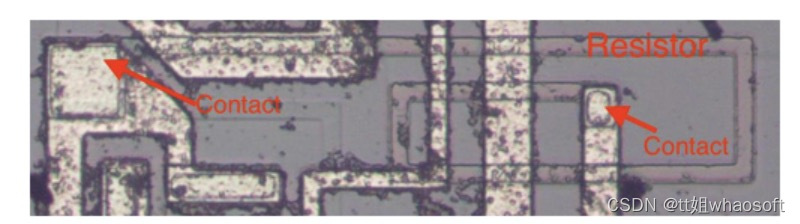

从显微镜图像的合成中创建了下面的照片。在硅的顶部,一层薄薄的金属连接芯片的不同部分。这种金属在照片中以浅色痕迹清晰可见。在金属下方,一层薄薄的玻璃状二氧化硅层在金属和硅之间提供绝缘,除了二氧化硅中的接触孔允许金属连接到硅的地方。在芯片的边缘,细线将金属焊盘连接到芯片的外部引脚。

如上,555 计时器的模具照片。

芯片上不同类型的硅更难看到。芯片的区域用杂质处理(掺杂)以改变硅的电特性。N 型硅具有过量的电子(负),而 P 型硅缺乏电子(正)。在照片中,这些区域显示为略有不同的颜色,周围有细黑色边框。这些区域是芯片的组成部分,形成晶体管和电阻器。在windows中,保存的时候先另存在桌面,再拖进去覆盖即可!

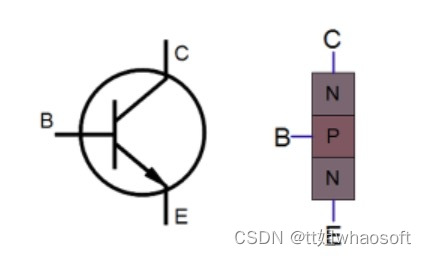

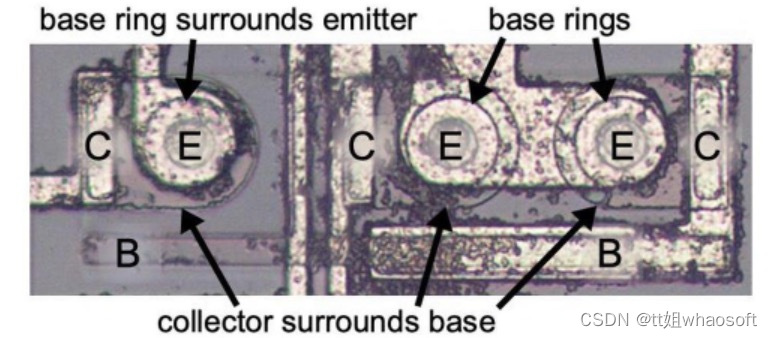

晶体管是芯片中的关键元件。555 定时器使用 NPN 和 PNP 双极晶体管。如果您研究过电子学,您可能已经看过如下图所示的 NPN 晶体管图,显示了晶体管的集电极 (C)、基极 (B) 和发射极 (E),晶体管被图示为P硅夹在两个对称的N硅层之间,NPN 层构成 NPN 晶体管。事实证明,芯片上的晶体管看起来不像这样,而且基极通常甚至不在中间!

如上,NPN 晶体管的原理图符号,以及其内部结构的简化图。

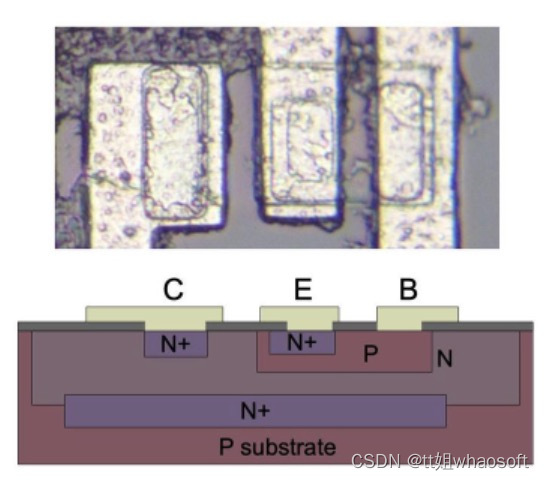

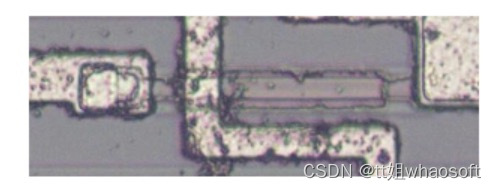

下面的照片显示了 555 中的一个晶体管的特写,因为它出现在芯片上。硅中稍有不同的色调表明已掺杂形成 N 和 P 区域的区域。白色区域是硅顶部芯片的金属层 - 这些形成连接到集电极、发射极和基极的导线。

如上图,裸片上 NPN 晶体管的结构。

照片下方是一个横截面图,说明了晶体管的构造方式。除了你在书中看到的 NPN 之外,还有很多其他东西,但如果你仔细观察“E”下方的垂直横截面,你会发现形成晶体管的 NPN。发射极 (E) 线连接到 N+ 硅。其下方是连接到基极触点 (B) 的 P 层。在其下方是(间接)连接到收集器(C)的 N+ 层。6 晶体管被 P+ 环包围,将其与相邻组件隔离。

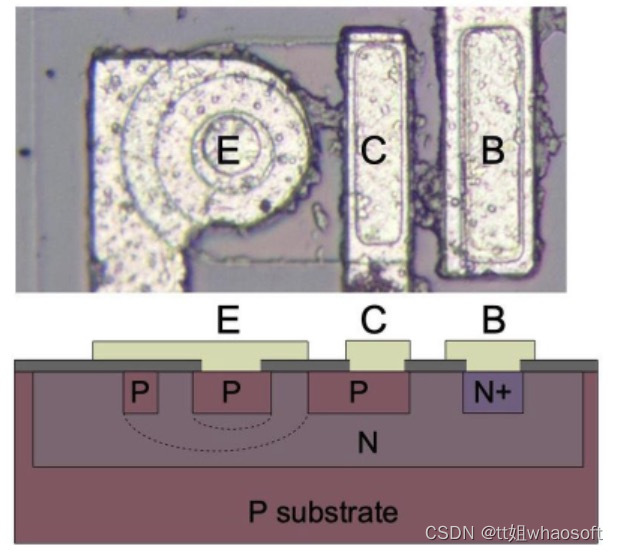

在IC内部的PNP晶体管:

如上图,555定时器芯片中的PNP晶体管。标注了集电极(C)、发射极(E)和基极(B)的连接,以及N和P掺杂硅。基极围绕发射极形成一个环,集电极围绕基极形成一个环。

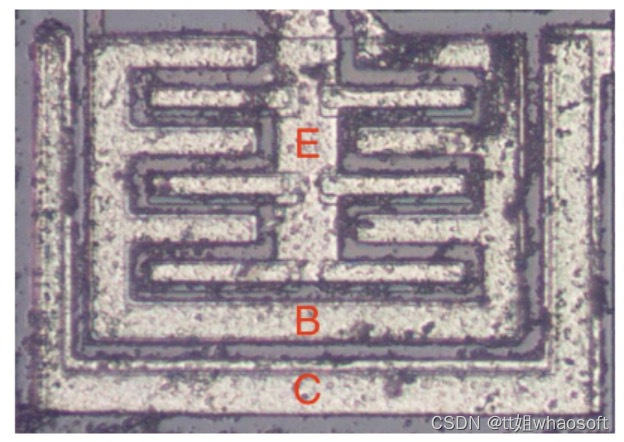

555中的输出晶体管比其他晶体管大得多,并且具有不同的结构,以产生高电流输出。下面的照片显示了输出晶体管之一。注意被大集电极包围的发射极和基极的多个互锁“手指”。

如上图,555定时器芯片中的大电流NPN输出晶体管。集电极(C)、基极(B)和发射极(E)被标记。

电阻器是如何在硅中实现的?

电阻器是模拟芯片的关键部件。不幸的是,IC 中的电阻器很大且不准确。不同芯片的电阻可能相差 50%。因此,模拟 IC 的设计只有电阻的比率很重要,而不是绝对值,因为比率几乎保持不变。

如上,555定时器内部的电阻。电阻器是两个金属触点之间的一条 P 硅。

上面的照片显示了 555 中的一个 10KΩ 电阻器,它由一条 P 硅(粉灰色)形成,在两端与金属线接触。其他金属线穿过电阻器。电阻器具有螺旋形状,以使其长度适合可用空间。下面的电阻是一个 100KΩ 的夹点电阻。夹层电阻器顶部的 N 硅层使导电区域更薄(即夹住它),形成更高但不太准确的电阻。

555定时器内部的收缩电阻器。电阻器是两个金属触点之间的一条P硅。顶部的N层夹住电阻,增加电阻。垂直金属线穿过该电阻器。

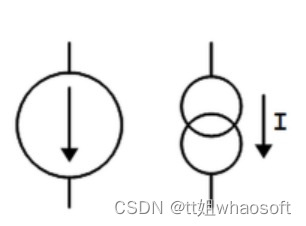

有一些子电路在模拟 IC 中很常见,但起初可能看起来很神秘。电流镜就是其中之一。如果您看过模拟 IC 框图,您可能已经看到下面的符号,指示电流源,并想知道电流源是什么以及为什么要使用它。这个想法是你从一个已知的电流开始,然后你可以用一个简单的晶体管电路,电流镜“克隆”电流的多个副本。

如上图,电流源的原理图符号。

以下电路显示了如何用两个相同的晶体管实现电流镜。参考电流流经右侧的晶体管。(在这种情况下,电流由电阻设定。)由于两个晶体管具有相同的发射极电压和基极电压,它们产生相同的电流,因此右边的电流与左边的参考电流相匹配。

如上,电流镜电路,右边的电流复制左边的电流。

电流镜的一个常见用途是替换电阻器。如前所述,IC 内部的电阻器既大又不准确,不便之处。尽可能使用电流镜而不是电阻器来节省空间。此外,与两个电阻器产生的电流不同,电流镜产生的电流几乎相同。

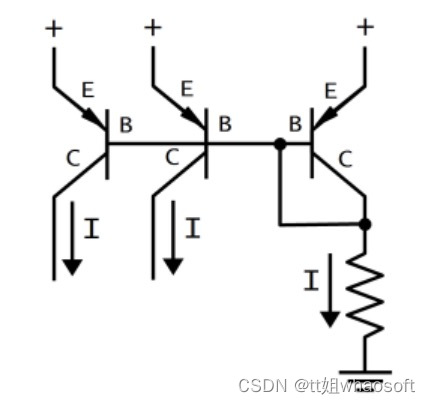

如上图,三个晶体管在555定时器芯片中形成一个电流镜。它们共用同一个基极,两个晶体管共用发射极。

上述三个晶体管构成一个具有两个输出的电流镜。注意,三个晶体管共享基极连接,连接到右边的集电极,右边的发射极连接在一起。在原理图中,右侧的两个晶体管被绘制为单个双集电极晶体管Q19。

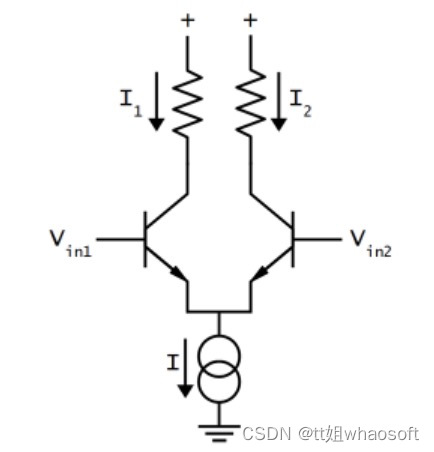

要了解的第二个重要电路是差分对,它是模拟 IC 中最常见的双晶体管子电路。 您可能想知道比较器如何比较两个电压,或者运算放大器如何减去两个电压。这是差分对的工作。

如上,简单差分对电路原理图。电流源通过差分对发送固定电流I。如果两个输入相等,则电流均分。

上面的示意图显示了一个简单的差分对。底部的电流源提供固定电流 I,该电流在两个输入晶体管之间分配。如果输入电压相等,则电流将平均分成两个分支(I1 和 I2)。如果其中一个输入电压比另一个高一点,则相应的晶体管会以指数方式传导更多的电流,因此一个分支获得更多电流,而另一个分支获得更少。一个小的输入差异足以将大部分电流引导到“获胜”分支,从而打开或关闭比较器。555 芯片使用一个差分对作为阈值比较器,另一对作为触发比较器。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?