opensbi下的riscv64裸机编程2(中断与异常)

1.本文说明

2.riscv特权模式下的异常

2.1 CSPs

2.2 异常开关的寄存器

2.3 与中断相关的指令

3.中断测试

3.1 设置中断向量表

3.2 开启中断设置

3.3 初始化timer

3.4 开启中断

3.5 中断处理

4.测试及校验

5.总结

1.本文说明

任何时候,中断和异常的产生都是十分值得关注的,这些将破坏程序原有的执行逻辑。按照芯片的设计来说,中断和异常大致上可以分为三类异常(Exception)、陷入(Trap)、外部中断(Interrupt)。

- 异常(Exception)

在一条指令执行的过程中发生了错误,可以通过异常处理函数进行处理,最常见的异常包括无效的内存地址访问、非法指令异常、缺页异常等等。当发生这些异常后可以进行处理。

- 陷入(Trap)

主动的让其进入异常处理函数,常见的是系统调用syscall。而在riscv上为ecall或者进入断点的ebreak。

- 外部中断(Interrupt)

一般由外部事件触发,比如定时器中断、GPIO中断等。这些异常是不可预知的。

对于一般的中断处理流程,进入中断后需要进行上下文的保存与恢复。

2.riscv特权模式下的异常

涉及到中断和异常,RISCV的特权模式是不能绕开的。在RISCV中,无论在任何模式发生的异常,硬件线程都会将控制权交给M-Mode的异常处理程序。然而对于类Unix的操作系统来说,异常都是由操作系统来处理。而操着系统运行的模式是S-Mode,所以RISCV也可以选择将异常重新导向到S-Mode,也支持异常委托机制(Machine Interrupt Delegaintion)将异常直接通过S-Mode进行处理,这样可以大大的增加操作系统的灵活性。

一般来说M-Mode是必须实现的,S-Mode也一般会有,而U-Mode是选择性扩展的。目前的RISCV芯片中例如蜂鸟的E203与K210都只支持了RISCV架构中的Machine Mode。

2.1 CSPs

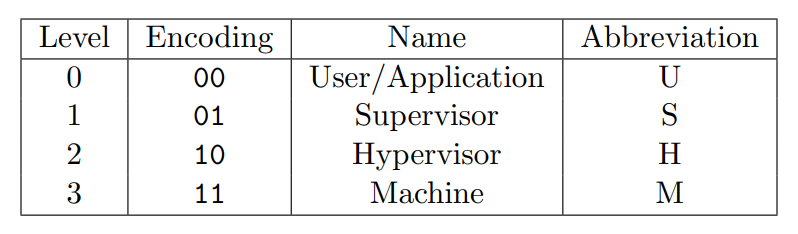

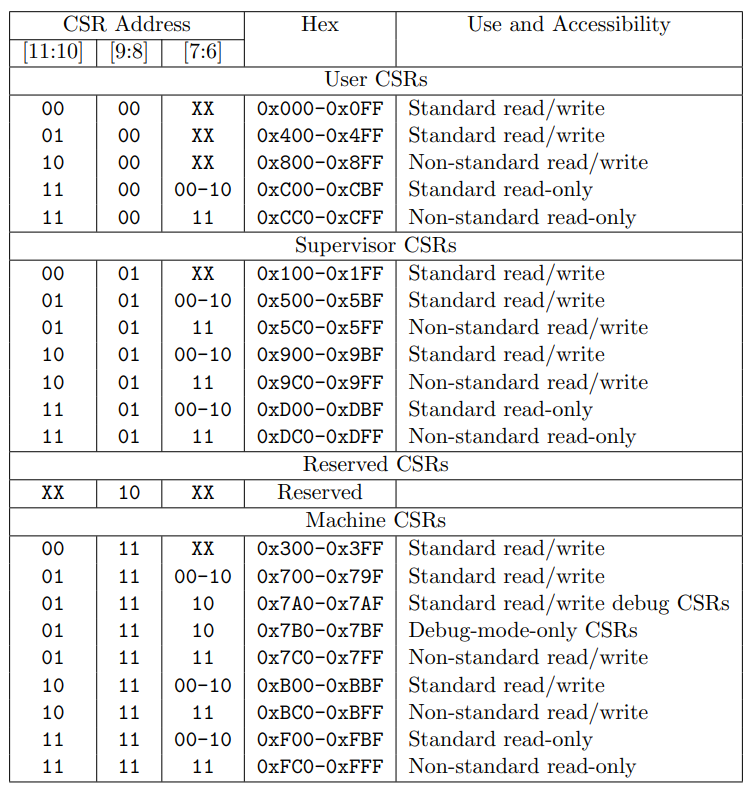

实际上RISCV在实现系统指令集的时候,是支持多种模式的扩展的,这一系列的指令集通过Control and Status Registers (CSRs)来进行控制。

CSR地址是扩展了12位,也就是可以设计最大4096个指令。

通过下面的网站可以看到当前CSRs的实现状态。

http://www.five-embeddev.com/quickref/csrs.html

这里只针对S-Mode下的异常处理进行分析,M-Mode下的异常处理类似。

| Name | Number | Feature/Extensions | Description |

|---|---|---|---|

| sepc |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

786

786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?