前文简单介绍了Sublime Text 3的下载安装、几款基本的插件以及与Vivado的关联使用,这次就介绍下几款真的可以提升编写Verilog代码效率的插件!

虽说网上已有很多相关文章,但是大多未详细介绍插件使用方法,所以本文就详细介绍一下!

(当然,使用其他编辑器也可能达到同样效果)

之前介绍了Package Control、ChineseLocalizations、Verilog、ConvertToUTF8四款插件,这里就不再多说,至于插件的安装方法可详见前文:

十二点过九分:Sublime与Verilog【一】:从安装到使用,提高FPGA开发效率!zhuanlan.zhihu.com

几款比较实用的插件

- Snippet Maker

对于Verilog搬砖工来说,最需要的就是代码自动补全功能,毕竟像是always、generate等语句一敲就是一大段,这谁受得了。当然在前面的Verilog插件已经实现了一些必要语句的补全,但若想一键搭个状态机的框架出来、或一键生成常用的代码结构,前面的插件似乎就无能为力了,而Sublime的Snippet(代码片段)功能可以很好的实现想要的效果。

对于Snippet功能和编写不多介绍,可详见:手把手教你写Sublime中的Snippet

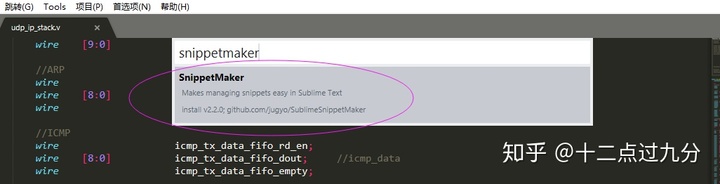

推荐一个快速编写Snippet的插件“Snippet Maker”,在install package中可以下载安装,如下图所示:

该插件的具体使用方式为:

- 选中一段代码片段,比如选择always块;

- 使用快捷键“ctrl + shift + p”进入控制台并输入“make snippet”进行代码片段的生成;

- 在界面下方的Trigger框中输入触发命令并回车(即之后输入该命令即可调出该代码片段),比如为al;

- 在界面下方的Description框中输入该代码片段的描述并回车,比如为alwaysblock;

- 在界面下方的Scope框中输入“source.verilog”并回车(即在Verilog下触发该片段);

- 在界面下方的File Name框中输入该代码片段的保存名称并回车(注意需要以sublime-snippet结尾),比如al.sublime-snippet;

上述操作可如下动图所示:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1128

1128

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?