USRP FPGA

EP1C12 的特性:

LEs

12,060

M4k RAM blocks (128 x 36 bits)

52

Total RAM

bits

239,616

PLLs

2

Maximum

user I/O pins

173

用硬件语言 Verilog 描述FPGA内部功能,用Altera's免费网络版

run Quartus II under Linux 而不需 Windows - YMMV.

FPGA 运行在 64MHz

时钟下,其所有内部部件同全球时钟同步。由于其极高的时钟,所以FPGA内部部件都被极高的流水线规划以求达到极高速度效果。

接收链路

AD9862 -> CORDIC -> CIC 抽取滤波器 (4阶的, 可编程抽取速率 [4,128]) -> 半带数字抽取滤波器 (固定抽头系数 2) -> RX

FIFO.

这提供了所有在 [8,256]范围内所有可能的偶数抽取速率。

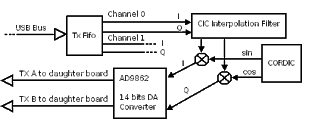

发射链路

这里是一个发射链路的大概原理框图:

有两路时钟:一个用于USB总线(上达 FIFO) 一个用于发射链路自身。 频道0具有本地环回功能。级联积分梳状滤波器(CIC)

速率由寄存器 FR_INTERP_RATE控制。CORDIC 变换在svn HEAD中被禁止.

到

USB 接口

描述主机(计算机)如何同 USRP 通信。

FPGA

寄存器

寄存器被分为三类 - 公用(common), 标准(standard),

及自定义(custom)。寄存器,除三个可读标准寄存器外,仅仅是把数据映射到计算机用于读取目的用的。

Writable Address Range: 0 - 31 (可写地址范围:0

-31)

Address

地址

Register

寄存器

Brief Description

简述

0

FR_TX_SAMPLE_RATE_DIV

Transmit sample rate divisor (发送采样速率除法器)

1

FR_RX_SAMPLE_RATE_DIV

Receive sample rate divisor (接收采样速率除法器)

2

UNUSED

Unused Register (没有用到的寄存器)

3

UNUSED

Unused Register (没有用到的寄存器)

4

FR_MASTER_CTRL

Master Reset and Enable controls

(主复位及使能控制)

5

FR_OE_0

IO Buffer direction settings for pins that go to daugherboards

(指向子板的管脚的IO缓存流向设置)

6

FR_OE_1

IO Buffer direction settings for pins that go to daugherboards

(指向子板的管脚的IO缓存流向设置)

7

FR_OE_2

IO Buffer direction settings for pins that go to daugherboards

(指向子板的管脚的IO缓存流向设置)

8

FR_OE_3

IO Buffer direction settings for pins that go to daugherboards

(指向子板的管脚的IO缓存流向设置)

9

FR_IO_0

IO Registers for pins that go to daugherboards

(指向子板的管脚的IO寄存器)

10

FR_IO_1

IO Registers for pins that go to daugherboards

(指向子板的管脚的IO寄存器)

11

FR_IO_2

IO Registers for pins that go to daugherboards

(指向子板的管脚的IO寄存器)

12

FR_IO_3

IO Registers for pins that go to daugherboards

(指向子板的管脚的IO寄存器)

13

FR_MODE

Sets RX Mode [NORMAL,LOOPBACK,RX_COUNTING,RX_COUNTING_32BIT](RX

方式设置)

14

FR_DEBUG_EN

Enables debug settings for debugging FPGA designs(FPGA 使能诊断设置)

15

FR_DC_OFFSET_CL_EN

DC offset control loop

enable (DC 补偿控制环路使能)

16

FR_ADC_OFFSET_0

ADC/DAC DC correction offset value (2's compliment) (ADC/DAC

纠错补偿值)

17

FR_ADC_OFFSET_1

ADC/DAC DC correction offset value (2's compliment) (ADC/DAC

纠错补偿值)

18

FR_ADC_OFFSET_2

ADC/DAC DC correction offset value (2's compliment) (ADC/DAC

纠错补偿值)

19

FR_ADC_OFFSET_3

ADC/DAC DC correction offset value (2's compliment) (ADC/DAC

纠错补偿值)

20

FR_ATR_MASK_0

Automatic Transmit/Receive Enable (Slot 0)

(自动发射/接收使能)

21

FR_ATR_TXVAL_0

Automatic Transmit/Receive TX Pin Values (Slot 0) (自动发射/接收

TX 管脚值)

22

FR_ATR_RXVAL_0

Automatic Transmit/Receive RX Pin Values (Slot 0) (自动发射/接收

RX 管脚值)

23

FR_ATR_MASK_1

Automatic Transmit/Receive Enable (Slot 1)

(自动发射/接收使能)

24

FR_ATR_TXVAL_1

Automatic Transmit/Receive TX Pin Values (Slot 1) (自动发射/接收

TX 管脚值)

25

FR_ATR_RXVAL_1

Automatic Transmit/Receive RX Pin Values (Slot 1) (自动发射/接收

RX 管脚值)

26

FR_ATR_MASK_2

Automatic Transmit/Receive Enable (Slot 2)

(自动发射/接收使能)

27

FR_ATR_TXVAL_2

Automatic Transmit/Receive TX Pin Values (Slot 2) (自动发射/接收

TX 管脚值)

28

FR_ATR_RXVAL_2

Automatic Transmit/Receive RX Pin Values (Slot 2) (自动发射/接收

RX 管脚值)

29

FR_ATR_MASK_3

Automatic Transmit/Receive Enable (Slot 3)

(自动发射/接收使能)

30

FR_ATR_TXVAL_3

Automatic Transmit/Receive TX Pin Values (Slot 3) (自动发射/接收

TX 管脚值)

31

FR_ATR_RXVAL_3

Automatic Transmit/Receive RX Pin Values (Slot 3) (自动发射/接收

RX 管脚值)

Writable Address Range: 32 - 63 (可写地址范围:32

-63)

Address

地址

Register

寄存器

Brief Description

简述

32

FR_INTERP_RATE

Transmit interpolation rate [1,1024]

(发射查补速率[1,1024])

33

FR_DECIM_RATE

Receive decimation rate [1,256]

(接收抽取速率 [1,256])

34

FR_RX_FREQ_0

DDC Center Frequency (word 0) (DDC

中心频率)

35

FR_RX_FREQ_1

DDC Center Frequency (word 1) (DDC

中心频率)

36

FR_RX_FREQ_2

DDC Center Frequency (word 2) (DDC

中心频率)

37

FR_RX_FREQ_3

DDC Center Frequency (word 3) (DDC

中心频率)

38

FR_RX_MUX

Configure the RX muxing stream of I/Q data

(配置RX链路复接I/Q数据流)

39

FR_TX_MUX

Configure the TX muxing stream of I/Q data

(配置TX链路复接I/Q数据流)

40

FR_TX_A_REFCLK

Configures a reference clock sent to daughterboard A (TX)

(配置发往子板的参考时钟)

41

FR_RX_A_REFCLK

Configures a reference clock sent to daughterboard A (RX)

(配置发往子板的参考时钟)

42

FR_TX_B_REFCLK

Configures a reference clock sent to daughterboard B (TX)

(配置发往子板的参考时钟)

43

FR_RX_B_REFCLK

Configures a reference clock sent to daughterboard B (RX)

(配置发往子板的参考时钟)

44

FR_RX_PHASE_0

RX DDC Starting Phase (word 0) (RX DDC

启动阶段)

45

FR_RX_PHASE_1

RX DDC Starting Phase (word 1) (RX DDC 启动阶段)

46

FR_RX_PHASE_2

RX DDC Starting Phase (word 2) (RX DDC 启动阶段)

47

FR_RX_PHASE_3

RX DDC Starting Phase (word 3) (RX DDC 启动阶段)

48

FR_TX_FORMAT

Configures TX Format (配置TX格式)

49

FR_RX_FORMAT

Configures RX Format (配置TX格式)

50

AVAILABLE

Available for future use (将来备用)

51

AVAILABLE

Available for future use (将来备用)

52

AVAILABLE

Available for future use (将来备用)

53

AVAILABLE

Available for future use (将来备用)

54

AVAILABLE

Available for future use (将来备用)

55

AVAILABLE

Available for future use (将来备用)

56

AVAILABLE

Available for future use (将来备用)

57

AVAILABLE

Available for future use (将来备用)

58

AVAILABLE

Available for future use (将来备用)

59

AVAILABLE

Available for future use (将来备用)

60

AVAILABLE

Available for future use (将来备用)

61

AVAILABLE

Available for future use (将来备用)

62

AVAILABLE

Available for future use (将来备用)

63

AVAILABLE

Available for future use

(将来备用)

Readable Address Range: 1 - 3 (可读地址范围:1 -

3)

仅仅只有三个可读寄存器,它们不和可写寄存器在一起,代码 fpga_regs_standard.h 在末尾部分定义它们。(所寻 READBACK 寄存器。)

Address

Register

Brief Description

1

FR_RB_IO_RX_A_IO_TX_A

Readback A-Side I/O pins (可读取A端I/O管脚)

2

FR_RB_IO_RX_B_IO_TX_B

Readback B-Side I/O pins (可读取B端I/O管脚)

3

FR_RB_CAPS

Readback FPGA capabilities

(FPGA可读取使能)

Custom Registers

(自定义寄存器)

Writable Address Range: 64 - 79 (可写地址范围:64

-79)

这些寄存器地址确保没被定义为公用(common)和

标准(standard)寄存器,专用于用户自定义的寄存器。

子板

如何去写USB接口用来控制诸如频率调制,滤波。

时序图或者子板的特定锁相时间,合成锁相时间等是很有意思的工作,下面是到子板清单的链接。

子板清单

Message Block

链接 FPGA 的 MessageBlocks 探讨高效地发送和接收功用。

注:UsrpFPGA(原文出处,翻译整理仅供参考!)

2280

2280

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?