常规的验证UVM、形式验证就可以覆盖大部分应用,但是这些主要是集中在SV/SC/C++/verilog语言中进行。在验证中python的应用大部分是script,但python强大的库只用来作为script有点太“掉价”了。在国外有一位大牛干脆将UVM集成到了python中,直接将python作为了验证语言彻底打破了python和sv交互的障碍。试想一下如果算法、设计、验证都是基于python那开发周期明显缩短,特别是对于AI。

对于cocotb的介绍小编是查看了相关的官网进行了阅读对有verilog/uvm经验的人来说可以很快入门。

参考网站:

https://github.com/pyuvm/pyuvm https://docs.cocotb.org/en/stable/release_notes.html

cocotb几个核心问题:

-

工作原理:

-

协同仿真(Co-simulation):Cocotb的核心在于协同仿真。这意味着它可以与多种仿真器(如VCS、Verilator等)集成,以执行设计代码(如Verilog、VHDL、SystemVerilog)的仿真。Cocotb本身并不执行仿真,而是作为这些仿真器的一个插件或接口,允许Python测试代码与仿真器中的设计代码进行交互。

-

协程(Coroutine):Cocotb的名字中的“co”代表协程(Coroutine)。协程是一种用户态的轻量级线程,它允许程序在多个任务之间切换,而不会引起线程切换的开销。在Cocotb中,协程被用于编写测试代码,以便在仿真过程中控制和管理测试的执行。

-

测试框架和测试用例:Cocotb提供了一套基于Python的测试框架,用于构建和管理测试用例。测试框架允许工程师使用Python编写测试代码,以验证设计代码的正确性。测试代码可以包括各种测试场景、输入数据和期望的输出结果。

-

通信接口:Cocotb通过仿真器提供的各种标准接口与仿真器中的设计代码进行通信。这些接口允许Python测试代码发送激励(如输入信号)到设计代码,并接收设计代码的响应(如输出信号)。通过这种方式,Cocotb可以验证设计代码在不同条件下的行为是否符合预期。

-

设计重用和随机化测试:Cocotb鼓励设计重用和随机化测试的哲学。通过编写可重用的测试代码和使用随机化测试技术,工程师可以更高效地发现设计中的问题,并提高测试的覆盖率和可靠性。

-

集成uvm后组件与uvm之间差别

案例中选取了example下面的TinyALU_reg进行分析

UVM_component 部分:

1. TEST

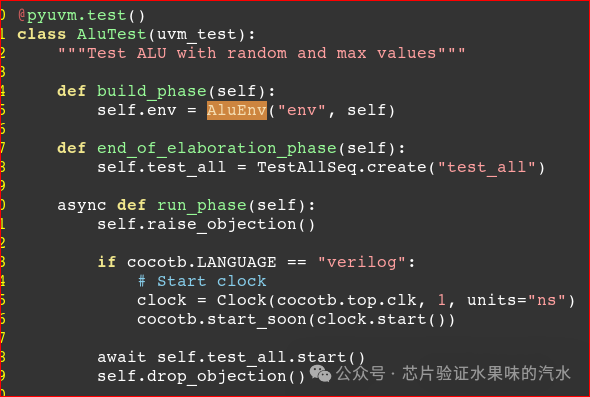

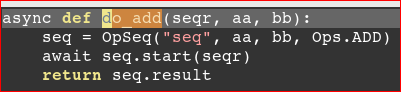

@pyuvm.test是python的修饰符,AluTest是扩展于UVM_TEST的class。在build_phase中instance了env,在end_of_elaboration_phase中create了TestAllSeq,并在run_phase中进行了start()。在pyuvm中uvm_component中没有了12个小phase,并使用objection机制控制各phase的进程。在uvm中我们启动sequence一般是defalue_sequence和start(),但是在pyuvm中是使用start()。

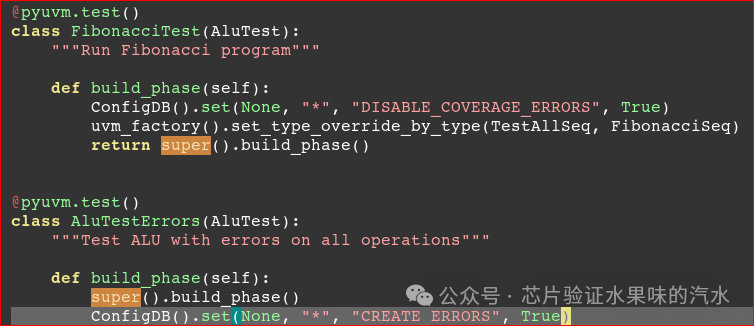

FibnacciTest扩展与AluTest class,在build_phase中可以直接进行factory机制进行override,这一点和UVM意思是一样的,简单来说就是修改了注册。

2. env

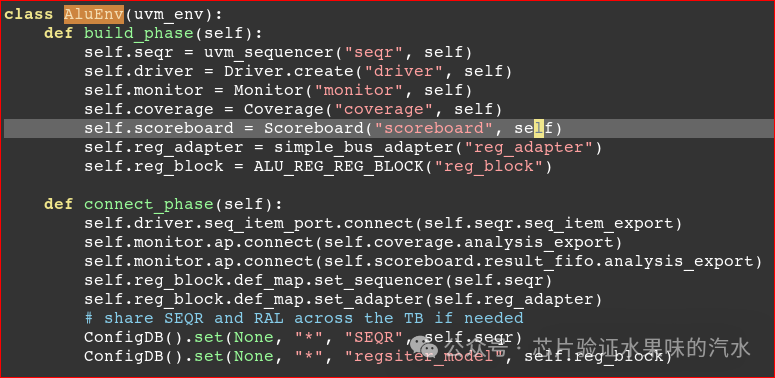

在build_phase和connect_phase进行了create和port/export connect。其中我们这边有regmodel进行了显示预测,平台中集成了adapter/predict,架构上和uvm没有啥区别。 其中,我们可以看到seqr config set 这个是为了方便sequence拿到p_sequencer句柄。

3. scb

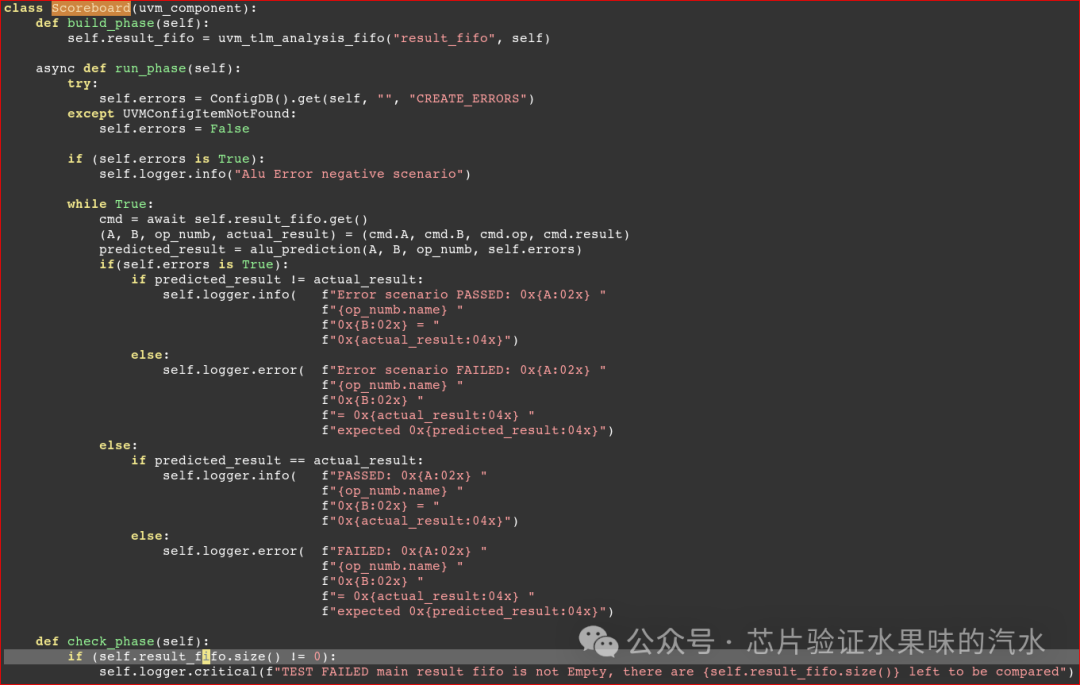

scb中主要是两个export拿到数据放到Q中,然后进行check。

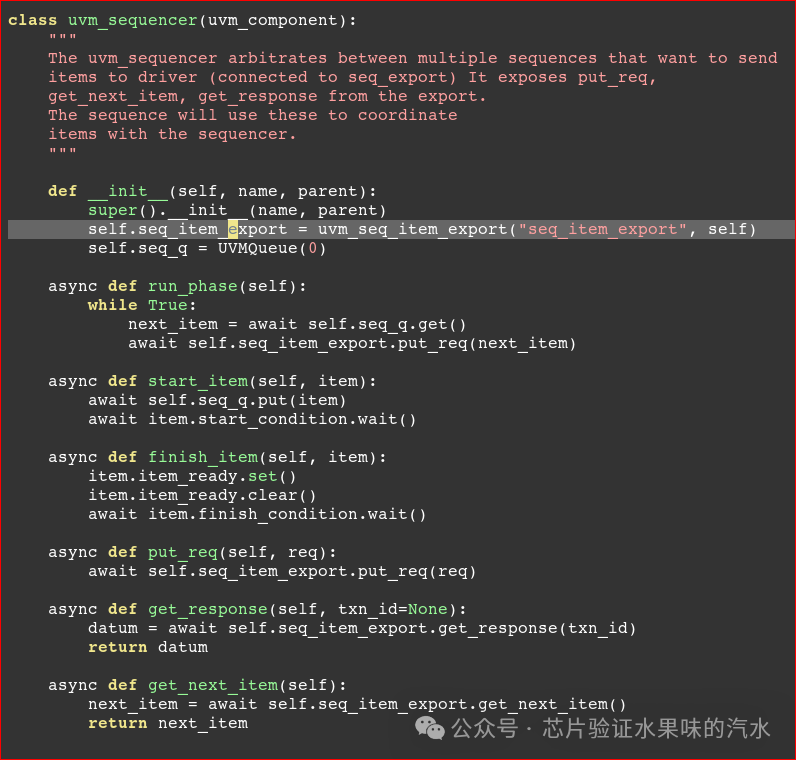

4. sequencer

这个就是和uvm里面是一样的,用例相对简单用户可以开发virtual sequencer。

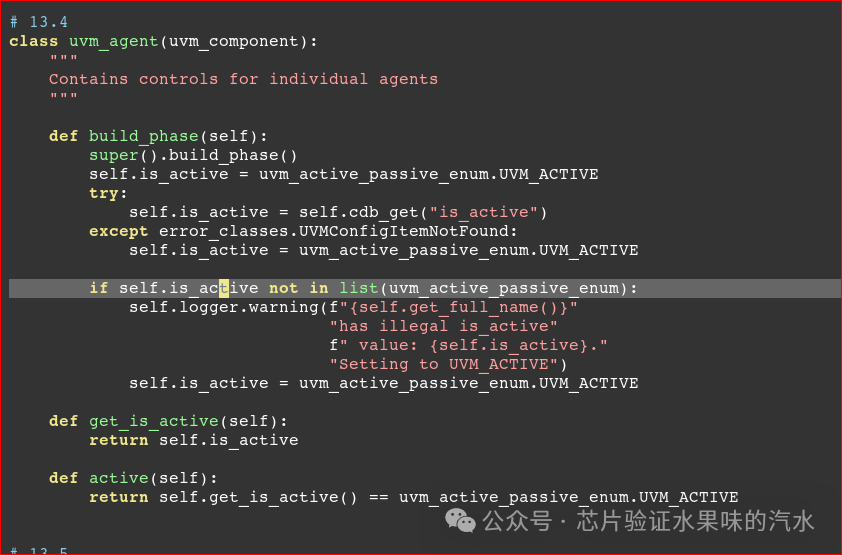

5. agent

一般来说agent 可以放drv/mon/sequncer,is_active确定当前的agent配置成master or slave。

3. drvier

TinyAluBfm是一个interface类型,transcation 包我们也是采用seq_item_port.get_next_item()和seq_item_port.item_done()组合。

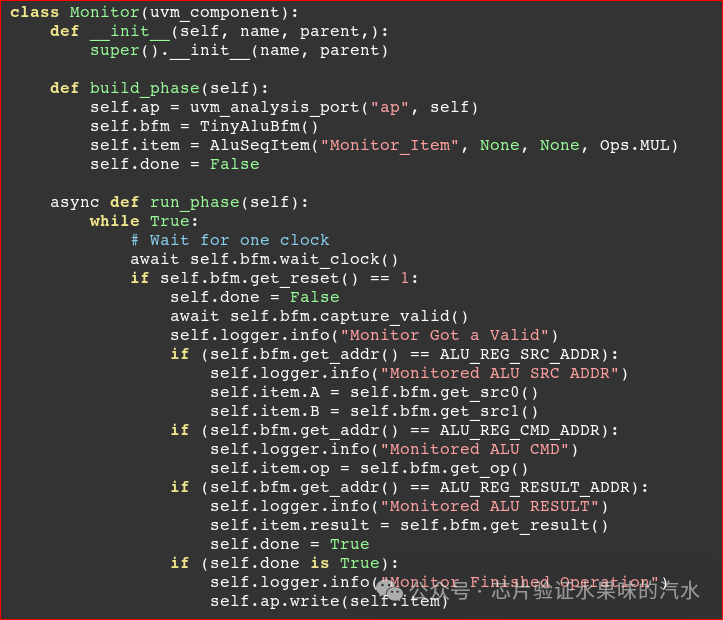

3. monitor

数据采集是采用capture_valid信号控制,采集完成以后发送到ap口上。

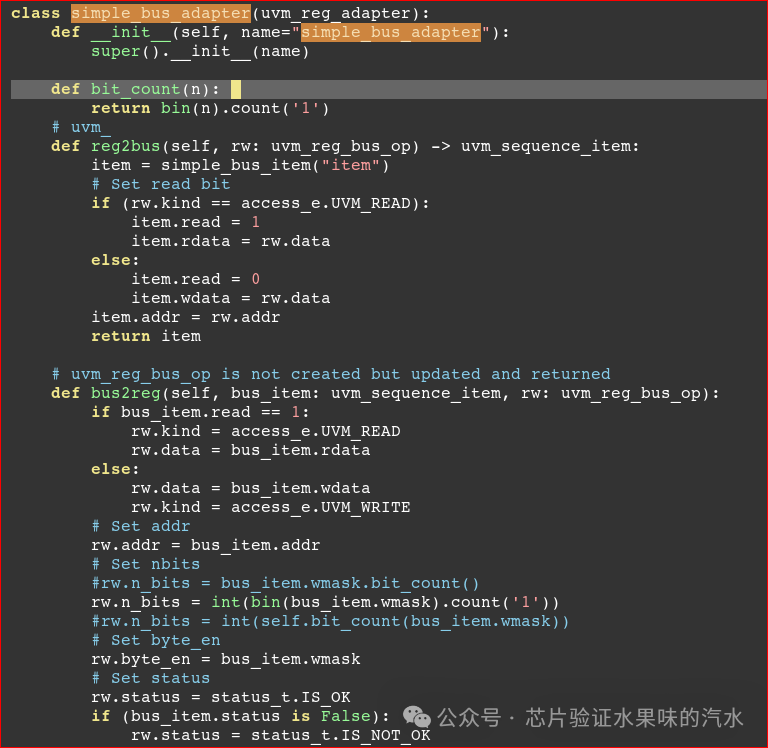

4. adapter

bus2reg、reg2bus都是标配

5. predictor

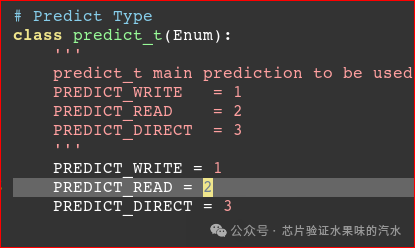

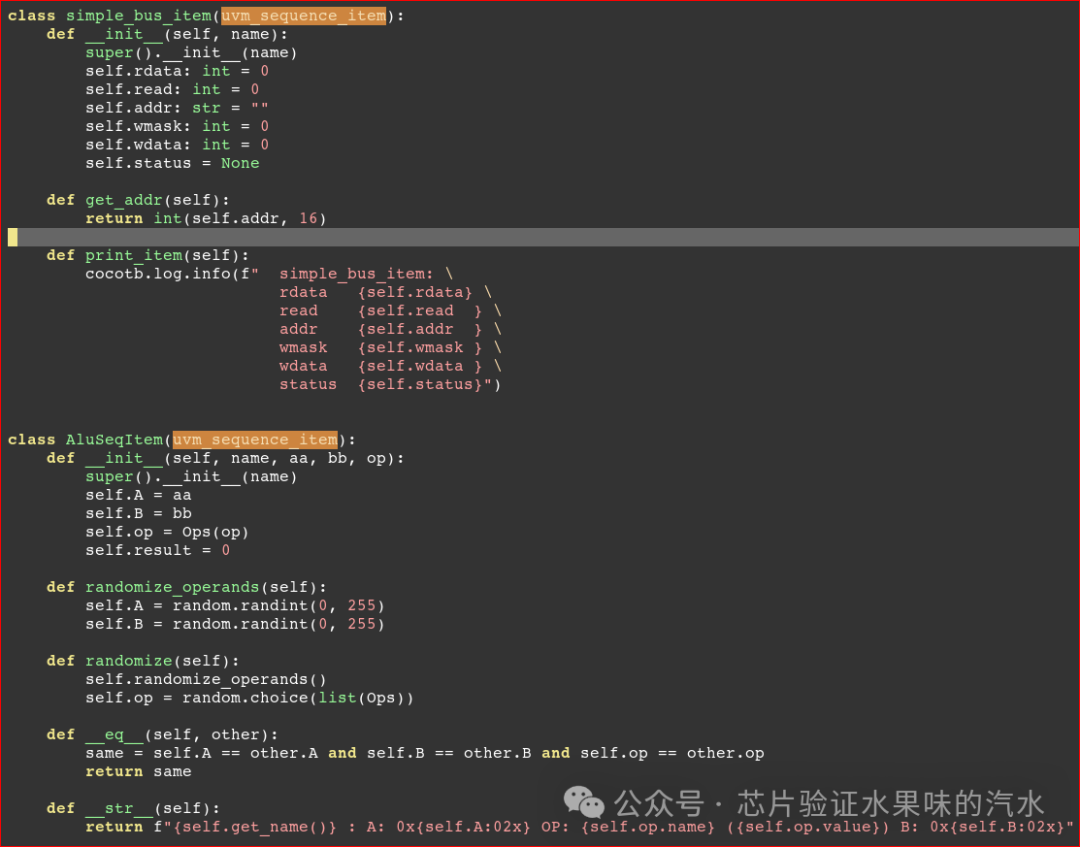

UVM_object 部分:

1. items

这边还没有call back机制调用pre_randomize()和post_randomize(),不过这个我们后期可以加上去可以进行call back. items的数据类型是支持compare、recoder、pack、unpack、copy等数据类型

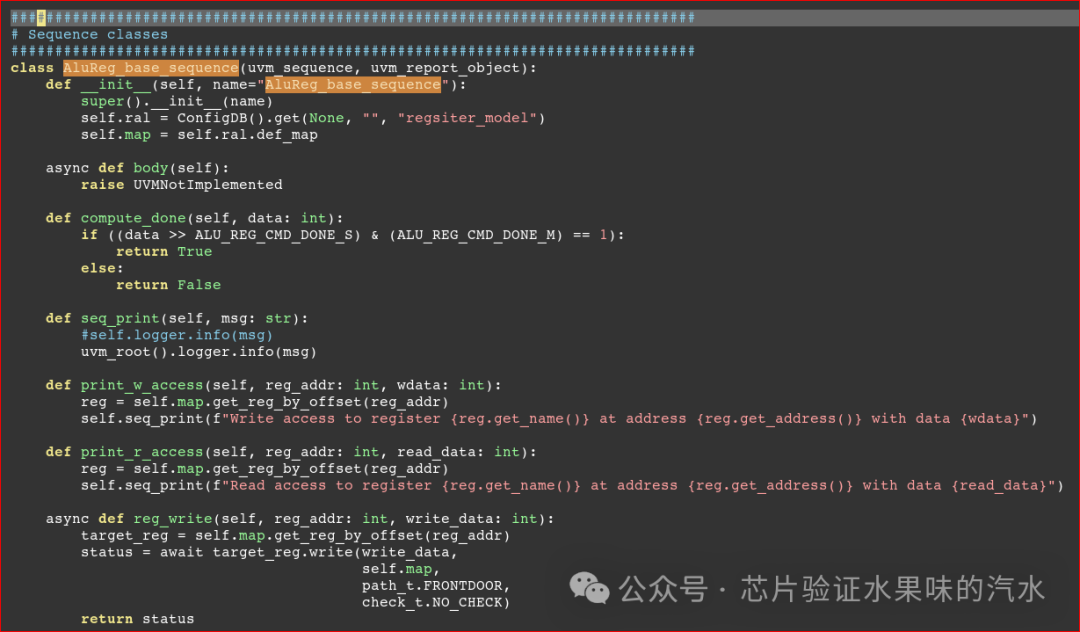

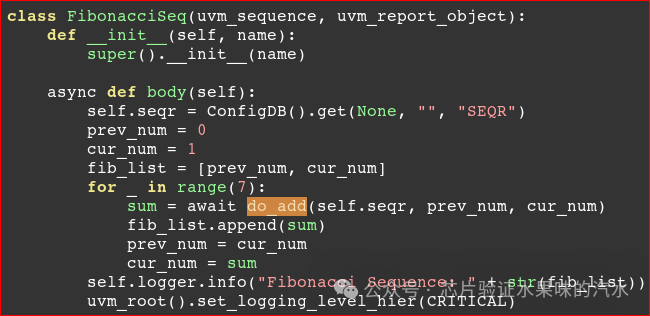

2.sequence

在sequence中我们获得sequncer的句柄是使用config get的方式,这个和uvm中是用p_sequencer用法还是有区别的。获得寄存器的方式也是使用config的方式。

案例中我们可以看到架构是相对简单的,我们可以优化的地方很多,后期我们会使用新的uvm架构来搭建pyuvm作为一个实践项目。

2299

2299

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?