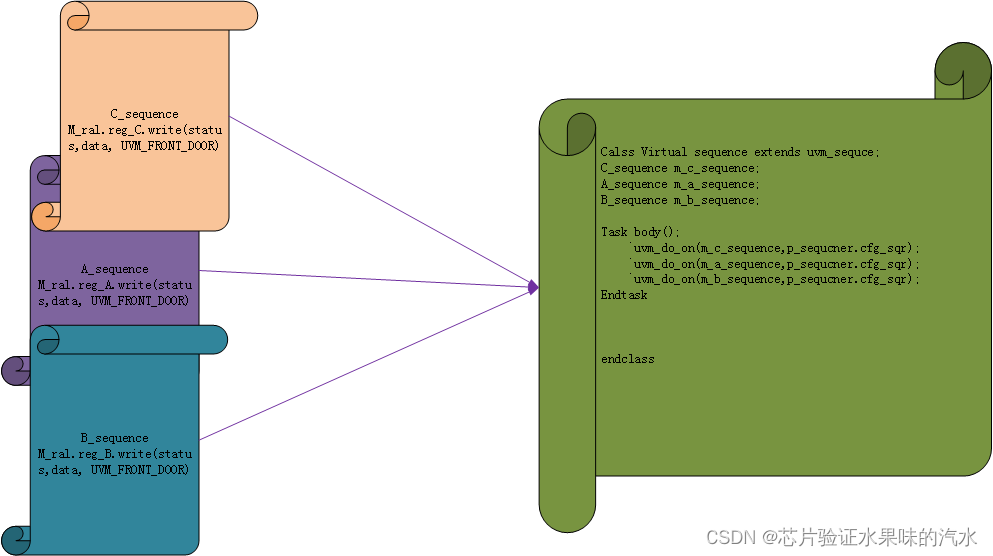

在uvm中有virtual sequence的概念是一个seuqence的群落集合地,用来将配置的seuqence和数据的sequence分别开来通过p_sequencer进行路由发送。在常规使用过程中我们可能会有多个配置的seuqnce一般是进行rtl寄存器配置操作,不可避免的会使用到ral的方式进行操作。

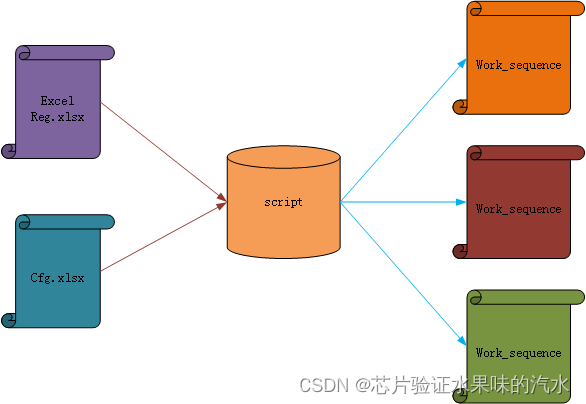

但是这些work_sequnce都是需要手动敲写去实现驱动,有没有一种方法可以进行自动生成呢?可以避免实现手动编写的出现语法错误,可读性又比较差。

上图中reg.xlsx是我们常用的寄存器文件里面包含了寄存器的编译地址,寄存器名字,读写属性,默认value等信息。

| RegName | offset(H) | attrbute | Bits | Fieldname | DefaultValue | Description | Cmodel_key |

| A_STRENGTH_CURVE | 0x0 | RW | [31:0] | A_STRENGTH_CURVE | 0X10C | CXXX | |

| B_CTRL | 0x4 | RW | [31:0] | B_CTRL | 0XA0 | CXXX | |

| B_DE_PARAM | 0x8 | RW | [31:0] | B_DE_PARAM | 0X90 | CXXX | |

| C_ROI_STATR | 0xC | RW | [26:16] | c_roi_sy | 0X0 | CXXX | |

| RW | [10:0] | c_roi_sx | 0X50 | CXXX | |||

| C_ROI_END | 0X200 | RW | [26:16] | c_roi_ey | 0X10 | CXXX | |

| RW | [10:0] | c_roi_sx | 0XB0 | CXXX |

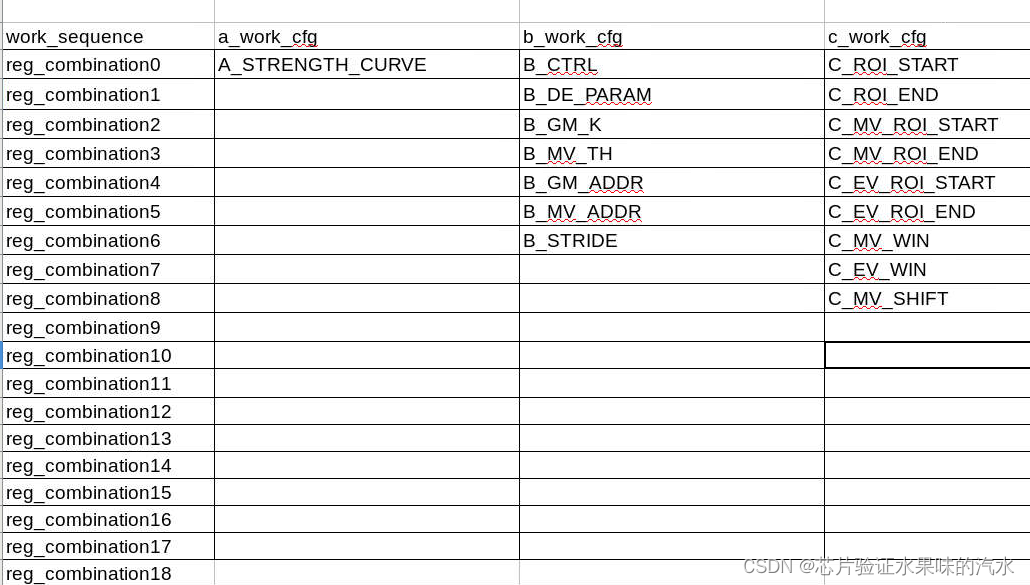

Cfg.xlsx是我们进行需要配置的寄存器集合: 其中,a_work_sequence是work_sequence 的name, A_STRENGTH_CURVE是寄存器的名字,例如:

其中,a_work_sequence是work_sequence 的name, A_STRENGTH_CURVE是寄存器的名字,例如:

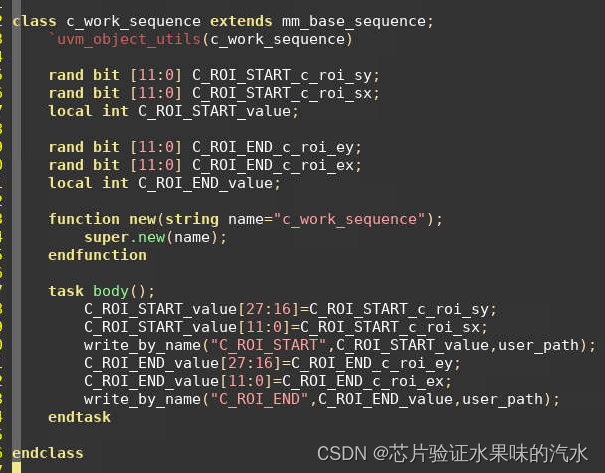

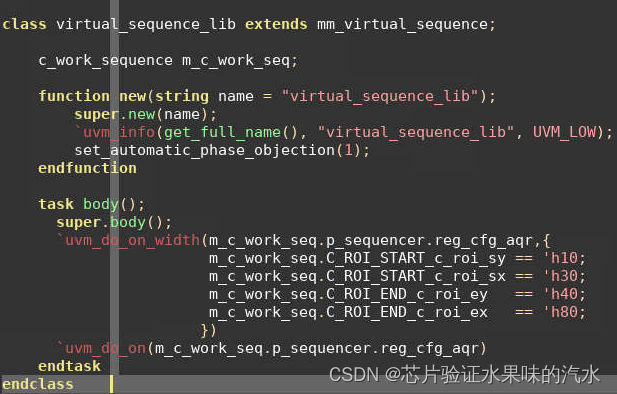

在class中 field_name的value命名规则是reg_name + filed_name的方式,目的是为了防止同一组的寄存器集合中出现寄存器field名字存在相同的情况,在顶层的virtual_seuqnce中可以进行调用和赋值。

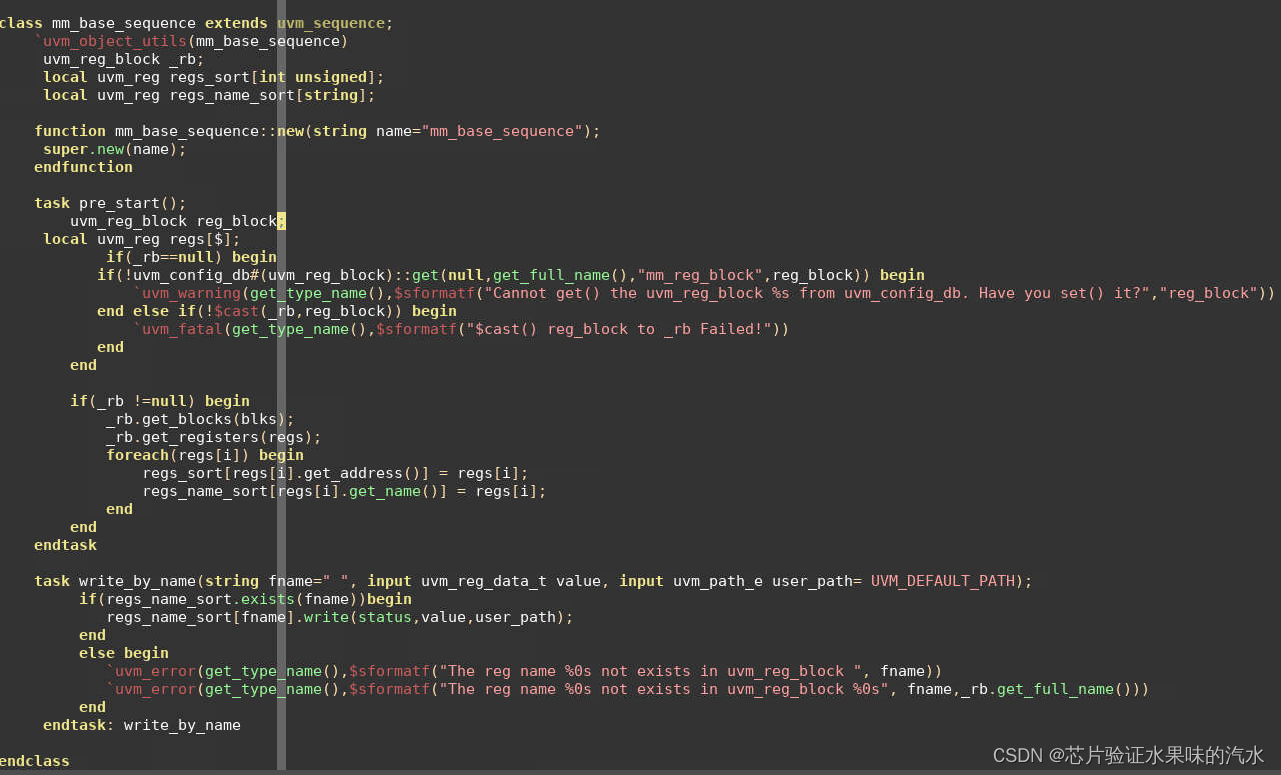

write_by_name的task是如何得到的呢?在mm_base sequence中通过uvm_reg_block获取uvm_reg和uvm_filed的相关信息并封装在数组中。

通过上述的flow流程我们可以实现自动化生成配置信息的sequence,简单高效的可以完成配置信息的sequence的编写。

6520

6520

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?