zynqNet

祥瑞Coding

机器学习,计算机视觉

展开

-

ZynqNet解析(六)内存的实现

背景:在zynqNet项目之中,程序到底如何分配DRAM上的地址作为global Memory。以及如何分配相应程序的内存。目录相关内容CPU端的函数与作用FPGA端函数的作用一、CPU端对DRAM的定义1.1 关于DRAM指针的全局变量1.2 定义DRAM指针的函数1.3 定义DRAM底层驱动1.4 具体驱动实现1.4.1 SHARED_DRAM_open...原创 2018-10-28 20:30:28 · 1985 阅读 · 0 评论 -

ZynqNet解析(七)实现于BRAM上的Cache

背景:我们需要仿照ZynqNet的模式构造卷积的IPcore用于FPGA的优化。目的:搞懂zynqNet的cache的实现。相关内容:ZynqNet解析(六)内存的实现 https://blog.csdn.net/weixin_36474809/article/details/83409853MTCNN(十)构建卷积IPcore https://blog.csdn.net/weix...原创 2018-11-08 14:59:27 · 2632 阅读 · 0 评论 -

ZynqNet解析(八)对IPcore的HLS

背景:zynqNet运用HLS来实现相应的IPcore。相关HLS过程的信息会打印到console之中。目的:读懂HLS对IPcore代码的HLS过程,具体硬件如何实现。将报告信息存下来用于参考。目录一、 全IPcore的HLS console二、 processInputChannel函数的HLSconsole三、synthesis结果IPcore调试成功,HLS打印信息...原创 2018-12-12 14:23:15 · 2180 阅读 · 0 评论 -

ZynqNet解析(四)FPGA端程序解析

背景:ZynqNet能在xilinx的FPGA上实现deep compression的网络,FPGA端程序运用传入每层数据运算后存在DRAM上。目的:读懂ZynqNet的FPGA端的代码。源码地址:https://github.com/dgschwend/zynqnet目录程序包括:1. 读取每层信息1.1 给所有block设置layer信息1.2 加载权重预加载图像...原创 2018-09-13 14:24:48 · 2021 阅读 · 0 评论 -

ZynqNet解析(三)CPU端程序解析

背景:ZynqNet能在xilinx的FPGA上实现deep compression的网络,目的:读懂ZynqNetCPU端的代码。源码地址:https://github.com/dgschwend/zynqnet目录cpu_top程序包括1 CPU端创建网络1.1 储存网络结构的结构体1.2 创建网络的函数1.3 输出每层信息1.4 构造函数2 FP...原创 2018-09-13 08:55:44 · 1453 阅读 · 3 评论 -

ZynqNet解析(二)运行与调试

背景:ZynqNet能在xilinx的FPGA上实现deep compression目的:运行zynqNet的代码。源码地址:https://github.com/dgschwend/zynqnet目录1. _TRAINED_MODEL2. _FIRMWARE2.1 运行打印结果3._HLS_CODE3.1 C simulation3.2 Synthesis...原创 2018-09-12 15:04:44 · 2066 阅读 · 1 评论 -

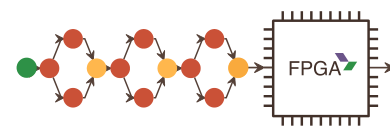

ZynqNet解析(一)概览

背景:ZynqNet能在xilinx的FPGA上实现deep compression。目的:读懂zynqNet的代码和论文。目录一、网络所需的运算与存储1.1 运算操作:1.2 Memory requirements:1.3 需求分析:1.4 FPGA based accelerator需要执行:二、网络结构针对网络结构进行了三种优化: FPGA-real...原创 2018-09-11 19:17:40 · 4842 阅读 · 0 评论 -

ZynqNet解析(五)具体硬件实现

背景:ZynqNet能在xilinx的FPGA上实现deep compression。目的:读懂zynqNet的代码中关于硬件实现的部分。目录1. 几个命名空间1.1 选用namespace的原因(4.4.2)1.1.1 软件整体进行HLS1.1.2 object-orinted1.1.3 Block-structured(ZynqNet采用的)1.2 四种cac...原创 2018-09-19 13:17:29 · 1462 阅读 · 0 评论

分享

分享