Primitive基元解析

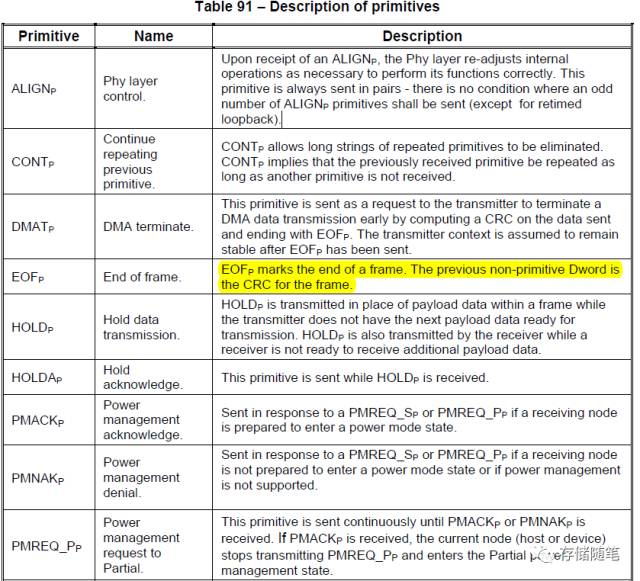

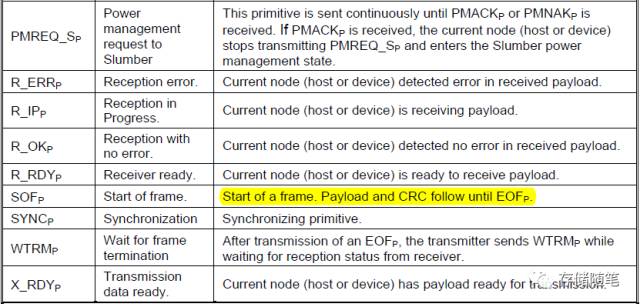

Primitive基元是用于控制和提供串行线状态的Dword实体。比如ALIGNp, SOFp, EOFp, HOLDp, PMREQ_Pp, PMREQ_Sp, SYNCp, WTRMp, R_RDYp, X_RDYp等。其对应的含义以及DW解析如下表:

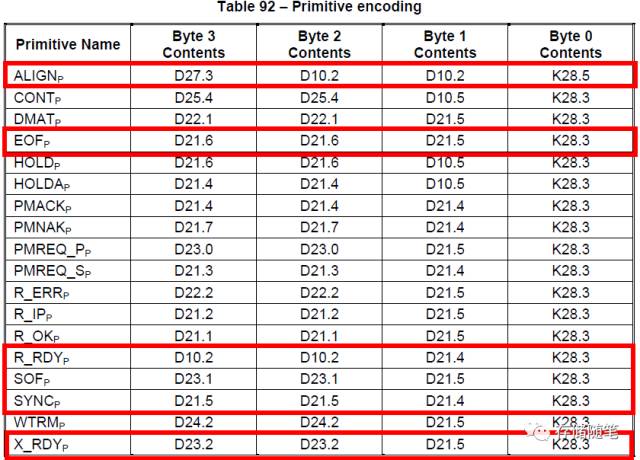

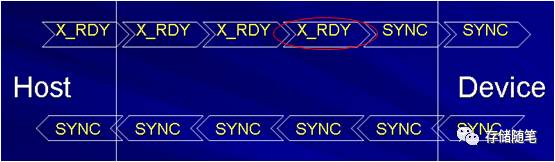

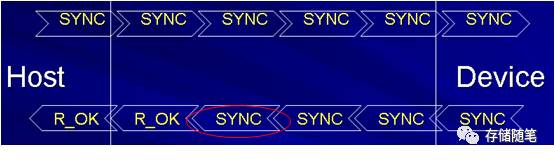

理论再多不如实践呐,现以设备接收一个资料包的传输过程来说明基元的作用。首先主机、设备都处于空闲状态(SYNC)。

(1) 主机有资料需要发送,发送X_RDY,通知设备准备接收资料;

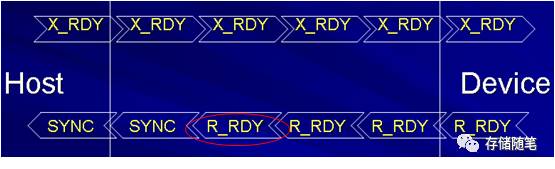

(2)设备检查自己的状态,准备好后发送R_RDY告诉主机可以发送数据;

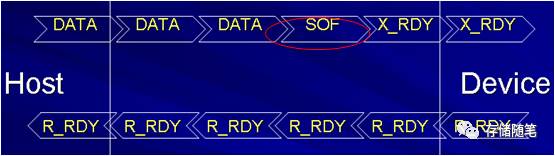

(3)主机开始发送资料, SOF为资料开始标志;

(4)接收方在接收到资料时,以R_IP告诉主机正在接收资料;

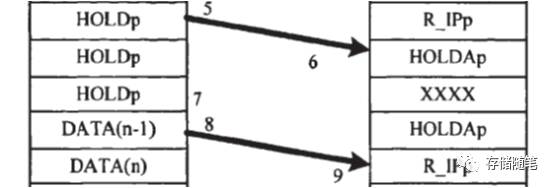

(5)主机的资料包没有发送完,可是还有些资料没有准备好,以HOLD告诉设备暂停资料发送;

(6) 设备接收到HOLD后,以HOLDA回应;

(7) 主机准备好了资料可以继续发送,以HOLD结束等待状态;

(8)主机继续传输资料;

(9)设备接收资料,以R_IP告诉主机正在接收资料;

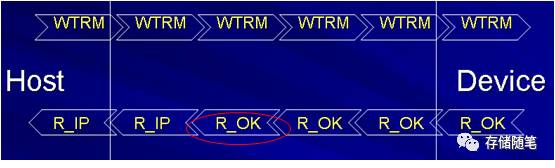

(10) 主机发送完了整个资料包,发送WTRM告诉设备:主机正在等待传输结果;

(11) 设备接收完整个资料包并检验正确,以R_OK告诉主机接收正确;

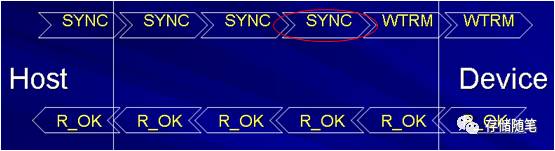

(12)主机进入空闲状态,发送同步信号SYNC;

(13)设备进入空闲状态,发送同步信号SYNC;

1881

1881

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?