从altera转战xilinx,经典的FPGA到ZYNQ系列,第一站就是先熟悉编译软件Vivado。我就直接跳过软件安装部分了,如有疑问,可以在评论区提出来,我看到了就帮你解答。

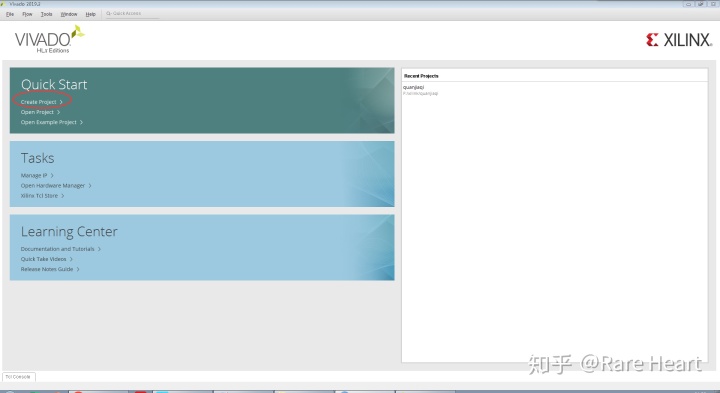

首先是是打开界面

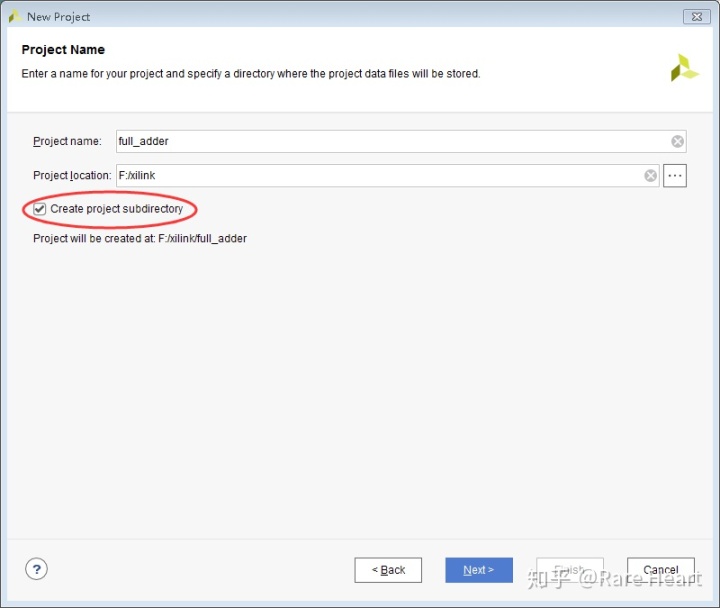

然后建立工程,红圈表示自动建立子文件夹。

因为手上暂时没有现成的器件,后续一直点next就行了。

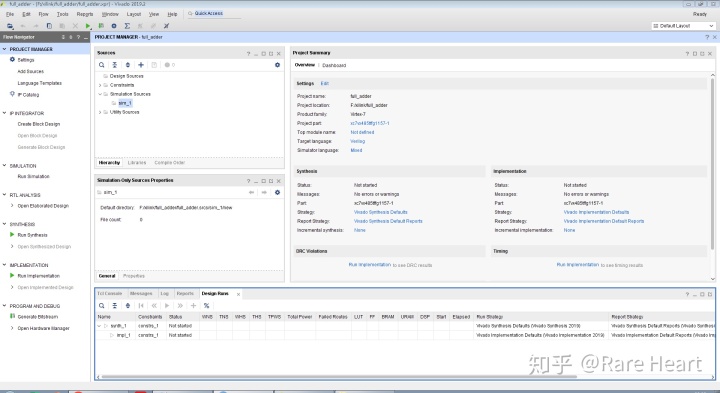

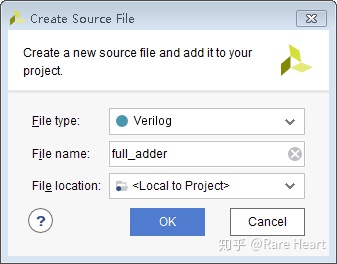

这是打开的界面,然后我们需要开始创建.v文件写全加器的电路代码。右键点击Design Sources->next->creat file.会得到下图二,然后取名full_adder再点OK和finish。

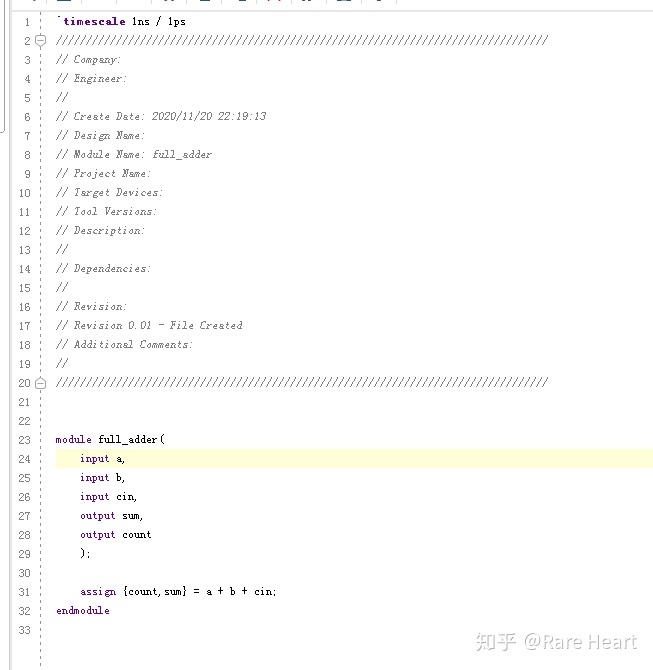

写好的代码如下图所示:

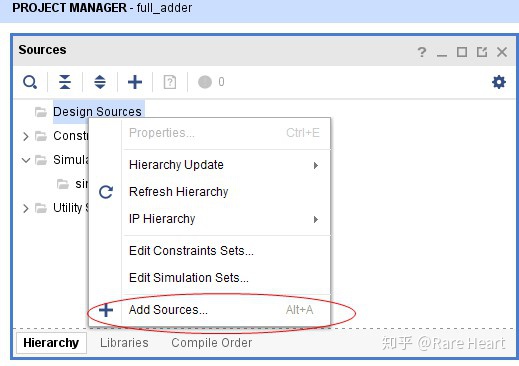

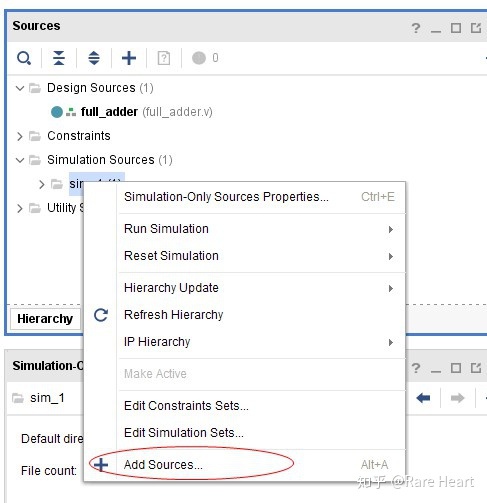

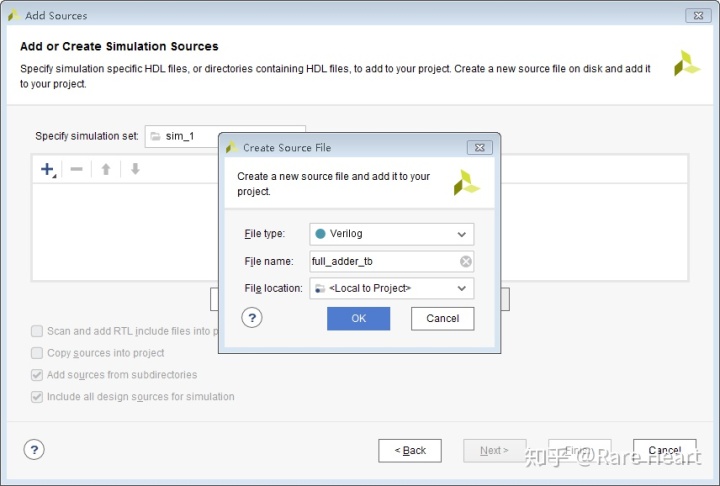

然后开始准备RTL仿真,右键点击Sim(1)的添加源文件。后面过程与写工程代码一样的流程。

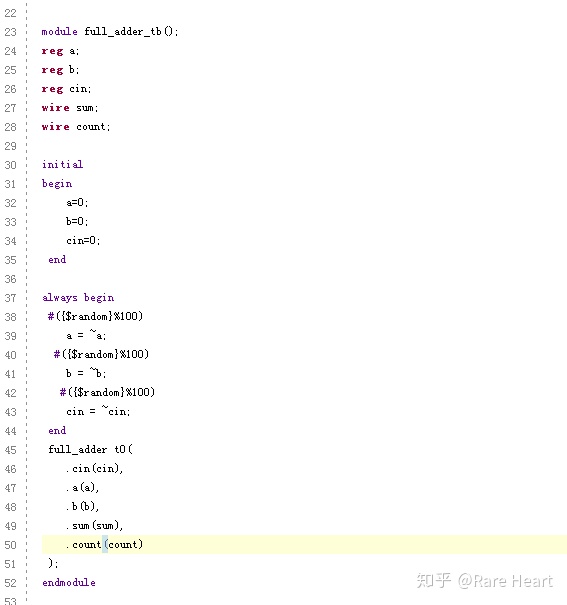

然后开始写激励文件。代码如下图:

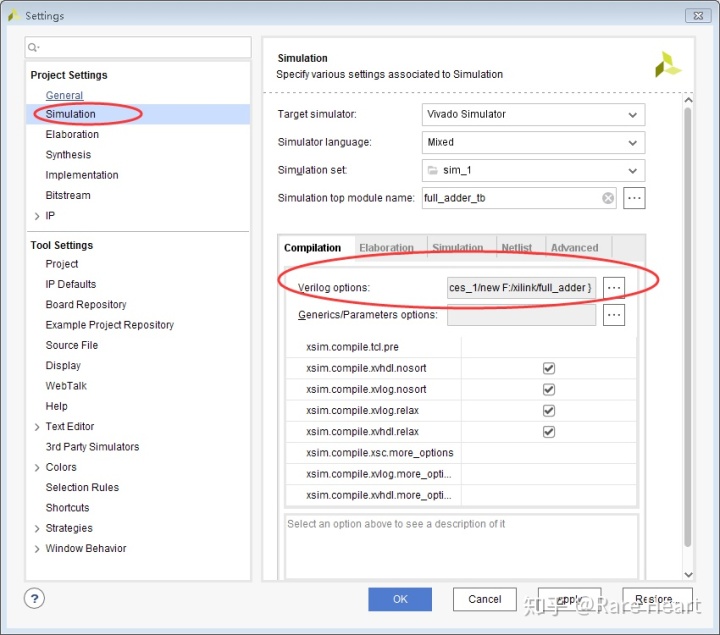

最后点击Tool-》Setting,设置仿真格式及其他。

一定要选择红圈处的verilog路径,一般就是你的工程文件夹。点击OK就直接运行仿真了,因为代码比较简单我就没做语法检验。

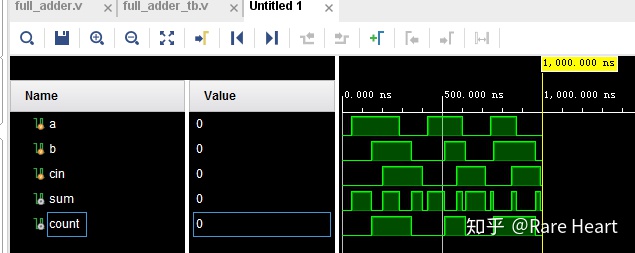

感觉这个仿真还挺不错的,比modelsim方便很多,主要是modelsim作为第三方软件需要额外下载,没有自带的便捷。

总结一下,感觉就是在vivado上写代码特别难受,还有他的编译功能找语法错误功能有点没摸懂,不太习惯。后面还是暂时先用notepad++写代码吧,看起来爽多了。

本文介绍了作者从Altera转向Xilinx后,初次使用Vivado进行FPGA设计的经验。通过创建全加器项目,详细说明了建立工程、编写Verilog代码、设置RTL仿真及运行仿真的步骤。相较于第三方软件Modelsim,作者认为Vivado内置的仿真功能更便捷,但在代码编辑方面不太习惯,倾向于使用notepad++。

本文介绍了作者从Altera转向Xilinx后,初次使用Vivado进行FPGA设计的经验。通过创建全加器项目,详细说明了建立工程、编写Verilog代码、设置RTL仿真及运行仿真的步骤。相较于第三方软件Modelsim,作者认为Vivado内置的仿真功能更便捷,但在代码编辑方面不太习惯,倾向于使用notepad++。

7609

7609

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?