我看csdn上关于vivado仿真的小实验很少,正好老师让我给师弟们讲讲这个软件,我就自己写一个吧。

用vivado实现一个四位全加器,并用自带的仿真软件仿真

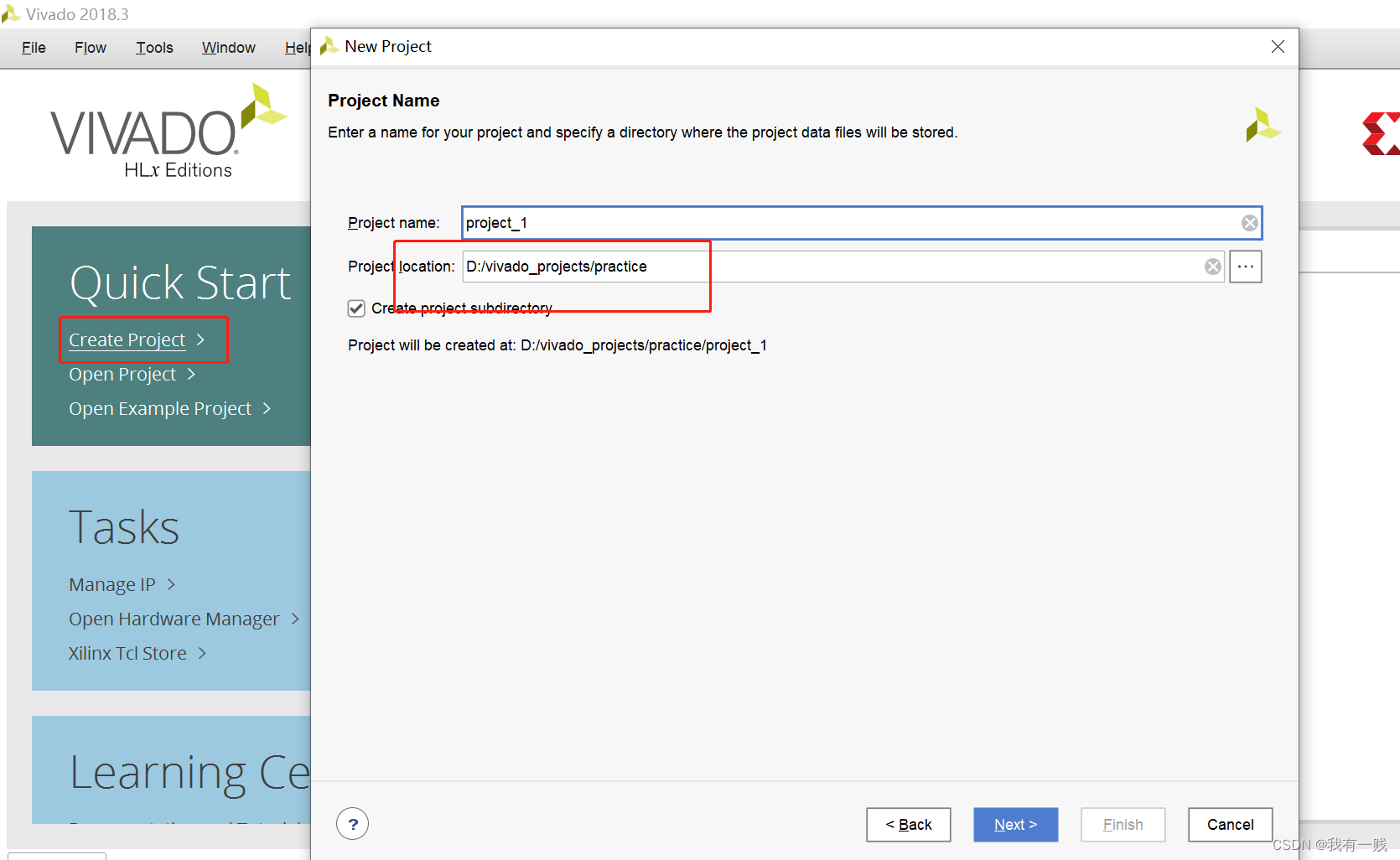

1.创建工程,这一步提前在D盘上创建个文件用来放project

然后一直点NEXT,直到下图

然后一直点NEXT,直到下图

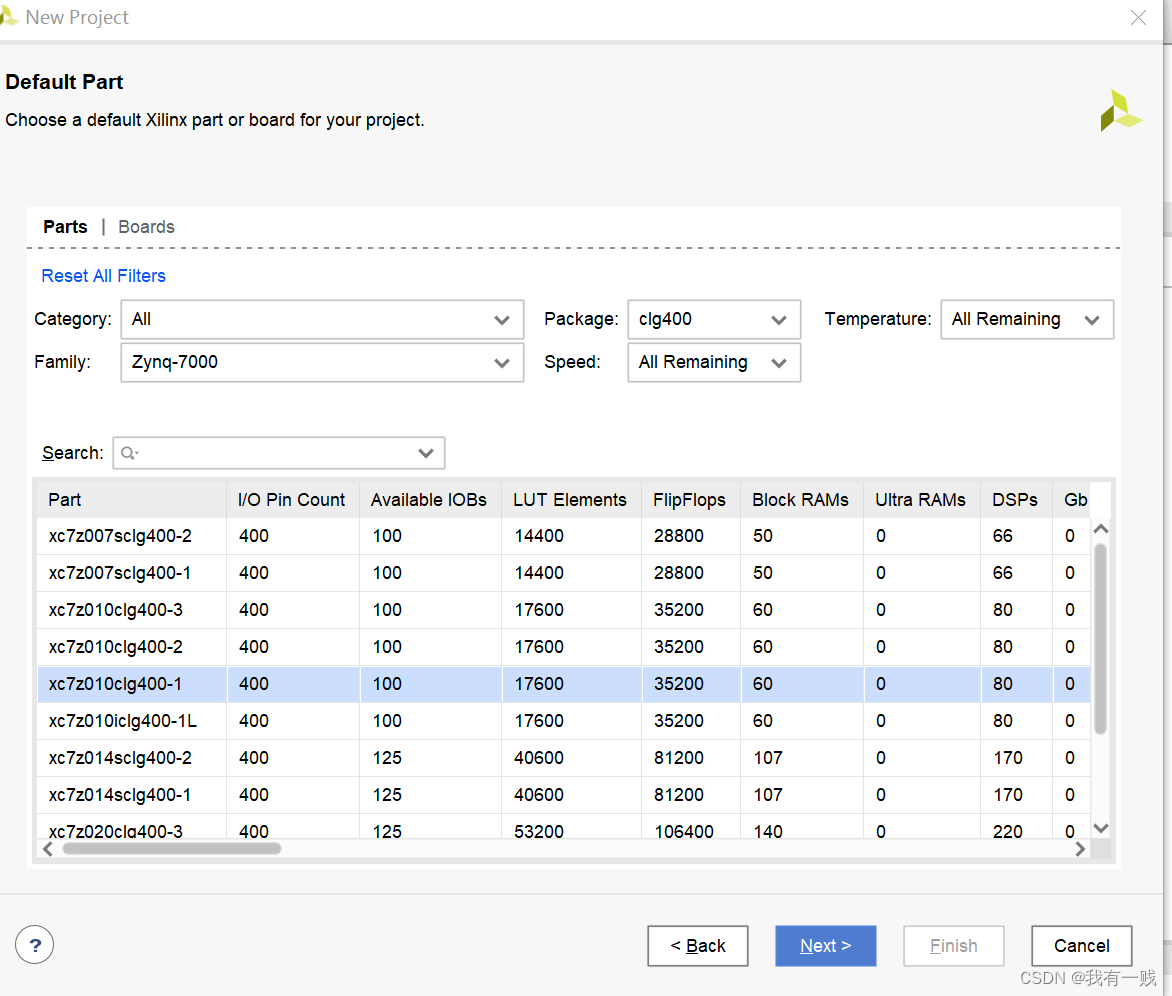

这步是选按照型号选板子,咱只做仿真实验的话,就随便选一个就行。

这步是选按照型号选板子,咱只做仿真实验的话,就随便选一个就行。

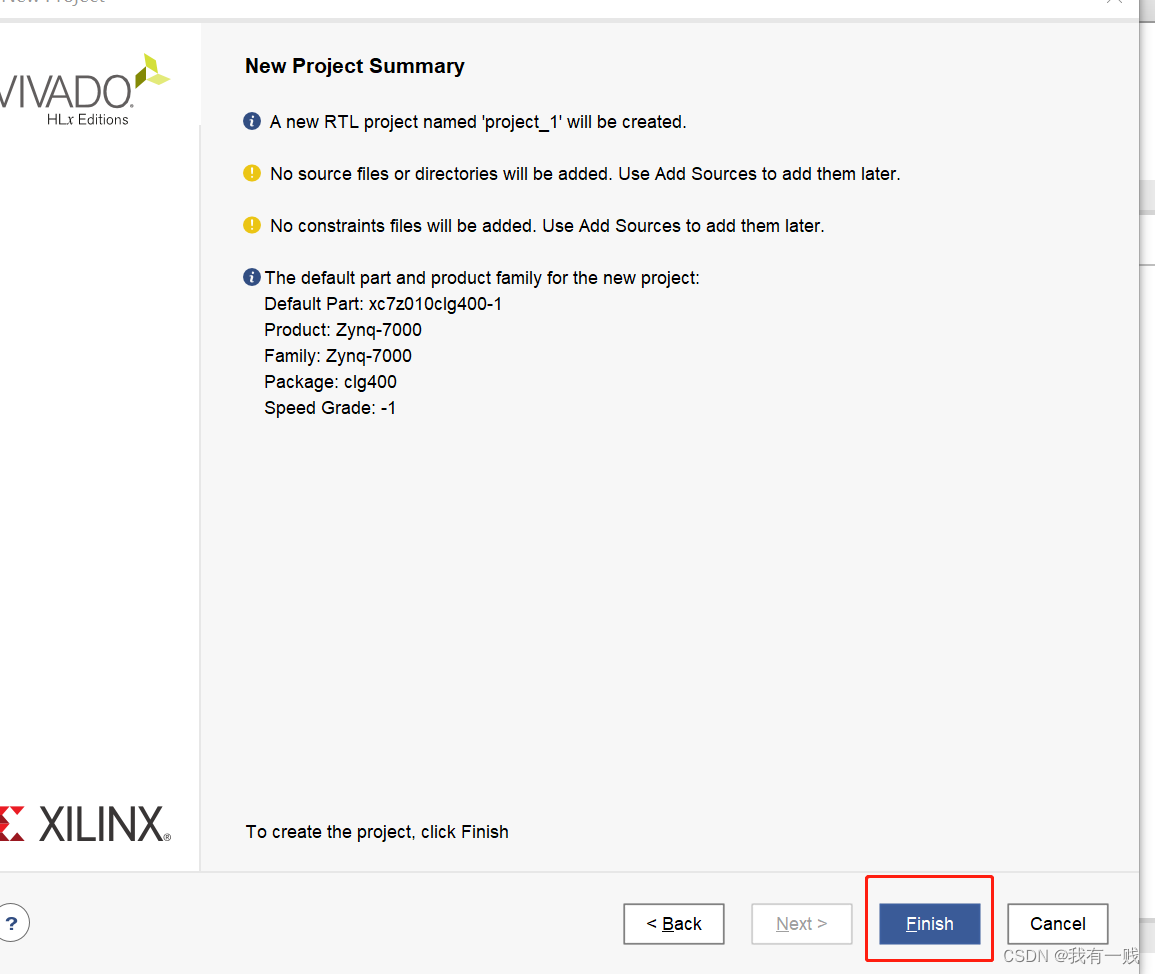

最后点Finish,就算完成了。

最后点Finish,就算完成了。

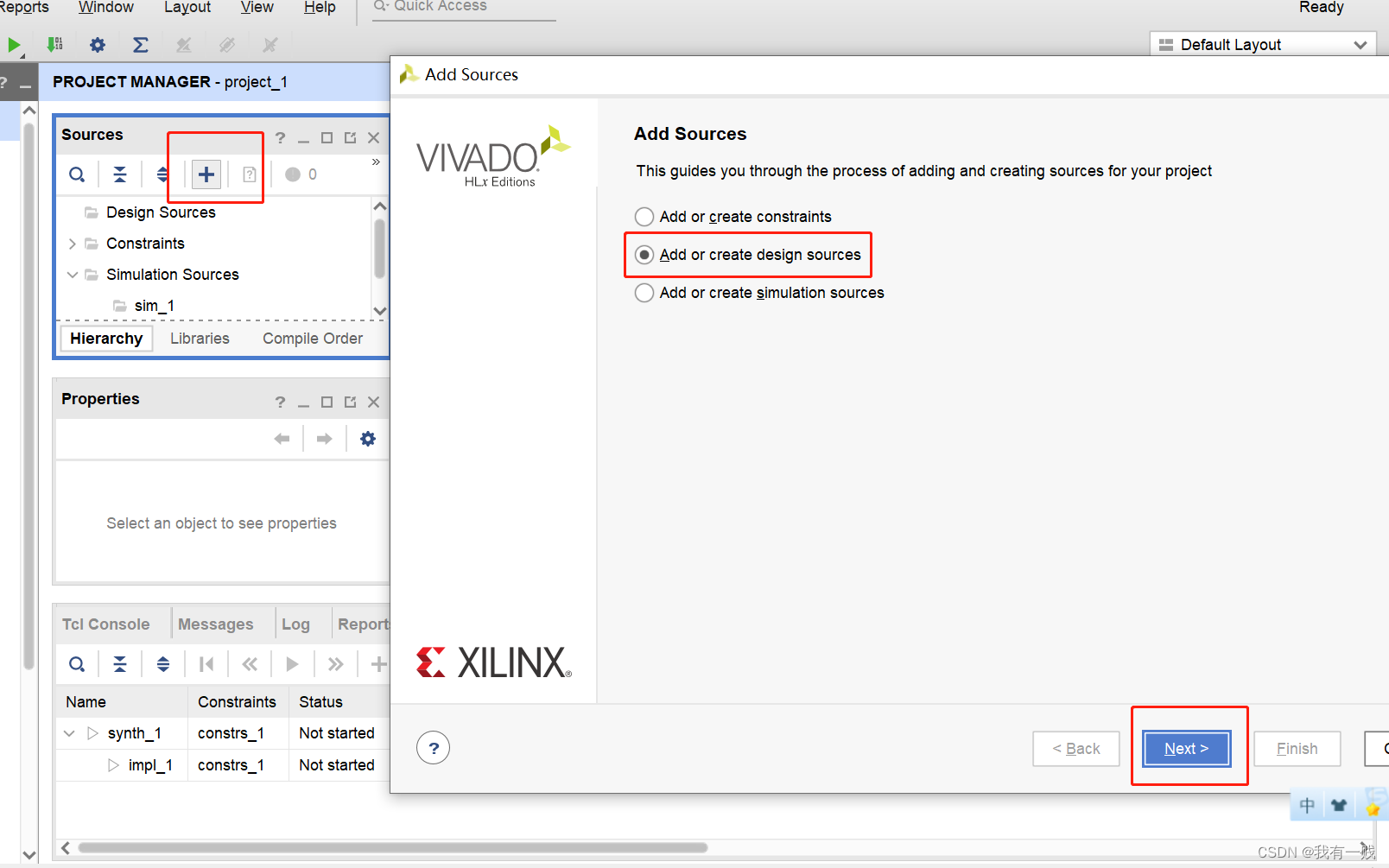

2.创建编程文件 adder

先点 + ,然后在弹出的页面中选择中间的design source,然后Next

点击creat File ,在弹出的界面中,输入上文件名:adder,点击OK。

本文详细描述了如何使用Vivado软件创建并仿真一个四位全加器,包括工程设置、编程文件(adder.v)编写和测试文件(tb_adder)的创建过程,以及仿真结果的展示。

本文详细描述了如何使用Vivado软件创建并仿真一个四位全加器,包括工程设置、编程文件(adder.v)编写和测试文件(tb_adder)的创建过程,以及仿真结果的展示。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1263

1263

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?