名称:基于FPGA的8位全加器设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:8位全加器

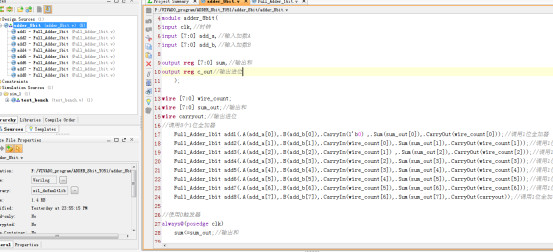

1. 工程文件

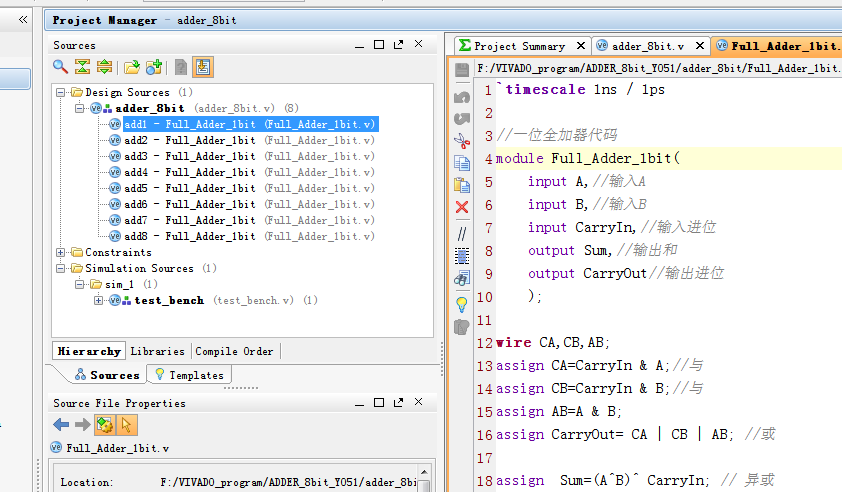

2. 程序文件

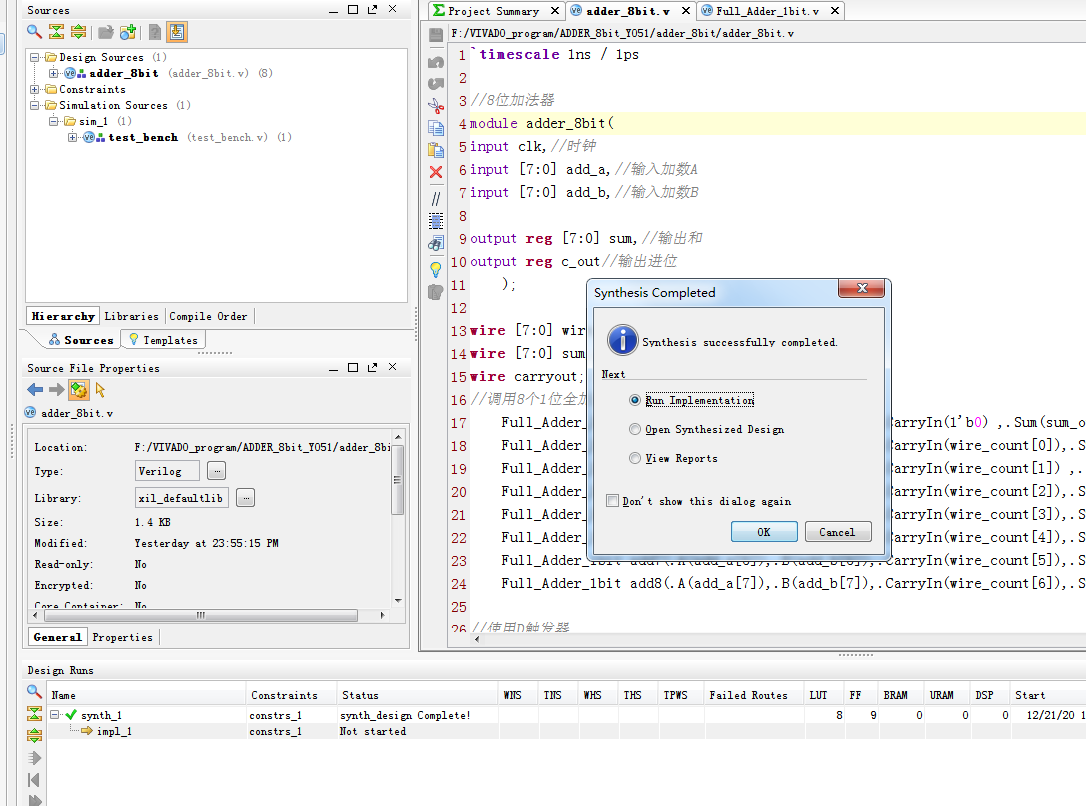

3. 程序编译

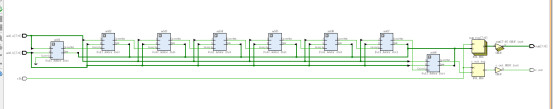

4. RTL图

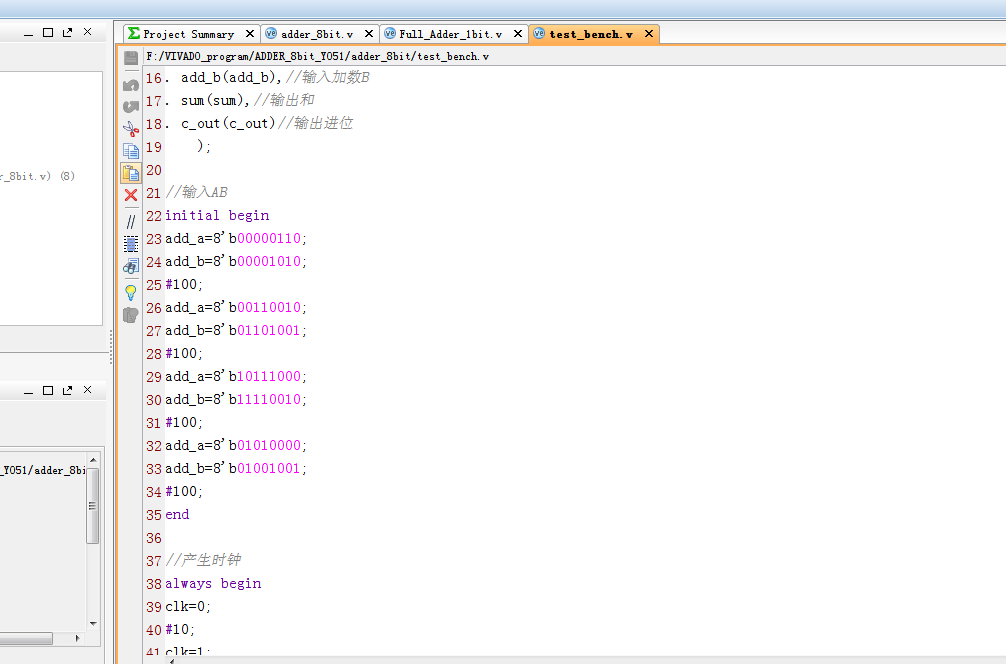

5. Testbench

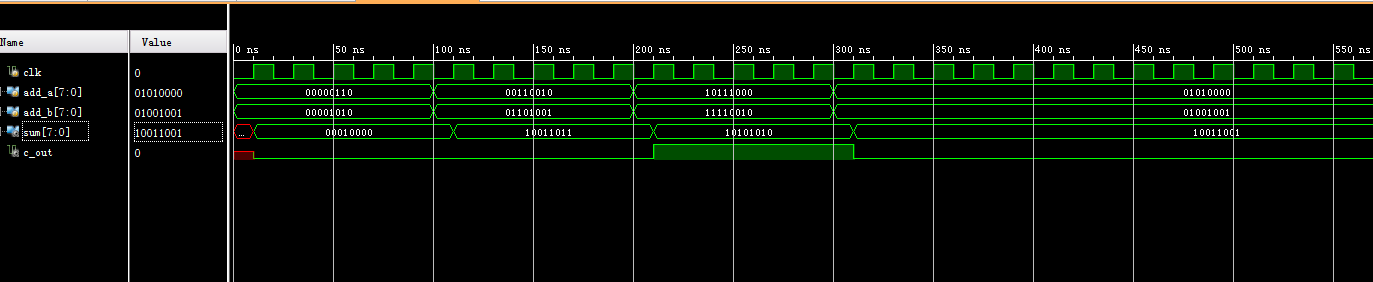

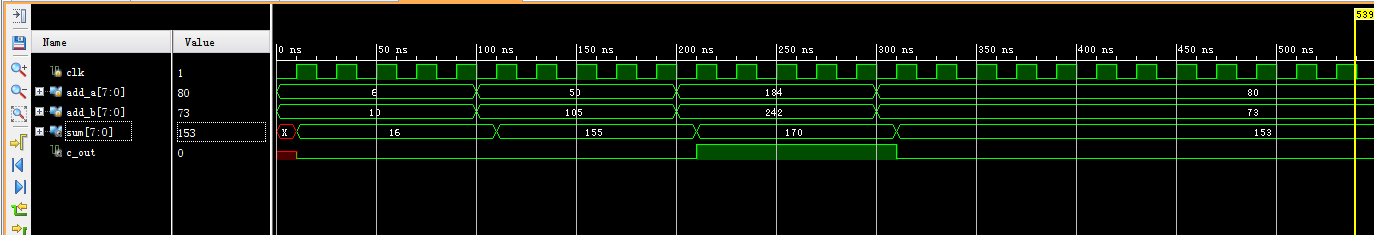

6. 仿真图

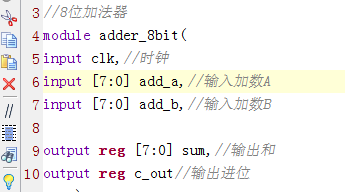

部分代码展示:

`timescale 1ns / 1ps //8位加法器 module adder_8bit( input clk,//时钟 input [7:0] add_a,//输入加数A input [7:0] add_b,//输入加数B output reg [7:0] sum,//输出和 output reg c_out//输出进位 ); wire [7:0] wire_count; wire [7:0] sum_out;//输出和 wire carryout;//输出进位 //调用8个1位全加器 Full_Adder_1bit add1(.A(add_a[0]),.B(add_b[0]),.CarryIn(1'b0) ,.Sum(sum_out[0]),.CarryOut(wire_count[0]));//调用1位全加器 Full_Adder_1bit add2(.A(add_a[1]),.B(add_b[1]),.CarryIn(wire_count[0]),.Sum(sum_out[1]),.CarryOut(wire_count[1]));//调用1位全加器 Full_Adder_1bit add3(.A(add_a[2]),.B(add_b[2]),.CarryIn(wire_count[1]) ,.Sum(sum_out[2]),.CarryOut(wire_count[2]));//调用1位全加器 Full_Adder_1bit add4(.A(add_a[3]),.B(add_b[3]),.CarryIn(wire_count[2]),.Sum(sum_out[3]),.CarryOut(wire_count[3]));//调用1位全加器 Full_Adder_1bit add5(.A(add_a[4]),.B(add_b[4]),.CarryIn(wire_count[3]),.Sum(sum_out[4]),.CarryOut(wire_count[4]));//调用1位全加器 Full_Adder_1bit add6(.A(add_a[5]),.B(add_b[5]),.CarryIn(wire_count[4]),.Sum(sum_out[5]),.CarryOut(wire_count[5]));//调用1位全加器 Full_Adder_1bit add7(.A(add_a[6]),.B(add_b[6]),.CarryIn(wire_count[5]),.

源代码

扫描文章末尾的公众号二维码

1063

1063

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?