欢迎FPGA工程师加入官方微信技术群

点击蓝字关注我们FPGA之家-中国最好最大的FPGA纯工程师社群

最近看了看了一篇《vivado使用误区与进阶》的文章,觉得写得挺不错了,看完后自己对时序分析又有了更深一层的理解,故记录下来。可能排版有些乱,有些图都是直接从文章中截取,但是不影响阅读。

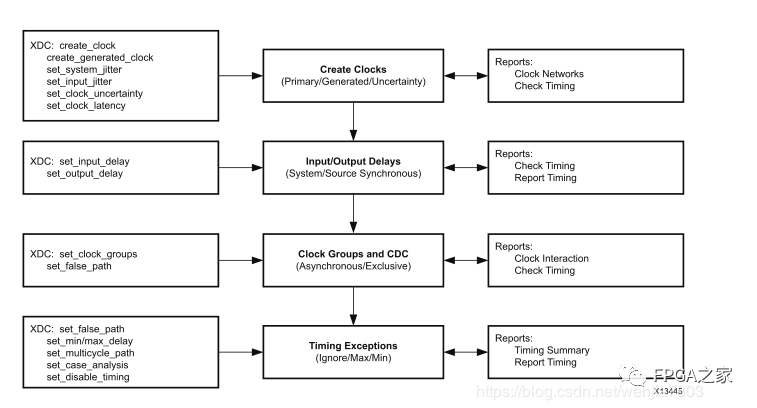

时序分析的基本步骤:

一个合理的时序约束可以分为以下步骤:

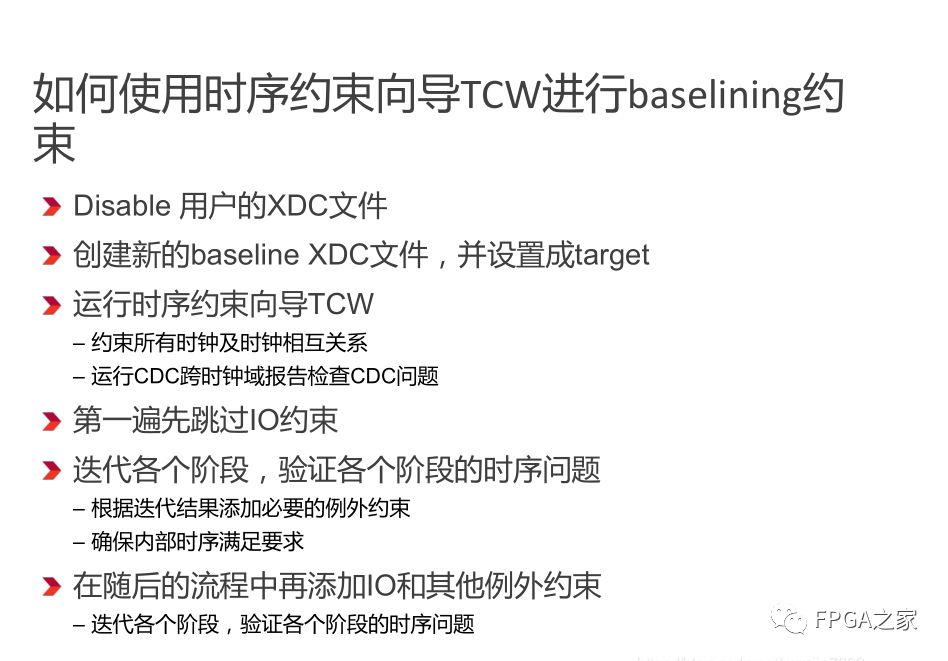

时序约束整体的思路与之前我说的方法基本一致。整体的思路如下:

先是约束时钟,让软件先解决内部时序问题;(在这一步骤中可以适当加入时序例外,以便时序通过)

然后再加入IO的延迟约束;

最后针对没有过的时序,添加时序例外。

在《vivado使用误区与进阶》中,提到了一种叫 UltraFAST 的设计方法。针对下图中所说的根据迭代结果添加必要的例外约束(步骤1),为什么是添加必要的呢?是因为虽然是跨时钟域,但是有时候就算不约束,时序也能过。当碰到时序不过的时候,现阶段可以去针对该部分路径进行时序例外约束,以便后续继续分析。需要注意的是,就算没有报时序为例,现阶段也一定要去留意那些跨时钟的路径(通过clock_interaction),确认代码有没有做相应的跨时钟域处理。针对跨时钟域的代码处理后面会提到。

定义时钟约束

时钟主要可以分为主时钟以及衍生时钟。

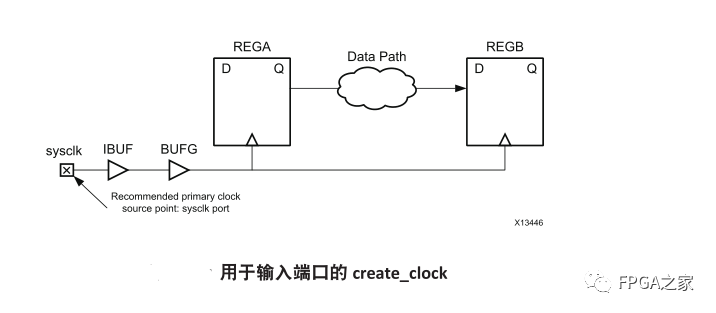

创建主时钟。典型的主时钟根包括有以下几种情况:输入端口、千兆位收发器输出引脚以及某些硬件原语输出管脚。

约束实例 :

create_clock -name SysClk -period 10 -waveform {0 5} [get_ports sysclk]

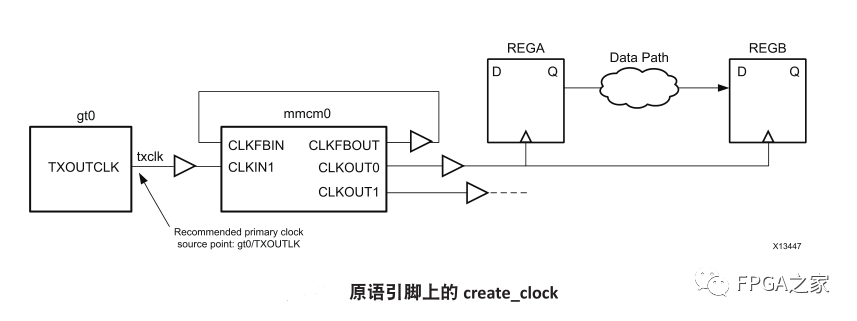

GT 收发器输入引脚,例如已恢复的时钟,

约束实例 :

create_clock -name txclk -period 6.667 [get_pin gt0/TXOUTCLK]

创建生成时钟。

自动衍生时钟

大部分生成时钟都由 Vivado 设计套件时序引擎自动衍生获得,该引擎可识别时钟修改模块 (CMB)及其对主时钟所执行的变换。赛灵思 7 系列器件中,CMB 是 :

• MMCM*/ PLL*

• BUFR

• PHASER*

如果 Vivado 设计套件时序引擎所选择的自动衍生时钟名称并不合适,您可以使用 create_generated_clock 命令强行定义自己的名称,此时无需指定波形转换。该约束应刚好位于约束文件中定义主时钟的约束之后。例如,由 MMCM 实例生成的时钟的默认名称是 net0

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

251

251

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?