一、时序约束是什么?

时序约束(Timing Constraints):用来描述设计人员对时序的要求,比如时钟频率,.输入输出的延时等。比如,对时钟频率的约束最简单的理解就是,设计者需要告诉EDA工具设计中所使用的时钟的频率是多少;然后工具才能按照所要求的时钟频率去优化布局布线,使设计能够在要求的时钟频率下正常工作。

二、为什么需要做时序约束?

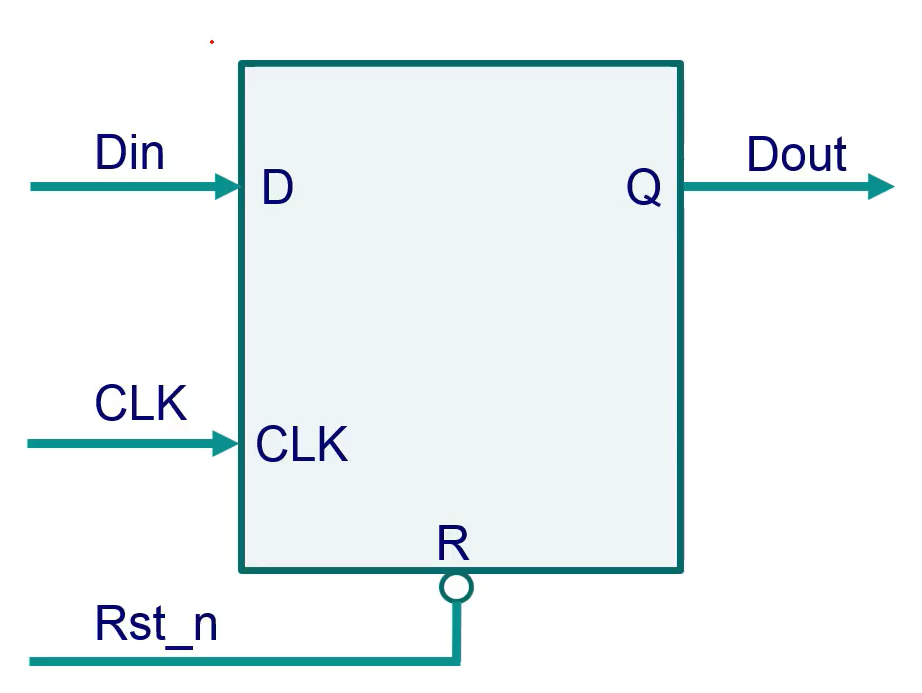

触发器:

建立时间(Tsu:setup time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。

保持时间(Th:hold time):是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th 就是指这个最小的保持时间。

Tco:触发器响应时间,根据不同FPGA 不同工艺决定的。

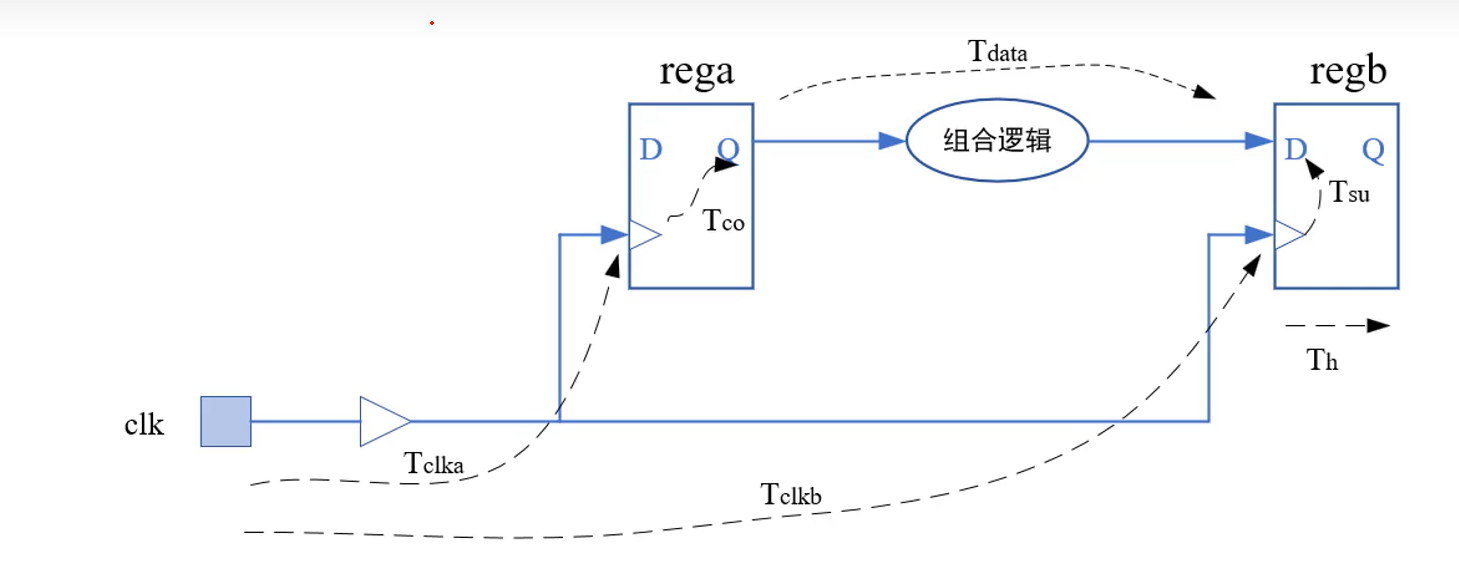

时序模型:

为什么需要做时序约束:通俗的说,就是因为代码写出来的时候,各功能块资源、寄存器资源、布线资源等资源是随机分布的,而布线不同路径导致延时时间不同,这样的话就会导致竞争冒险的出现,因此,为了避免这种情况,必须对fpga资源布局布线进行时序约柬以满足设计要求。

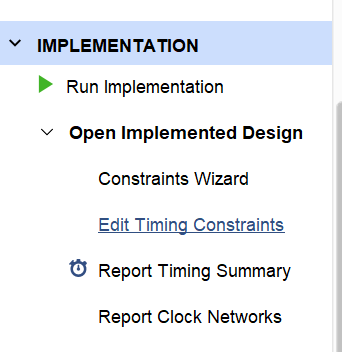

三、创建时序约束

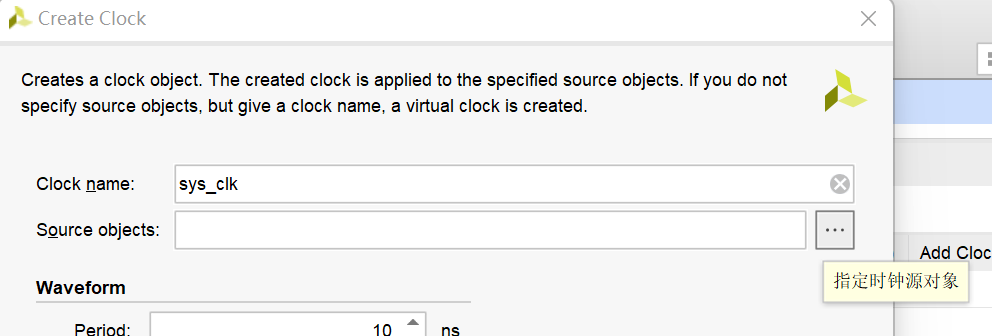

- 打开下图

- 点击 编辑时钟约束

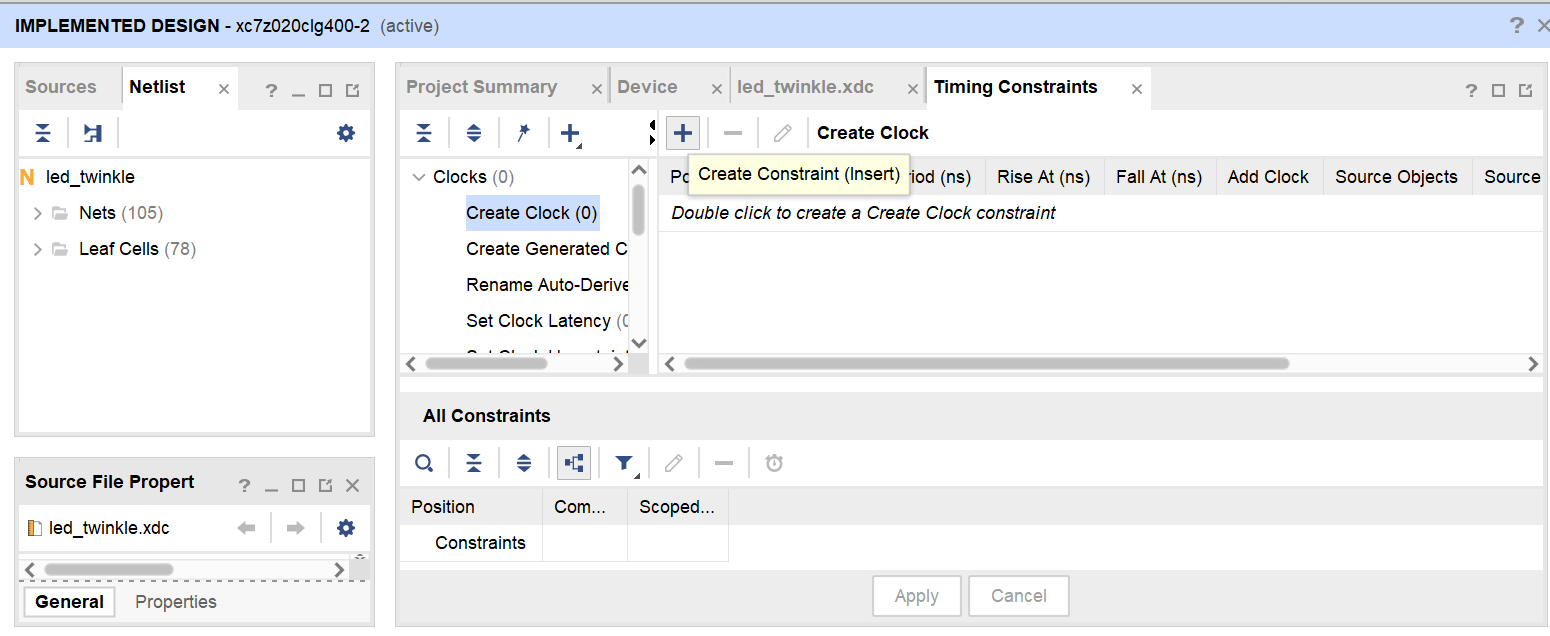

- 点击+号 添加一个时钟约束

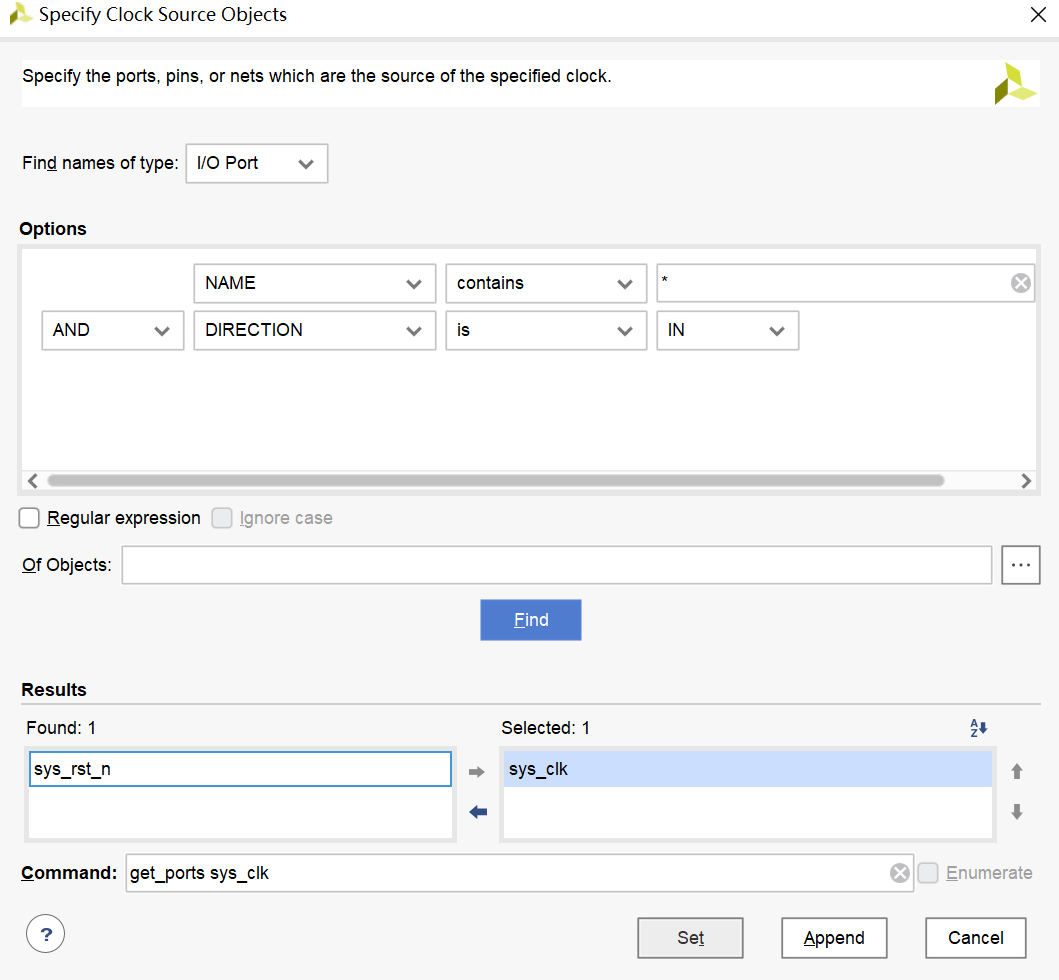

- 点击指定时钟的源 >> 查找find >> 添加所需要的

- 选择I/O端口

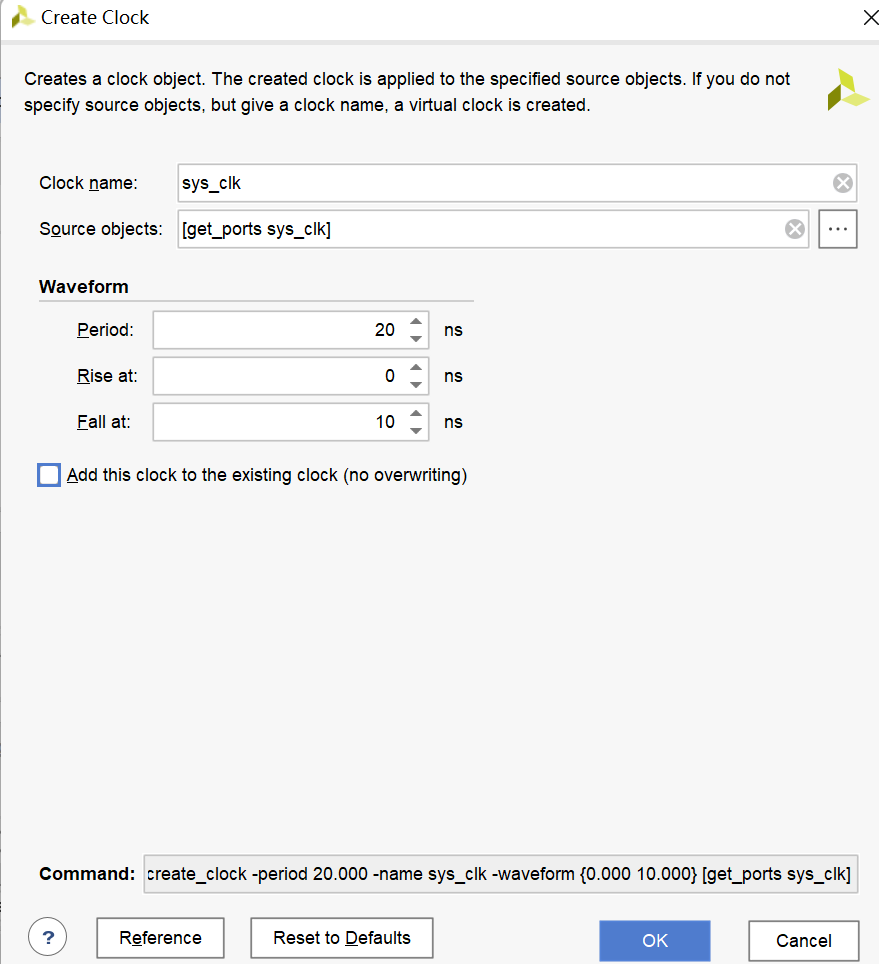

- 选择ok

- 保存后关闭。然后重新生成比特流 可以看到timing如下图所示

- 也可以在xdc文件直接改

create_clock -period 20.000 -name sys_clk -waveform {0.000 10.000} [get_ports sys_clk]

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?