使用

Visual Studio Code

舒适地开发

Verilog HDL

入门级教程

V1.1

By 胖头鱼

前言

距离上一篇教程已经过去了六个月,同学们也经历了一学期的线上学习。经过了数电与电电小学期的洗礼,同学们的硬件编程与debug能力都得到了大幅提升。

然而学期结束后,就在笔者兴高采烈地卸载Quartus II与Modelsim SE时,计原携其实验却无情地打碎了笔者的白日梦,并带来了牙膏厂收购Altera后的船新版本:Quartus Prime。现在再看上一篇教程,内容未免有些naive,值得做出一定的补充了。因此,笔者在开学第二周,牺牲了宝贵的睡觉(玩手机)时间写下了这篇教程,权当补充。

本教程在V1.0基础上写成,但碍于篇幅限制,V1.0中的大部分内容不再赘述,且本教程较V1.0更为简略。建议未阅读过上一篇教程的读者先阅读V1.0再阅读本文。

更新日志:

改进V1.0中的部分细节

增加利用modelsim自动查错的内容

增加利用iStyle一键排版的内容

增加利用命令进行分析综合与仿真的内容(Optional)

本教程部分内容来自GitHub, CSDN, VS Code Docs等。

V1.0教程点这里

Part I

V1.0教程改进

Quartus II

Visual Studio Code

的链接

V1.0原文

我们的Verilog环境搭建好了,但我们平时一般不会直接对.v文件进行操作,都是在Quartus II工程里编辑代码。幸好Quartus比较有至知之迷,可以自行设置偏好的文本编辑器。这样一来,我们就可以在Quartus中双击.v文件用Code打开了。

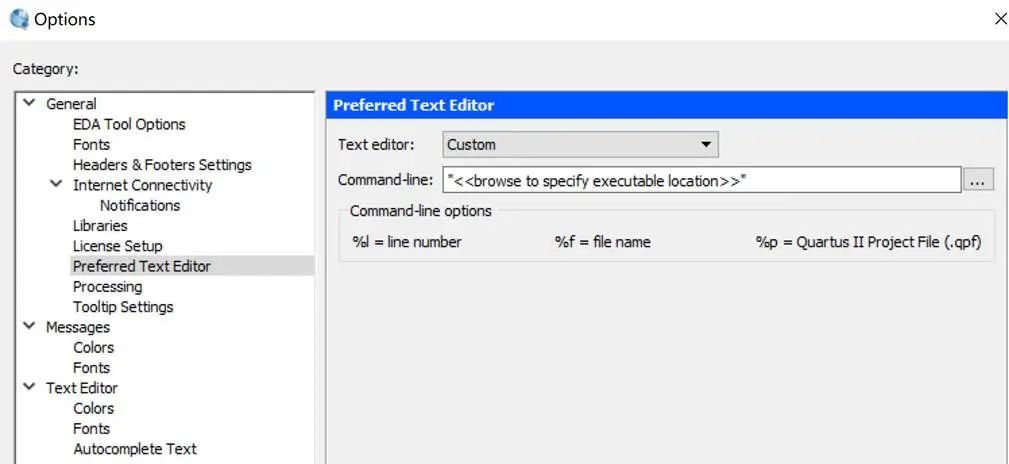

启动Quartus,点击Tools -> Options -> Preferred Text Editor。在下拉菜单中选择编辑器类型。这里Visual Studio Code并没有单独的选项,我们只得选择Custom。

选择外部编辑器

此时我们需要在引号中填上我们的Code的主程序的位置。默认该位置是C:\Users\(我们的电脑账户名)\AppData\Local\Programs\Microsoft VS Code\Code.exe。大家可以通过右边的浏览按钮在文件管理器中找到这个位置(“用户”就是“Users”)(这里可能需要更改文件管理器设置以看到隐藏的AppData文件夹)。然后在引号后面写上%f %l(就是下面的那个%f和%l),这样当Quartus调用Code的时候Code就知道该打开哪个文件了。完成后点击OK即可。

配置VS Code命令

此时我们再在Quartus双击.v文件时,它便会自动用Code打开。我们在Code中写完代码保存,可以回到Quartus进行其他操作,如生成符号文件等。

V1.1改进

长期使用VS Code后,笔者发现,上述方法存在一个和VS Code设计初衷相悖的问题:此命令(code %f %l)只能单独打开目标.v文件(打开后最下面状态栏是紫色的),而不能打开其所在文件夹(通常刚好是Quartus工程目录)(打开后最下面状态栏是蓝色的),这为许多后续的操作造成了麻烦。

实质上,这一步的原理是,Quartus主程序执行这一行命令,以调用目标编辑器,并将参数传递进去。因此,通用的在CMD控制台调用Code的方法这里也可以借鉴。通过查阅VS Code文档:

https://code.visualstudio.com/docs/editor/command-line

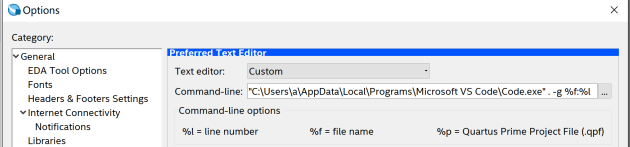

可知,若想使用Code打开目标文件夹,只需要执行>code . 即可。而若想将行号这一信息传递进去,则需要使用-g或--goto参数。

因此,我们可以将那一行命令修改为:

"C:\Users\***\AppData\Local\Programs\Microsoft VS Code\Code.exe" . -g %f:%l

配置VS Code命令

此时我们再在Quartus双击.v文件时,它便会自动用Code打开,且打开其所在的文件夹。当我们在Quartus里双击编译错误提示时,能够自动转到VS Code中对应文件的对应行。

Ctags 配置

V1.0原文

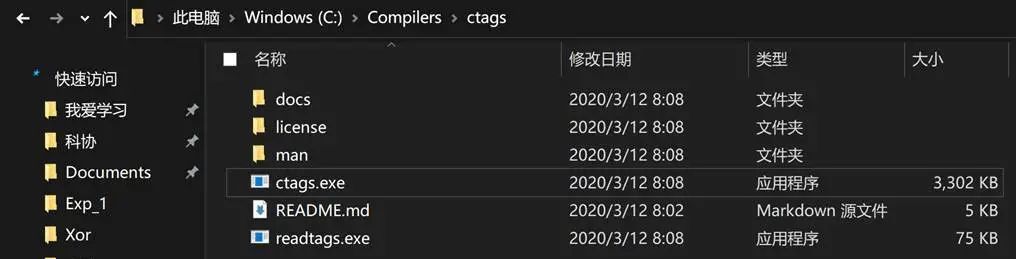

将下载好的压缩包解压缩,并将其拷贝到一个好找的目录下。我自己放在了C:\Compilers\ctags,我的Compilers文件夹里还装了很多其他的小工具,大家可以按自己的习惯选择位置。注意ctags.exe等文件应当恰好放在这个目录下,而非此目录的某个子目录下。

ctags.exe所处的位置

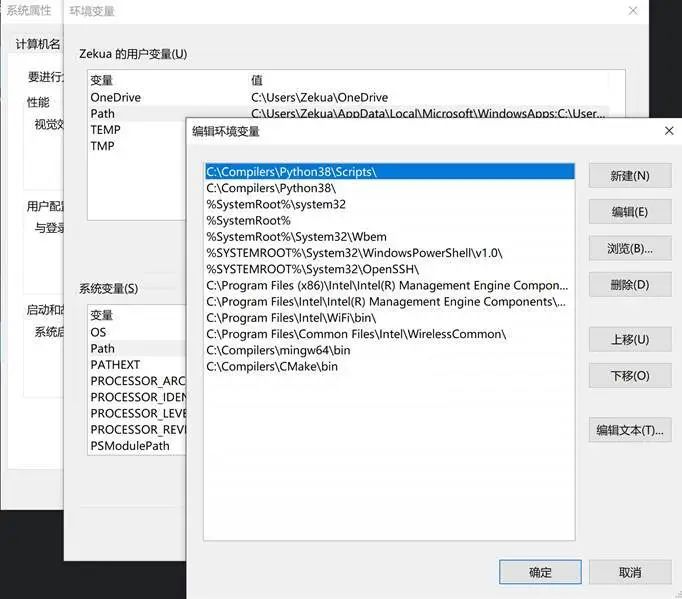

Ctags安装好了,但Code并不知道去哪里找到这个程序。因此,我们需要在系统里设置一些“超链接”来让Code和其他的程序方便地调用Ctags:设置系统环境变量。

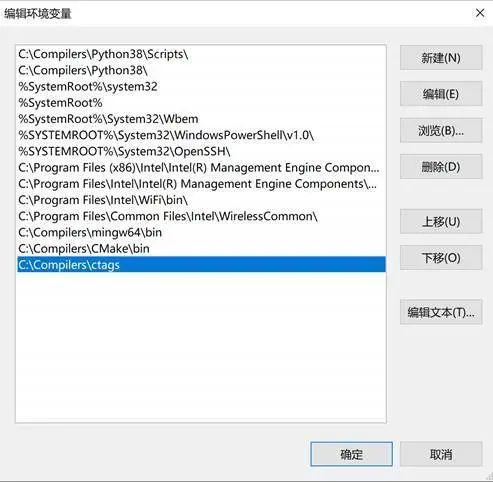

打开“编辑系统环境变量”:控制面板->系统和安全->系统->高级系统设置->环境变量…(可以直接在开始菜单搜索“编辑系统环境变量”)。点击“环境变量…”,进入环境变量设置界面。

在系统变量列表中选中Path,双击编辑。点击“新建”,再点击“浏览…”,找到刚才ctag.exe所在的目录。点击很多次确定退出,我们就完成了系统环境变量的配置,Code便可以直接调用Ctags。(注意这里点取消或关闭窗口都不会保存更改)

编辑环境变量

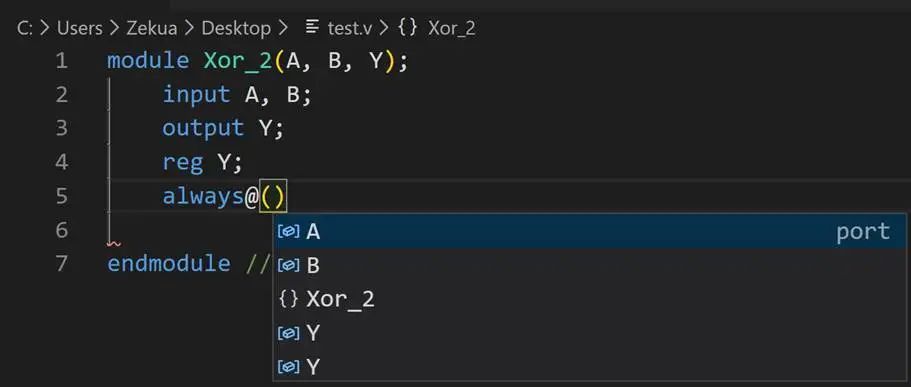

此时重启Code,在Code中编辑.v文件的时候,一些情况下(如always@语法中)便可在候选框中看到我们自己定义的变量或模块等。

候选框中出现了端口名

V1.1改进

教程发出的当天,就有巨佬在评论区提出,这里修改系统环境变量会增大系统的不稳定性。因此,还是修改用户的环境变量比较保险,且效果几乎一致,不影响使用。

事实上,上述步骤几乎无需改动,只需在环境变量设置界面中选中***的用户变量而非系统变量即可,其余步骤不变。

Part II

使用Modelsim

自动查错

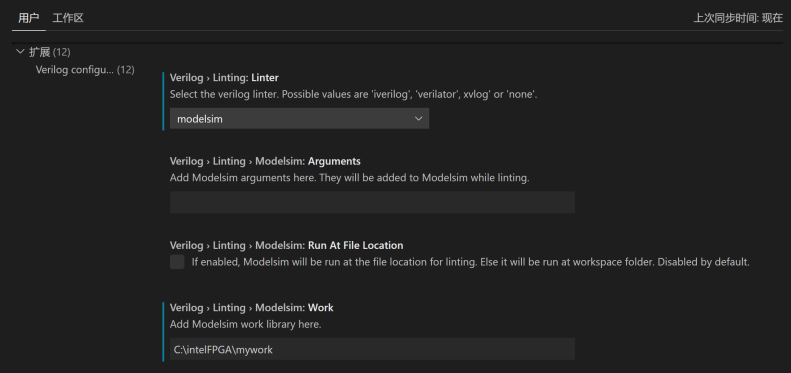

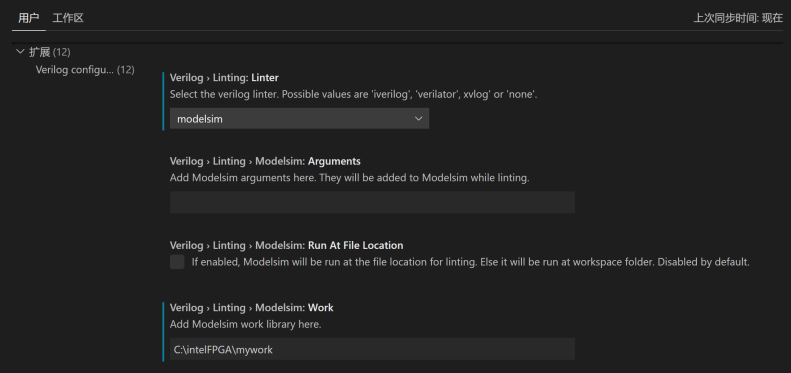

V1.0教程中提到,我们使用的Verilog扩展存在linter(代码自动查错)设置项,并配置了iverilog作为linter。然而可以发现,Modelsim本身也出现在了linter列表里,因此理论上Modelsim也可以被配置为linter。

扩展设置中的Linting相关项

与通常的编译器不同,Modelsim的运行依赖于库(work library),且库常常在每次新建工程时同时建立。当然,不同工程对应的库的内容是几乎一样的,都是通用的器件与组件信息等。Modelsim当然也明白这一点,因此每次随工程新建的库实际上主要包含的是一组映射(mapping),并不会真的把所有的文件全都复制一份。我们若想调用Modelsim作为linter,同样也需要建立一个类似的库才能正常运行。

由于同学们平时Modelsim的使用主要集中在仿真,并没有体验过从新建工程到完成仿真的全流程,因此手动新建一个库是比较难以操作的。然而事实上,Quartus在调用Modelsim执行仿真的时候,同样需要新建一个配套的库,且其映射应当已经设置完毕。所以,我们只需借用这个库即可。

若想利用VS Code调用Modelsim,同样地,我们需要先将Modelsim的主要程序目录添加为环境变量。一般情况下,这一步在Modelsim安装时已由安装程序完成。保险起见,我们也可以打开环境变量列表查看是否已经添加Modelsim程序所在目录(通常为***\modelsim_ase\win32aloem)。

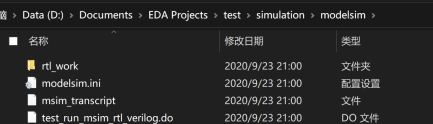

为了利用Quartus生成的库,我们需要进行一次Quartus工程的编译与仿真。如果读者已有现成的仿真完成的工程,且工程文件夹内有simulation\modelsim\rtl_work文件夹,可跳过此段。

Quartus中新建工程,设置仿真器为Modelsim-Altera,语言选择Verilog HDL。新建Verilog文件,简单编写一个模块的代码,只需能够通过编译即可。将其设为顶层,点击Start Analysis & Elaboration,编译完成后点击Tools -> Run Simulation Tool -> RTL Simulation。若先前设置无误,则Quartus将调用Modelsim进行仿真,就像平常那样。结束仿真,打开工程文件夹,确认存在simulation\modelsim\rtl_work文件夹即可。这个文件夹内便存放着Quartus调用Modelsim时生成的库。

Modelsim可用的rtl_work库

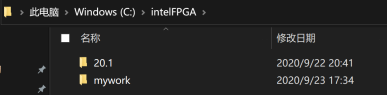

接下来,复制整个rtl_work文件夹到一个熟悉的地方。笔者将其复制到了Modelsim的安装目录下C:\intelFPGA,并进行了重命名。注意不要复制到C:\intelFPGA\20.1及其子文件夹,因为20.1文件夹需要管理员权限才能访问,而Modelsim通常并不具有管理员权限。

保存自己的库

此时,只需在VS Code的扩展设置页面将linter设为modelsim,并将我们自己的库的目录粘贴在对应位置即可。

更改扩展设置,将modelsim设为linter

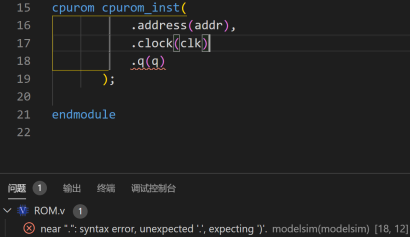

至此,Modelsim在Code中的配置完成了。每当大家保存当前文件的时候,程序都会自动执行一次Modelsim的vlog.exe程序进行查错,并且把错误信息显示在控制台窗口里。如果看不到错误信息,可以点击左下角的×和!按钮即可看到“问题”窗口。

这是我第二次看到错误提示这么高兴

Part III

使用iStyle

一键排版

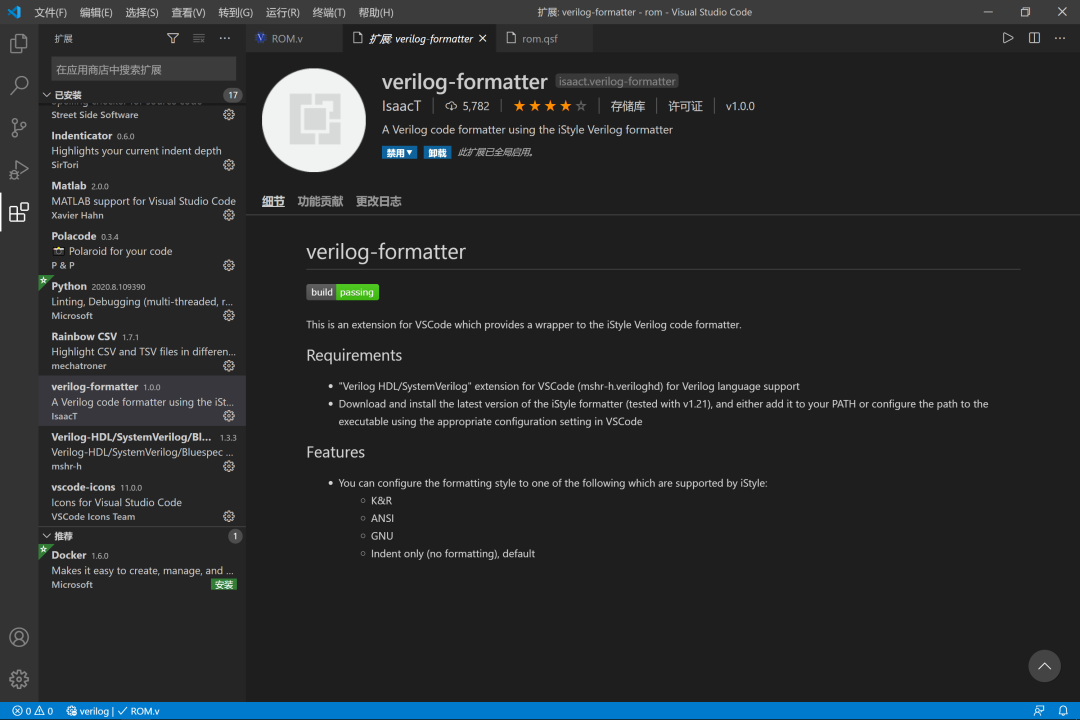

iStyle是一款针对Verilog的排版程序,灵活性极高。利用VS Code的verilog-formatter插件,我们能够使用iStyle对.v文件进行自动排版。

verilog-formatter扩展页面

首先,我们需在VS Code中安装verilog-formatter扩展。可以看到,在扩展的介绍页中注明了,它需要搭配Verilog HDL/SystemVerilog扩展,以及v1.21及更新的iStyle进行使用。Verilog HDL/SystemVerilog扩展我们自然是装好了的,接下来只需准备好iStyle即可。

熟悉利用makefile进行c++多文件编译的同学,可以到

https://github.com/thomasrussellmurphy/istyle-verilog-formatter

下载最新的iStyle源码并进行编译得到iStyle.exe(推荐)。而对上述操作不熟悉的同学,可以到云盘下载笔者编译好的iStyle.exe文件:

https://cloud.tsinghua.edu.cn/d/10ea979850ce4cbb8430/

与Ctags相同,iStyle.exe同样应被妥善保存,并添加到环境变量。笔者将其放在了C:\Users\***\Compilers\iStyle目录,保证iStyle.exe恰好放在这个目录下。

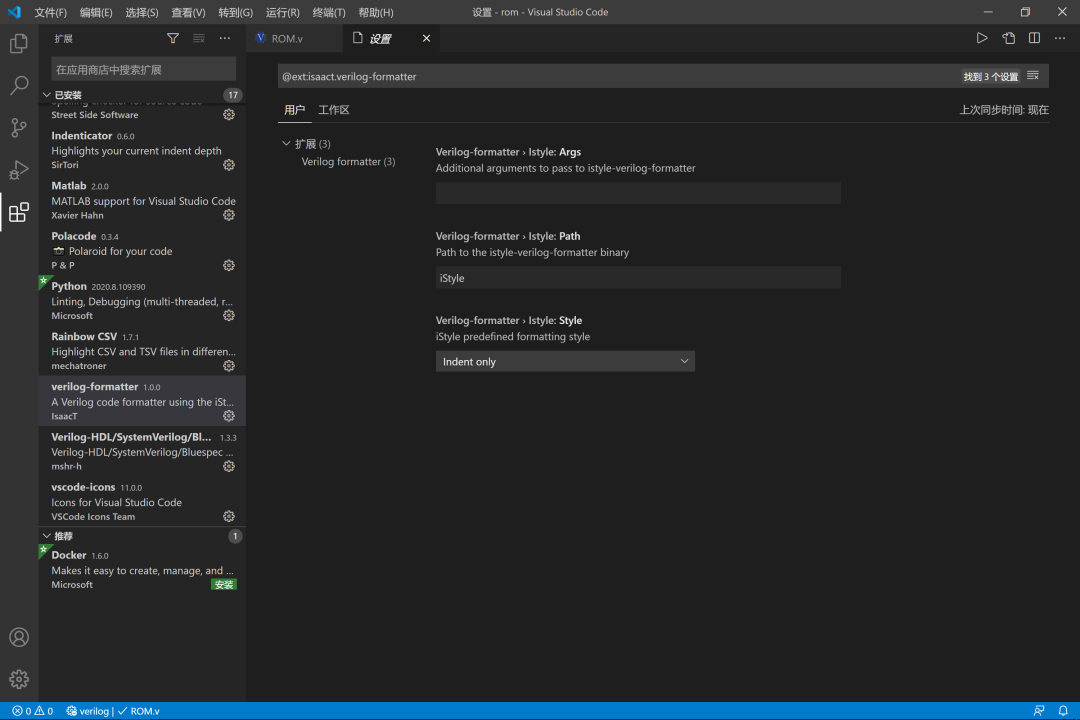

上述步骤均完成后,可检查verilog-formatter扩展的配置页面。由于我们已将iStyle添加到环境变量,因此三项设置均采用默认即可。

verilog-formatter配置页面

至此,我们在VS Code中编写.v文件时,按下Alt+Shift+F快捷键,便能够对整个文档进行默认格式的自动排版。当然,iStyle支持自定义格式排版,具体设置方法可参考iStyle的Github页面,对应设置其命令行参数args。

值得注意的是,假如按下快捷键无法进行排版,且CMD运行> iStyle命令报错,有可能是系统中缺少c++编译器(及其附属dll文件),例如卸载了Visual Studio等。这种情况下可下载安装c/c++的轻量级编译器gcc/g++(即mingw-w64)或其他编译器(如clang等)便可解决问题。具体步骤可参考VS Code配置C++环境的教程。

Part IV

命令行

(Optional)

Quartus与Modelsim实在是太庞大了!事实上,它们如此臃肿的原因之一,是它们包含了许多工具包,且图形界面本身(GUI)就占去了不小的资源(参考MATLAB)。假如我们能够尽量避免全盘地调动起整个Quartus或者整个Modelsim,那么或许能够一定程度上缓解系统的压力。用好命令行便能够做到这件事。

此外,用命令行看起来很酷。

然而由于笔者水平有限,因此这一部分仅能够提供一个不够完美的参考。具体而言,该部分包含了使用命令行进行分析综合与仿真这两部分,而配置testbench等内容并无涉及。欢迎大家和我交流。

使用命令行执行分析综合

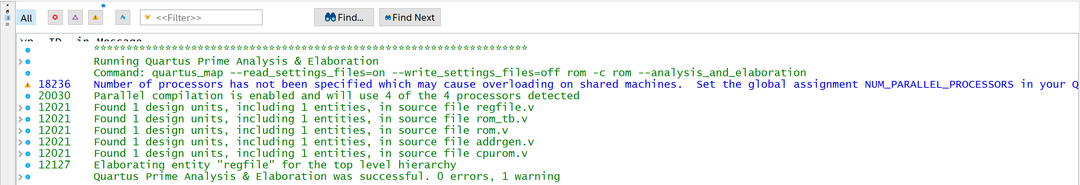

在Quartus GUI中,当我们对工程进行分析与综合时,可以看到,其信息提示中开头有这样一行:

Info: Command: quartus_map --read_settings_files=on --write_settings_files=off -c

这一行命令,便是执行分析综合所用的命令。

Quartus GUI中的信息提示

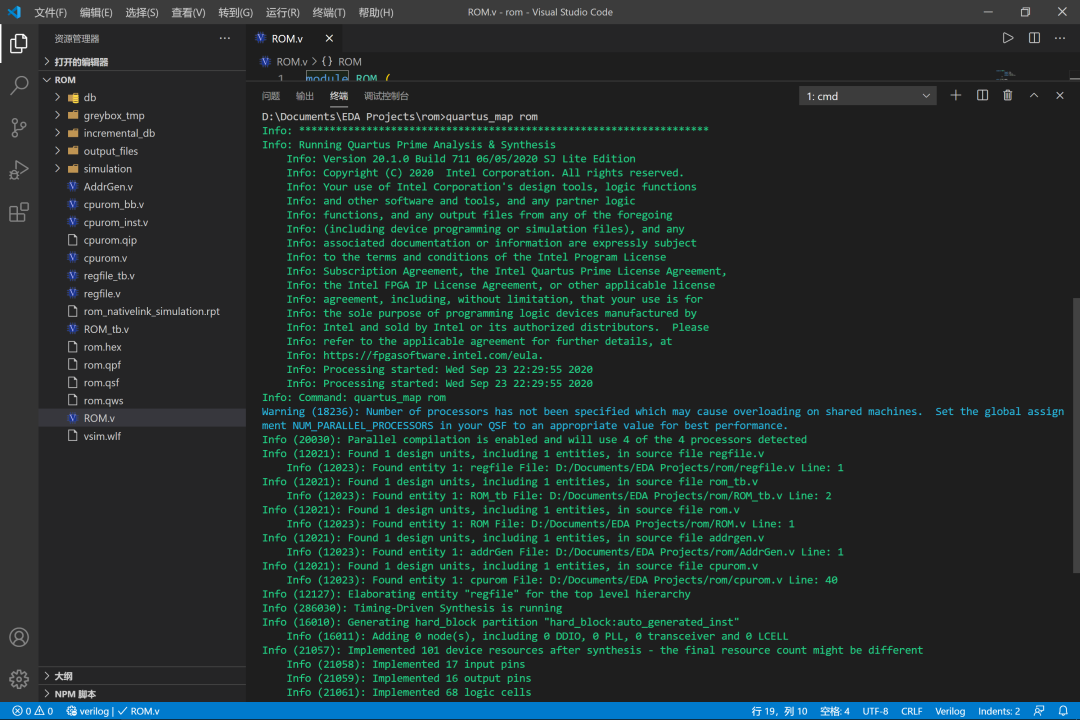

因此,我们可以在VS Code自带的CMD窗口中直接执行这一命令,以对当前工程进行分析综合。事实上,在敲命令时,只需写> quartus_map 即可,其余参数可以直接使用默认值,当然也可以仿照上图,将涉及到的参数全部列出。

使用命令行执行分析综合

可以看到,在Quartus的众多程序中,quartus_map是负责分析综合的那一个,因此我们用命令行直接执行它可以省去诸多麻烦。

注:

应确保VS Code打开了该工程文件夹,而非仅打开.v文件。事实上,应确保CMD中quartus_map运行在工程目录下。

为在CMD中调用quartus_map,应事先将其所在的Quartus的可执行文件(quartus_map等)所在目录添加到环境变量。

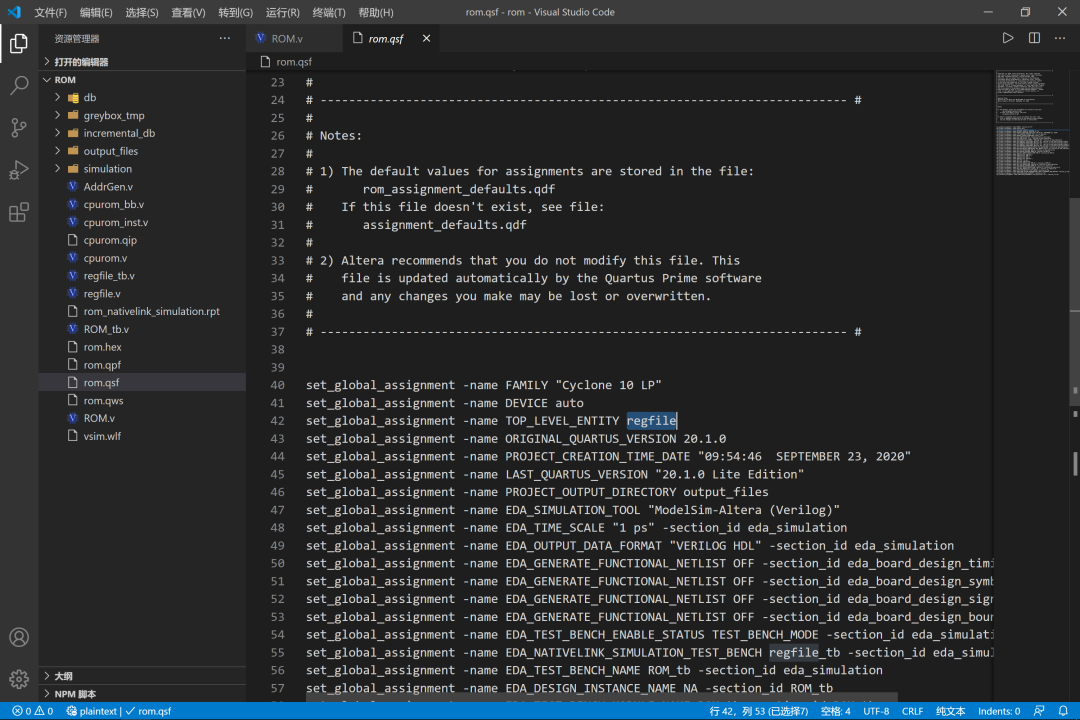

与在Quartus GUI中的操作相同,应首先设定工程的顶层实体。具体而言,可通过编辑.qsf(可用Code打开)实现。此外,在这里所做的手动更改会在Quartus GUI执行分析综合时更新到GUI里。

修改qsf文件以确定顶层实体

使用命令行进行仿真

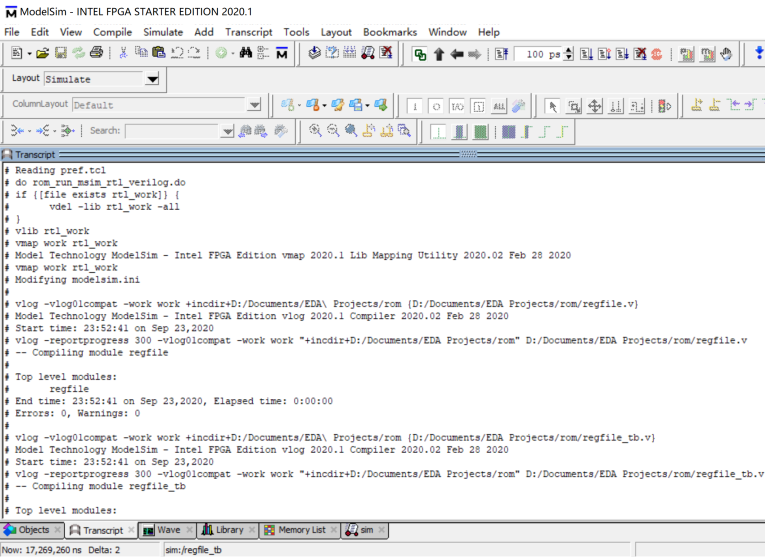

在Quartus GUI中,当我们对工程进行Modelsim仿真时,在Modelsim的Transcript窗口可以看到,其开头有这样一行:

do rom_run_msim_rtl_verilog.do

Modelsim Transcript窗口

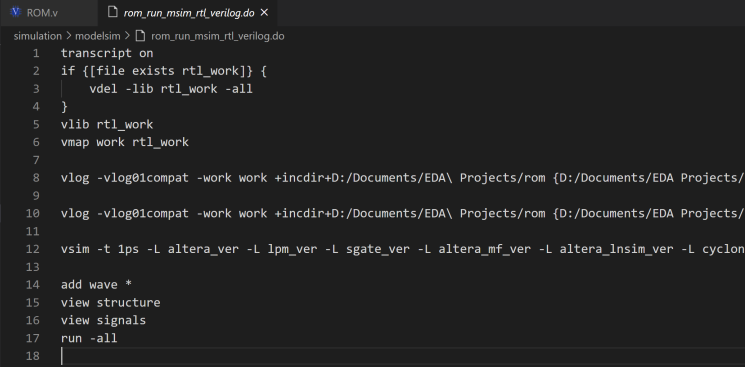

在Modelsim中,.do是一种可执行的脚本文件。也就是说,当Modelsim执行这一行命令时,它实际上在顺序执行这个.do文件里的每一行命令。在VS Code中很容易看到,这个.do文件所处的位置和先前的rtl_work一样,都在\simulation\modelsim文件夹下。

*.do脚本文件内容

打开这个.do文件可以看到,其内容和先前Transcript中的内容十分相近。Transcript窗口中的内容实际上就是Modelsim执行.do文件中每条指令的内容和结果。换言之,.do文件的命令加在一起就实现了整个仿真的操作,而.do文件是由Quartus在分析与综合时生成的。

因此,我们可以直接让Modelsim在Quartus GUI之外,在命令行中也执行相同的.do脚本文件,便也能依葫芦画瓢,实现整个仿真了。

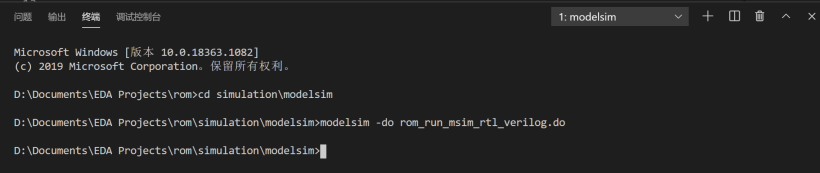

为了让Modelsim工作在\simulation\modelsim文件夹下,需要首先使用cd命令更改CMD所在的目录,然后在CMD中使用Modelsim命令,将.do文件作为参数传入即可。具体命令如下:

[project_folder]> cd simulation\modelsim

[project_folder]\simulation\modelsim> modelsim -do _run_msim_rtl_verilog.do

使用命令行执行仿真

注:

在调用命令行执行仿真前,应确保先对工程执行过分析综合(GUI或命令行均可),否则没有生成.do脚本文件。

testbench的配置仍需要在Quartus GUI中完成。

写在最后

“其实还是自己养成规范码代码的习惯更好一点。”

——hls

若想玩转Quartus命令行,可以参考

https://www.intel.cn/content/dam/www/programmable/us/en/pdfs/literature/manual/tclscriptrefmnl.pdf

本人水平有限,大家若发现了教程的bug或有更好的方案,欢迎和我交流。

祝大家Coding愉快!

— END —

本文是关于如何使用Visual Studio Code (VS Code)舒适地开发Verilog HDL的教程,重点介绍了如何配置VS Code与Quartus II和Modelsim的集成,包括设置VS Code为Quartus的默认编辑器、利用Modelsim进行自动查错以及使用iStyle进行代码排版。此外,还提到了通过命令行进行分析综合和仿真的方法。

本文是关于如何使用Visual Studio Code (VS Code)舒适地开发Verilog HDL的教程,重点介绍了如何配置VS Code与Quartus II和Modelsim的集成,包括设置VS Code为Quartus的默认编辑器、利用Modelsim进行自动查错以及使用iStyle进行代码排版。此外,还提到了通过命令行进行分析综合和仿真的方法。

1587

1587

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?