- schematic design

有两个工具支持:Allegro Design Entry HDL (concept)和OrCad capture CIS。似乎业界多用OrCad capture CIS。 以前的项目用过concept。

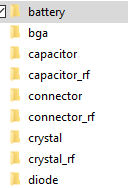

如果使用concept,元器件库需要做以下几点:

- 元件库生成 (使用它project manager->Allegro PCB Librarian XL)http://blog.chinaunix.net/uid-24343357-id-3265826.html

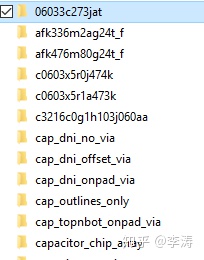

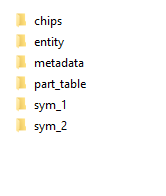

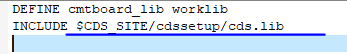

- 放置所用的setup file到一个公用folder,定义环境变量Cds_site指向这个folder. ./cdssetup/cds.lib定义了所用库单元的路径

- 将做好的元件单元库放入路径内

当使用Concept做一个新的design的时候,会在项目folder下生成一个cds.lib,该文件内容指向library setup

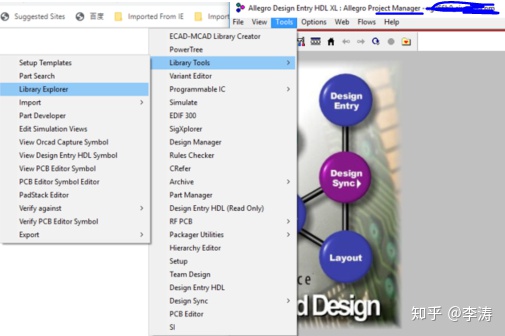

- 如何将Concept的library转为orcad的library

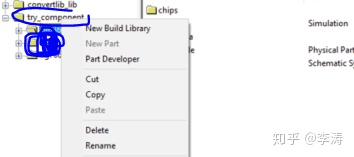

使用Library Explorer创建一个新的项目,然后修改cds.lib加载所有需要转换的concept库单元。

重新打开项目后会看到所有的库单元,右键选择“Part Developer“打开一个新的”Part developer“的工具。

选择file->Import and Export找到”Export Capture Parts"

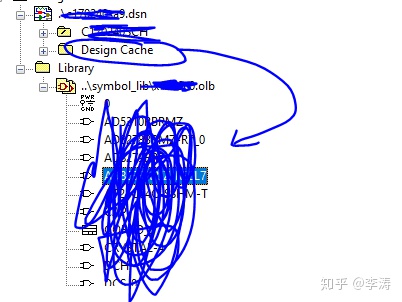

- 如何将一个schematic设计的原件库导入自己的库

用OrCad capture打开该dsn文件,design cache会有一些库单元。将这些库单元选中右键“copy”。然后在“Library”加载自己的元件库,右键“paste”就可以得到这些库单元

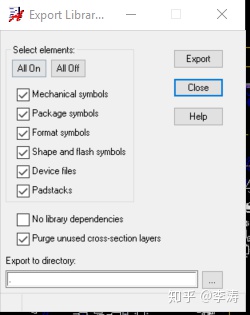

- 如何从pcb文件brd导出封装库

如果文件没有lock,可以简单 File->Export->Library就可以了

- 板子厚度

6.0 mm +/- 0.25mm --> 40 layers boards?

- trace和电流的关系

For a width of 0.25mm with thickness of copper of 35µm , the current is 0.700 mA

For 0.3mm -> 0.9 mA

For 0.5mm -> 1.5 A

For 0.7mm -> 1.9 A

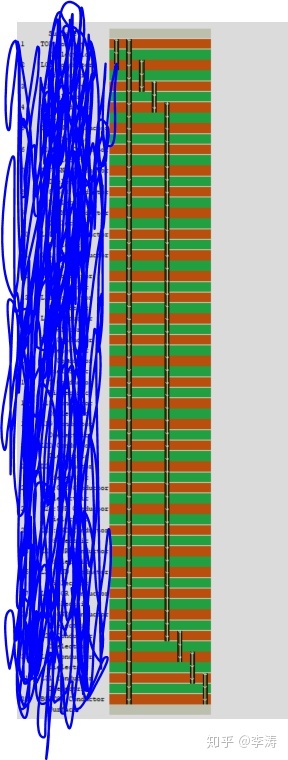

- 叠层设计

需要理解材料如何选择,层厚,线宽....etc

需要和PCB板卡商确定材料类型(conductor和dielectric),厚度,介电参数...etc. 线宽需要根据叠层设计和PCB板卡商确认(50 ohm,100 ohm, 45 ohm...ect)

- 盲埋孔的设计

setup -> Cross-section可以看层结构。View->show Drill chart 可以看过孔。如果看到盲埋孔,需要看 setup-> BB Via definition -> define BB via 知道这些盲埋空如何定义的。

- Report generation

Tools-> Reports可以产生各种report,需要看看哪些report是有用的可以加到checklist中去

- 约束管理器的使用

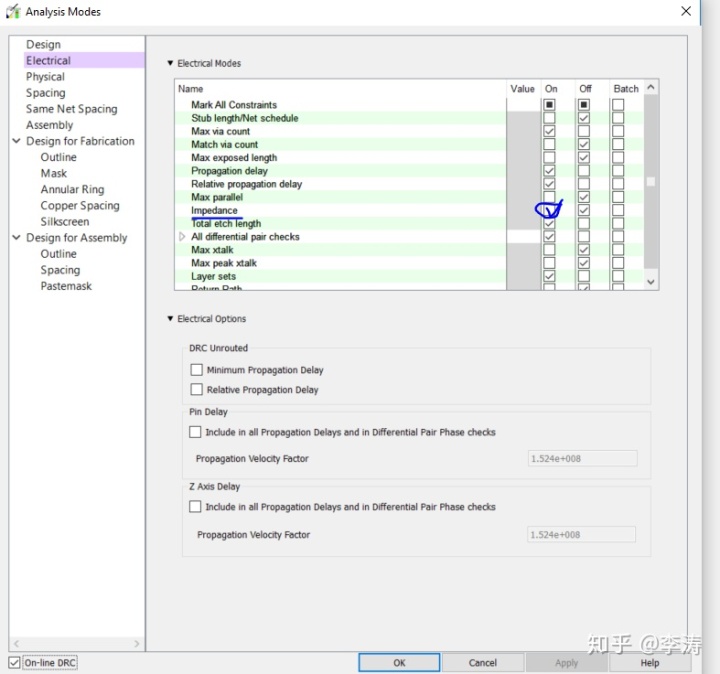

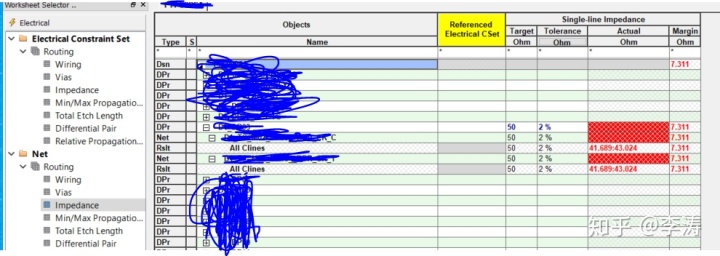

约束定义好了并且走线之后,我们需要使用约束管理器去检查所有约束是否满足。步骤如下:

- 打开Allegro Constraint Manager (Setup -> Constrains->Constrains manager)

-打开Analyze-> Analyze Modes确保关心的参数被选取了(比如下图的impedance)

-回到constraint的主页面,在关心的参数点击analyze可以看结果

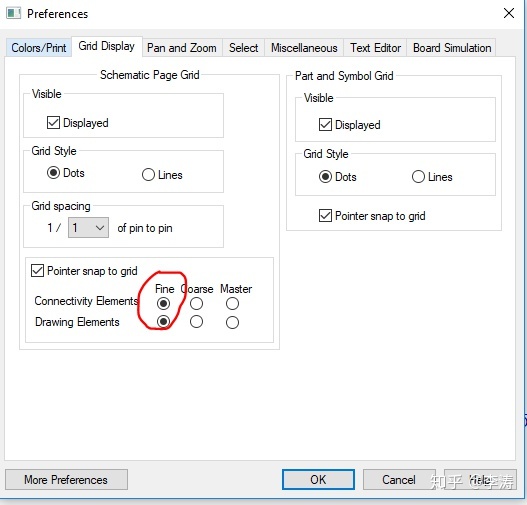

- schematic画图时如何disable grid方便连线

Options->Preferences可以配置连线的grid粗细,避免连线跳格太大

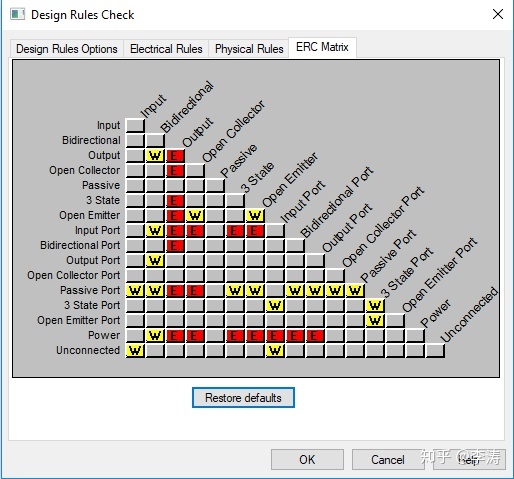

- schematic DRC check 的问题

ATE板子一般会将多种资源连接到一个net上,因此DRC的check会报很多error和warning。尝试修改ERC matrix但是没见到效果

但是可以将DRC的warning放到waiver中,DRC的error无法放入waiver。

- PCB layout 设计相关问题总

1) 封装设计相关资料

一般标贴器件的焊盘尺寸可以参见ipc的标准,有一个工具“pcb matrix ipc lpc viewer”可以下载参考如何定义标准标贴封装的焊盘大小;

做tester channel card,DPS card的封装的时候最好是在Pin1的中心画一个十字星,目的是在放入PCB的时候方便和footprint对齐坐标;

制作有via的焊盘时,需要考虑散热焊盘和antipad设计,在于争视频第25讲和以下文章可以看到具体内容

Allegro学习笔记之6 - 热风焊盘 - 百度文库wenku.baidu.com2) 层叠的设计

层叠的层数是由板子复杂度决定的。但是走线层的铺铜厚度(1 oz,0.5oz),介质层厚度及DK参数,阻抗控制需要线宽等需要事先和PCB厂商询问。

因此一般在约束管理器我们只约束线宽而不约束阻抗,原因就是因为在层叠中设置的一些影响阻抗的值比一定是打板的最终数据,allegro计算的阻抗不是实际板子值。所以我们只约束线宽,然后要求PCB厂商微调介质层厚度及DK参数保证阻抗。

3) 过孔的设计

在层叠设计之后要简单规划过孔的类型,然后在setup-> BB Via definition -> define BB via 中添加。

层叠的层数是由板子复杂度决定的。但是走线层的铺铜厚度(1 oz,0.5oz),介质层厚度及DK参数,阻抗控制需要线宽等需要事先和PCB厂商询问。

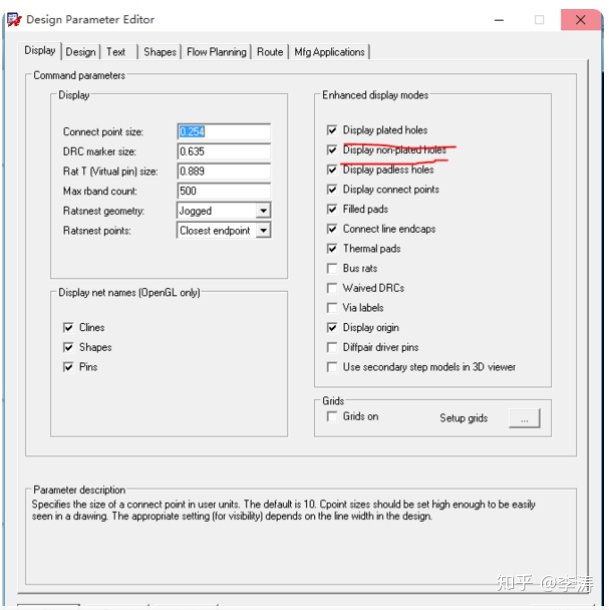

route时候如果增加VIA看不到drill hole,需要查看这些设置:

Display->color/visibility检查都有哪些设置

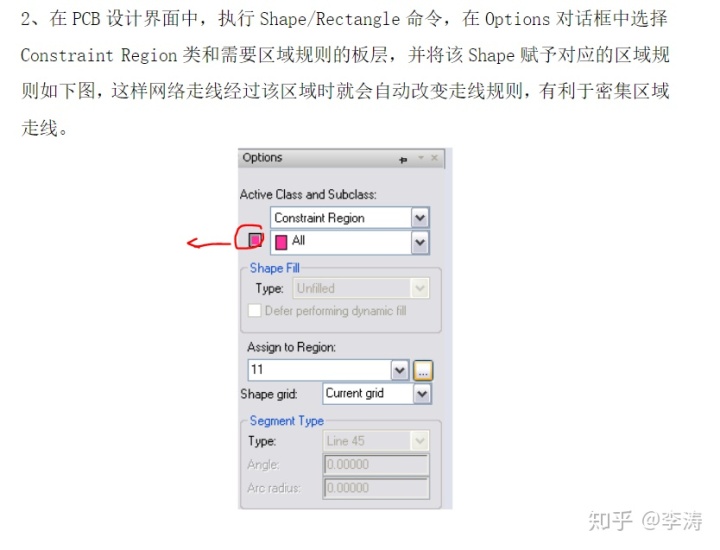

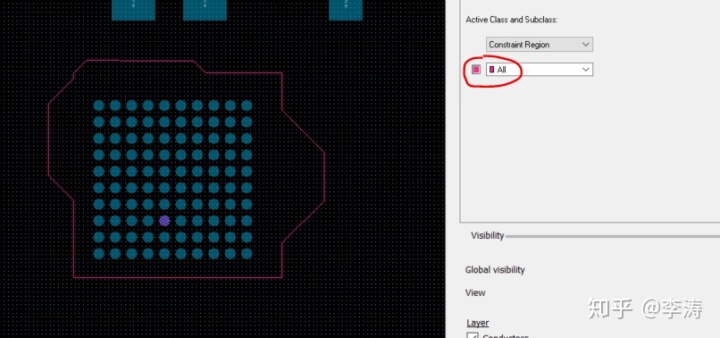

4) region的定义和约束施加

一般DUT的BGA array附近的走线需要不同的线宽,线距约束。因此需要定义这个特殊region,然后在约束管理器中对这个region定义参数。 Region可以用下面步骤定义,注意选择颜色保证绘制以后可见。

- PCB design的一些问题

做tester channel card,DPS card的封装的时候最好是在Pin1的中心画一个十字星,目的是在放入PCB的时候方便和footprint对齐坐标。

- 于博士讲allegro系列是比较好的初学教程,其教程如下:

第1讲:课程介绍,学习方法,了解cadence软件。

第2讲:创建原理图工程,创建元件库;

第3讲:分裂元件的制作方法(homogeneous和heterogeneous的区别;创建homogeneous类型元件;创建heterogeneous类型元件)

第4讲:正确使用heterogeneous类型的元件(可能出现的错误;出现错误的原因;正确的处理方法)

第5讲:加入元件库,放置元件(如何在原理图中加入元件库;如何删除元件库;如何在元件库中搜索元件;放置元件;放置电源和地))

第6讲:同一个页面内建立电气互连(放置wire,90度转角,任意转角;wire的连接方式;十字交叉wire加入连接点的方法,删除连接点方法;放置net alias方法;没有任何电气连接管脚处理方法;建立电气连接的注意事项。)

第7讲:总线的使用方法(放置总线;放置任意转角的总线;总线命名规则;把信号线连接到总线上;重复放置与总线连接的信号线;总线使用中的注意事项;在不同页面之间建立电器连接)

第8讲:browse命令的使用技巧(浏览所有parts使用技巧;浏览所有nets使用技巧;浏览所有offpage connector使用技巧;浏览所有DRC markers使用技巧)

第9讲:搜索操作使用技巧(搜索特定part;搜索特定net;搜索特定power;搜索特定flat nets)

第10讲:元件的替换与更新(replace cache用法;update cache的用法;replace cache与update cache区别)

第11讲:对原理图中对象的基本操作(对象的选择;对象的移动;对象的旋转;对象的镜像翻转;对象的拷贝、粘贴、删除)

第12讲:杂散操作(修改元件的value 及索引编号的方法;属性值位置调整;放置文本;文本的移动、旋转、拷贝、粘贴、删除;编辑文字的大小、字体、颜色)

第13讲:怎样添加footprint 属性(在原理图中修改单个元件封装信息;在元件库中修改封装信息,更新到原理图;批量修改元件封装信息 a。直接针对元件修改 b。在property editor中选择元件修改;查找元件封装信息是否遗漏的快速方法。

第14讲:生成网表(生成netlist前的准备工作;生成Netlist的方法;)

第15讲:生成元件清单及打印(生成元件清单;打印原理图;)

第16讲:高速电路设计流程,本教程使用的简化流程;

第17讲:Allegro常用软件模块介绍,各个软件模块之间的关系;

第18讲:allegroPCB editor软件操作界面介绍;

第19讲:allegro两个重要的概念:class和subclass分别是什么

第20讲:简单元件封装制作(allegro元件库封装制作的流程步骤;规则形状的SMD焊盘制作方法;表贴元件封装制作方法;0805贴片电容的封装制作实例。)

第21讲:BGA272封装制作,TI DSP6713;怎样设置引脚名称,怎样修改引脚布局;

第22讲:怎样创建自定义形状焊盘;

第23讲:SOIC类型封装制作;

第24讲:PQFP类型封装制作,学习引脚的旋转方法;

第25讲:包含通孔类引脚的零件制作,元件制作向导的使用(thermalpad和antipad的设计,负片需要VIA有这两个);

第26讲:包含非电气引脚的零件制作方法;

第27讲:创建电路板;

第28讲:设置叠层结构,创建内层电源和地平面;

第29讲:导入网表,栅格点的设置,Drawing Option的设置;

第30讲:手工摆放元件;

第31讲:使用原理图进行交互式摆放;

第32讲:按原理图页面进行摆放;

第33讲:使用Allegro pcb editor按room摆放;

第34讲:使用OrCAD Capture CIS按room摆放;

第35讲:快速布局,摆放过程中如何自动定位找到元件;

第36讲:pcb布局基本知识简单介绍;

第37讲:约束规则设置对话框简介,各部分关系;

第38讲:约束规则设置方法;

第39讲:线宽线距约束规则设置示例;

第40讲:区域约束规则设置示例;

第41讲:设置器件模型,加载模型库,赋予器件模型;constraint manager objects显示设置;创建总线;

第42讲:设置拓扑约束(方法1)

第43讲:设置拓扑约束(方法2)

第44讲:线长约束规则设置;

第45讲:相对延时约束规则设置;

第46讲:差分约束规则设置;

第47讲:布线准备(设置颜色;特殊方式显示电源地网络的飞线;网络的高亮设置;DRC标记显示方式;布线栅格点设置;飞线显示的开关;用不同的颜色同时高亮不同的网络;)

第48讲:BGA元件的自动扇出;

第49讲:手工布线、控制面板中内容解释。

第50讲:走线(拉线;加过孔,换层;控制线宽;推挤、抱紧;抓焊盘;替换走线;自动完成,控制出线方向。)

第51讲:群组布线;

第52讲:布线过程中实时信息显示(布线时显示延迟以及相对延迟信息;动态显示走线长度。)

第53讲:差分布线方法(伴随走线;单根走线模式;添加过孔;自动分离与靠拢。)

第54讲:高速网络布线(含T形连接点的网络走线方法;蛇形走线方法;修线。)

第55讲:铺铜操作:(内电层铺铜,外层铺铜,编辑shape的边界,为shape指定网络,手工void,删除孤岛,铺静态铜皮,铜皮的合并。)

第56讲:电源层分割;

第57讲:后期处理部分:(重新编号,back annotate,查看报告,数据库检查等相关操作。)

第58讲:丝印信息的处理;

第59讲:NC DRILL钻孔数据处理操作;

第60讲:gerber文件的输出:(方法和步骤);

3464

3464

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?