wire1–>wire2 可以,想象一根线,前后都可以连其他线。

wire w1,w2;

reg r1,r2;

assign w1=~w2;

wire–>reg 可以!reg只在特定触发条件下改变,所以wire怎么变无所谓。

wire w1,w2;

reg r1,r2;

initial begin

r1=w1;

$display("%b,%b,%b,%b",w1,w2,r1,r2);

end

reg->wire ,可以,只要reg变了,wire才变。

wire w1,w2;

reg r1,r2;

assign w1=~r1;

initial begin

r1=w1;

$display("%b,%b,%b,%b",w1,w2,r1,r2);

end

reg1->reg2,可以,reg的采样取决于触发,相当于特定时刻我采样,没啥问题。

wire w1,w2;

reg r1,r2;

initial begin

r1=r2;

$display("%b,%b,%b,%b",w1,w2,r1,r2);

end

从上述四个方向分析,方向其实是无所谓的,有所谓的是赋值方式,比如assign的左边,必须是net,因为assign就表示了这是一个连续functor,右边改变,左边要传递的,你reg是时序触发的,传不动。

再比如,w不能放在initial和always中的左值,因为它是个线网,需要时刻不能说按照你时序的方式来赋值。

综上所述,方向不限,但reg的赋值必须是时序方式,wire的赋值方式必须是net方式连续赋值,functor模式,合情合理。

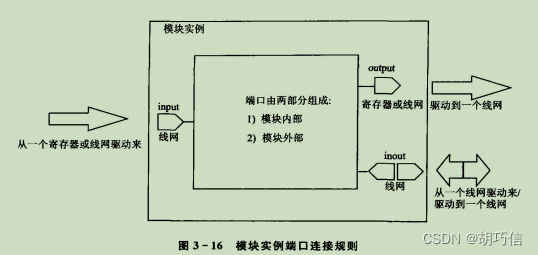

关于模块参数的线网或reg类型的限制原理:

由前面分析可知,方向无所谓,但reg当左值时,必须是时序方式,进而推理:

module输出,ouput是右值,外面是左值,所以output可以是reg或wire,外面必须是wire。

module输入,外面是左值,input是右值,所以input必须是wire,外面可以是reg或wire。

module inout,inout和外面都是wire。

7235

7235

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?