双口RAM的读写冲突问题在FPGA调试中经常遇到,并且,往往是那种费了好大劲追信号追到吐血后才确认到的问题。在初学FPGA调试中,常常为了所谓的省事,在写代码设计仿真阶段就忽略了双口RAM的读写冲突问题,导致在FPGA上板调试中浪费大量的时间。本文就针对以往出现的双口RAM读写冲突问题展开讨论,希望能够给大家提个醒,内容虽然简单,但的确是不容忽视的一个隐藏很深的大问题。

FPGA调试本身就是挺辛苦的一件事情,尤其是在刚开始调试FPGA的时候,无论培训的时候如何强调一些注意事项,如跨时钟域问题,如接口问题,以及RAM读写冲突问题,但一旦做起项目来,每每还是有同学必须要亲自往这些坑里面跳一次才真正懂得这些BUG的含义。

这么多年了,每届学生都是如此。

双口RAM读写冲突的问题,往往在性能的边界极限测试的时候才暴露出来。往往分为不宜重现和可重现两种。虽然可重现,但一步步根据错误现象进行信号追踪到出问题的双口RAM时,已经过去了一周或数周的时间。不宜重现的问题则更加麻烦,有时候几个小时还不出一次问题。避免这种问题的的根本解决办法就是防范于未然,在代码的仿真阶段就对各个双口RAM进行读写冲突的防护措施。

双口RAM对同一个地址同时读写、对同一个地址写的冲突,每年都要跟这个问题斗争一两次,每次少则几天,多则几周时间。

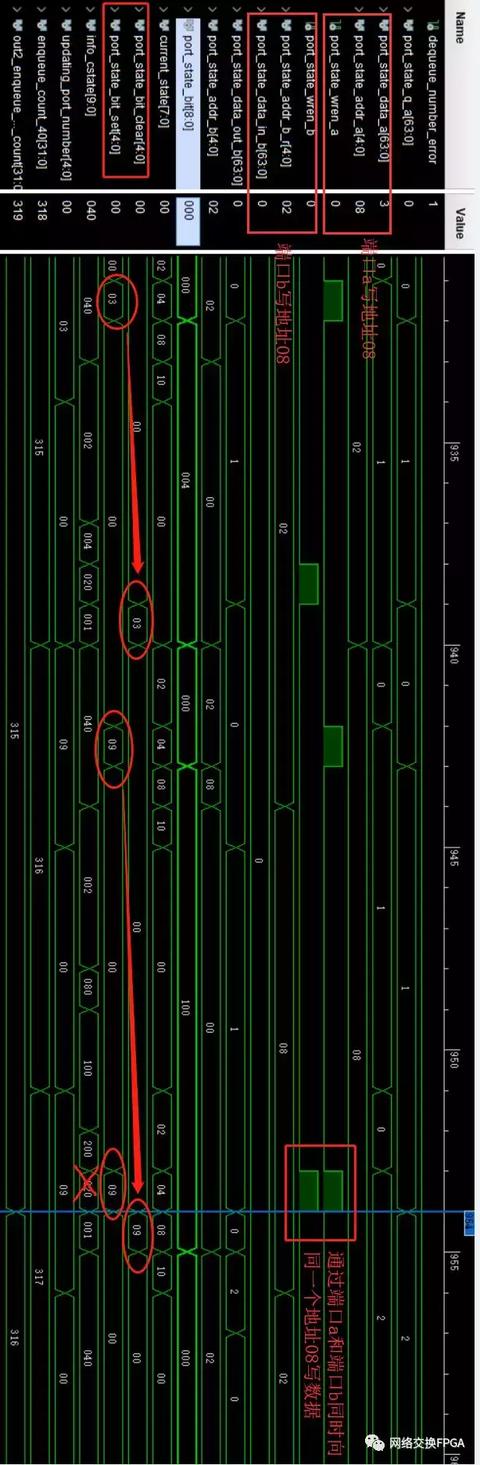

下面是一个经过了数天定位到的一个问题,双口RAM两侧同时向同一个地址写入数据导致出错的Vivado调试波形截图。(ZL)

案例1(TK)

1、问题现象:

以队列信息中的队列中分组个数的值为例,由于更新错误导致当队列中实际为空(即分组个数为0),而队列信息显示队列分组个数不为0,导致输出错误数据帧。

双口RAM的读写冲突问题在FPGA调试中经常遇到,并且,往往是那种费了好大劲追信号追到吐血后才确认到的问题。在初学FPGA调试中,常常为了所谓的省事,在写代码设计仿真阶段就忽略了双口RAM的读写冲突问题,导致在FPGA上板调试中浪费大量的时间。本文就针对以往出现的双口RAM读写冲突问题展开讨论,希望能够给大家提个醒,内容虽然简单,但的确是不容忽视的一个隐藏很深的大问题。FPGA调试本身就是挺辛苦的...

双口RAM的读写冲突问题在FPGA调试中经常遇到,并且,往往是那种费了好大劲追信号追到吐血后才确认到的问题。在初学FPGA调试中,常常为了所谓的省事,在写代码设计仿真阶段就忽略了双口RAM的读写冲突问题,导致在FPGA上板调试中浪费大量的时间。本文就针对以往出现的双口RAM读写冲突问题展开讨论,希望能够给大家提个醒,内容虽然简单,但的确是不容忽视的一个隐藏很深的大问题。FPGA调试本身就是挺辛苦的...

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3235

3235

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?