简介

在PCIe总线中,MSI和MSI-X中断机制使用存储器写请求TLP向处理器提交中断请求,所以将MSI/MSI-X中断信息的存储器写报文简称为MSI/MSI-X报文。

x86使用FSB Interrupt Message方式处理MSI/MSI-X中断请求。

PCIe设备在提交MSI中断请求时,都是向MSI/MSI-X Capability结构中的Meaasge Address的地址写Message Data数据,从而组成一个存储器写TLP,向处理器提交存储器写请求。

翻译一下就是说:

由于存储器域和PCIe域地址的相互映射,向MessageAddress地址写数据,也就是向对应的存储器域地址写数据,写入的数据为Message Data,从而组成一个存储器写TLP,向存储器提交存储器写请求。

虚拟中断线方式

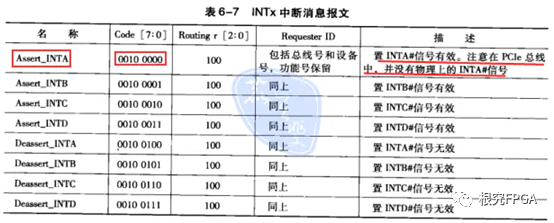

在PCIe桥下挂载PCI设备时,如果该PCI设备不支持MSI终端机制,在PCI设备发出INTx中断请求时,PCIe桥将该INTx中断信号转换为INTx中断消息报文,并向Root Complex提交中断请求。在PCIe总线中,一共规定了8种INTx中断消息报文:

当PCIe设备不使用MSI报文向RC提交中断请求时,可以首先使用ASSERT_INTx向RC提交中断请求,当RC处理完毕后发出一个Deassert_INTx中断请求,设备接收到Deassert_INTx报文后,将结束接收到的INTx中断请求。

PCIe设备接收到一个INTx中断请求后,需要首先结束该INTx中断消息,之后根据中断路由表产生一个新的INTx中断消息,直到这个中断消息传递到RC。

Legacy Interrupt

Legacy Interrupt,翻译过来是传统中断,百思不得其解,直到看到这样一段解释:

Legacy interruptare two interrupts that were in ARM before GIC arrived:

nIRQ-normalinterrupt request

fIRQ-fastinterrupt

Legacyinterrupts were made for single-core processors,and they don’t support multi-coreprocessors internally.

The legacy arehardwired into one of the cores

LegacyInterrupts:传统中断,非MSI中断,PCI设备使用INTx中断请求的方式与电平触发类似,而MSI/MSI-X中断请求的方式与边沿触发方式类似。

当PCI设备的INTx信号有效时,PCIe桥将该信号转换为Assert_INTX消息报文,当这些INTx信号无效时,PCIe桥将该信号转换为Deassert_INTx中断信号。

MSI与MSI-X的区别

MSI中断机制最多支持32个中断请求,而且要求中断向量连续;

MSI

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

414

414

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?