SDC语法学习

前言

参考

《综合与时序分析的设计约束》进行学习,主要针对一些经典语法的使用,适合与新手入门,如有错误请及时指正,本人白天上班晚上更新,可能更新的比较慢,也针对工作中遇到的问题进行重点学习

一、通过Tcl扩展SDC

1.Tcl基础知识

1.1 Tcl具有多种语言结构:

- 变量

- 列表

- 表达式与运算符

- 控制流语句

- 过程

1.2 Tcl变量:

Tcl变量是ASCII字符串,变量使用set命令来分配

set abc "1234" ;#set是命令,abc是变量,1234是分配给变量的值`

如果对变量求值,则需使用$符号

puts $abc ;#将会打印1234

如果索引与变量名一起使用,则可将变成视为数组,索引可以为字符串

set def(1) 4567 ;#这里def是数组变量,索引被设为1

set def(test) 5678 ;#这里索引是test

puts $def(1)

puts $def(test)

打印特殊符号

puts "I have a \$bill"

puts {I have a $bill}

如果尝试利用另一个命令设置变量

set x [set y 100] ;#将x的值设置为100

set x {[set y 100]} ;#将x的值设置为[set y 100]

1.3 Tcl列表:

Tcl中的列表是对象的集合

#以下创建列表

set gates [list AND OR NOT NAND NOR]

set gates [{AND} {OR} {NOT} {NAND} {NOR}]

set gates [split "AND.OR.NOT.NAND.NOR" "."]

#要将另一个项目添加到列表中,使用lappend

set gates [lappend gates XOR]

#要在列表中搜索,使用lsearch

#返回2,他是列表中的索引

puts [lesarch $gates NOT];

#返回-1,疑问没找到

puts [lesarch $gates XNOT];

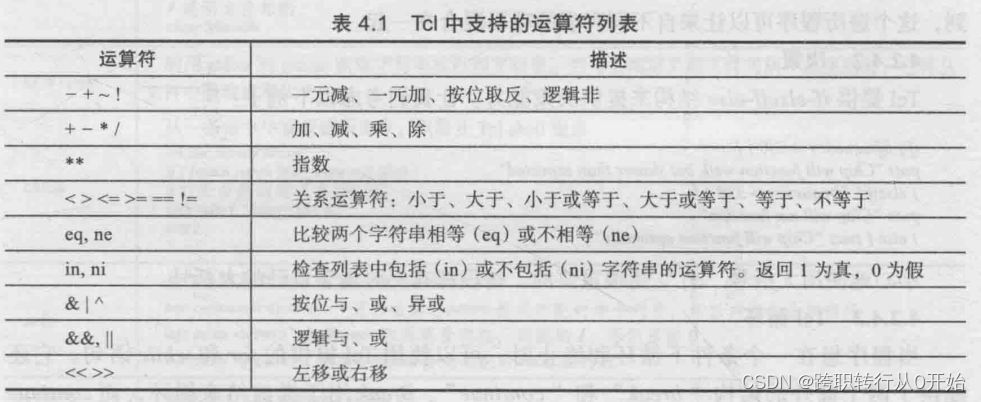

1.4 Tcl表达式与运算符:

Tcl中使用expr命令来对表达式求值

set x 10;

#两条返回语句均为30

expr $x + 20

expr {$x + 20}

1.5 Tcl的控制流语句:

Tcl控制流语句由以下种类的结构组成:

- 列表遍历

- 决策

- 循环

- 子程序

1.5.1 列表遍历

为了遍历列表,Tcl提供了foreach结构

set gates [list AND OR NOT NAND NOR XOR]

set index 1

foreach element $gates{

puts "Gate $index in the list is $element"

incr index ;#index 自动加1

}

#产生输出如下:

Gate 1 in the list is AND

Gate 2 in the list is OR

Gate 3 in the list is NOT

Gate 4 in the list is NAND

Gate 5 in the list is NOR

Gate 6 in the list is XOR

Tcl的foreach为用户提供了同时遍历多个列表的独特功能

set allgates{}

foreach gatelist1{AND OR XOR} gatelist2{AND OR XOR}{

lappend allgates $gatelist2 $gatelist1

}

put $allgates

#将在变量allgates中存储以下值“NAND AND NOR OR XNOR XOR”

1.5.2 决策

Tcl提供if-elseif-else结构来提供决策能力:

if{$frequency<300}{

puts "Chip will function well,but slower than expected"

}elseif{$frequency>300}{

puts "Chip will not function"

}else{puts "Chip will function optimally"}

1.5.3 Tcl循环

for<初值><条件><下一步>{

<语句体>

}

while<条件>{

<语句体>

}

1.5.4 Tcl过程

Tcl过程使用proc来编写,使用return语句从过程中返回值:

proc sum{addend1 addend2}{

ser value[expr {$addend1 + $addend2}]

return $value

}

#调用过程

set x[sum 5 10]

puts $x ;#打印15

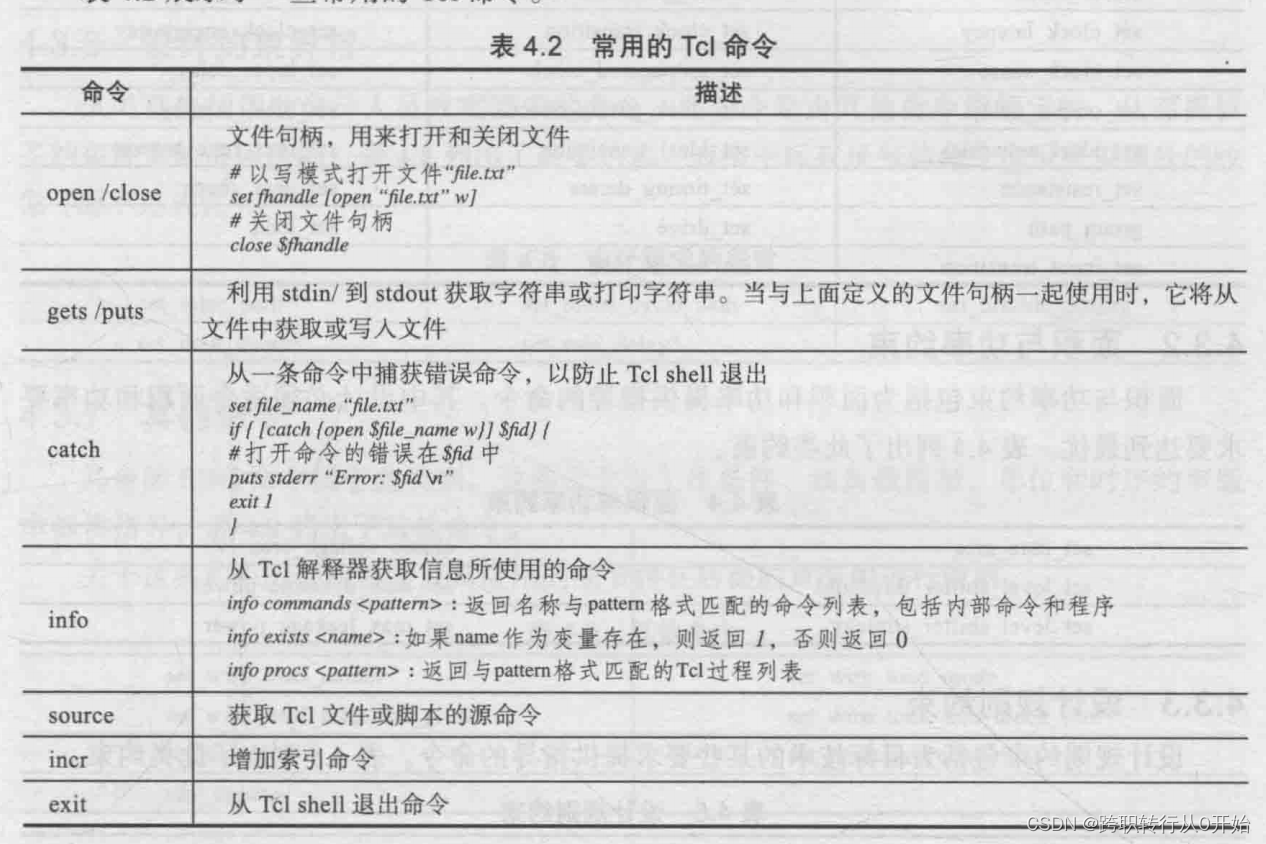

1.5.5 其他命令

总结:

本章主要介绍了Tcl一些基础知识,用于构建工程的框架,在大规模芯片设计中,通常是以模块为单位进行时序约束, 但最终全芯片综合时需要剔除一些约束,或者变更pins和ports的路径,这时就需要通过传递参数实现, 后面将进行约束语法进行说明

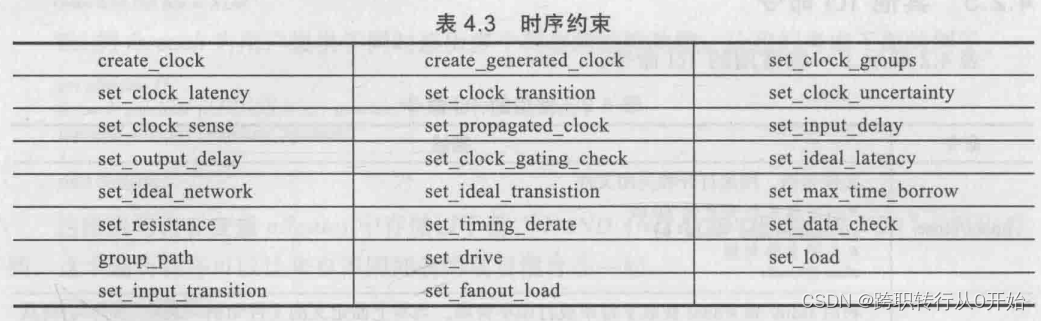

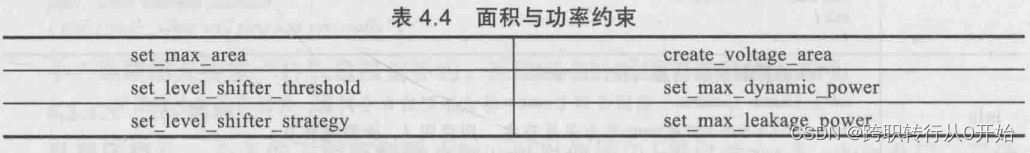

2. SDC综合

SDC格式的约束可以大致分为以下几种

- 时序约束

- 面积与功率约束

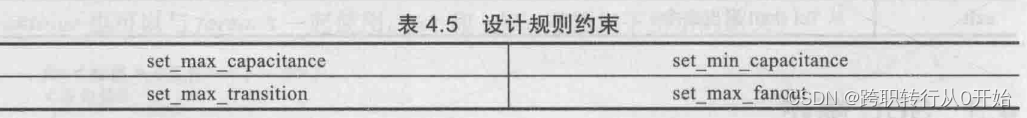

- 设计规则约束

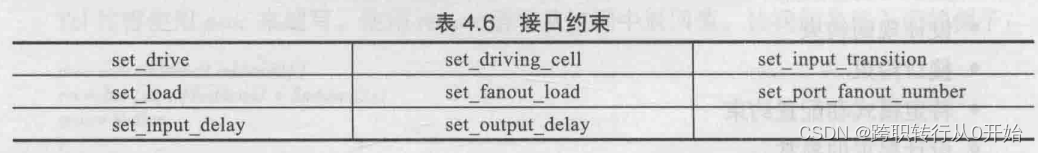

- 接口约束

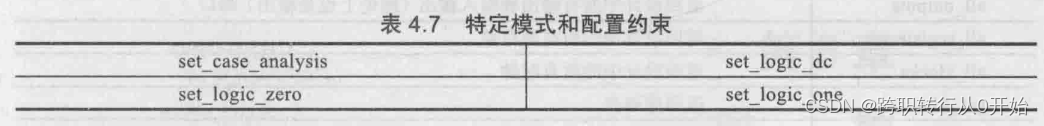

- 特定模式和配置约束

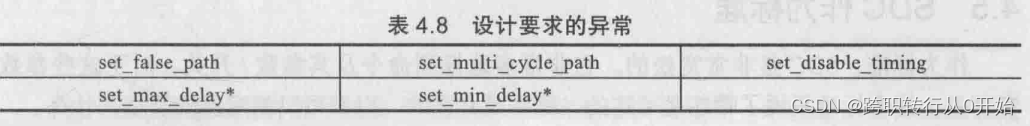

- 设计要求的异常

- 其他命令

2.1 时序约束:

2.2 面积与功率约束:

2.3 设计规则约束:

2.4 接口约束:

2.5 特定模式和配置约束:

2.6 设计要求的异常:

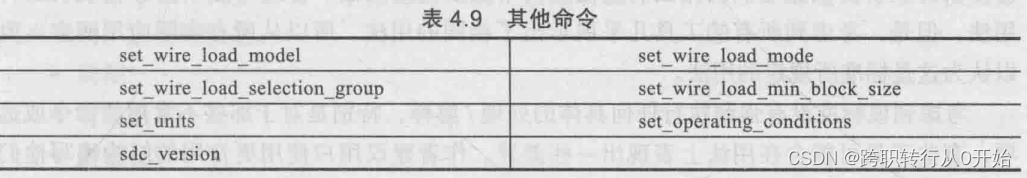

2.7 其他命令:

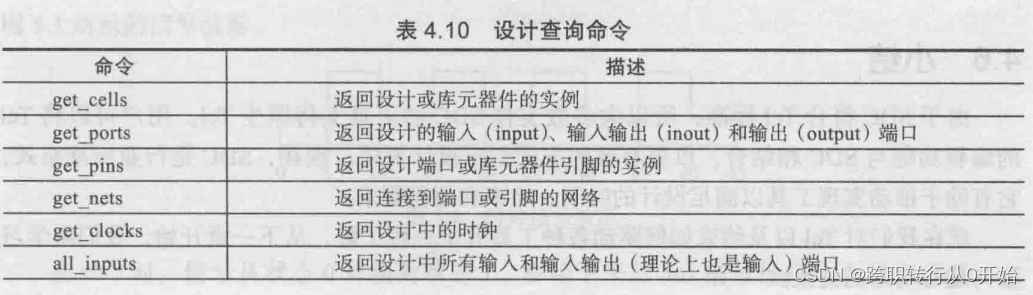

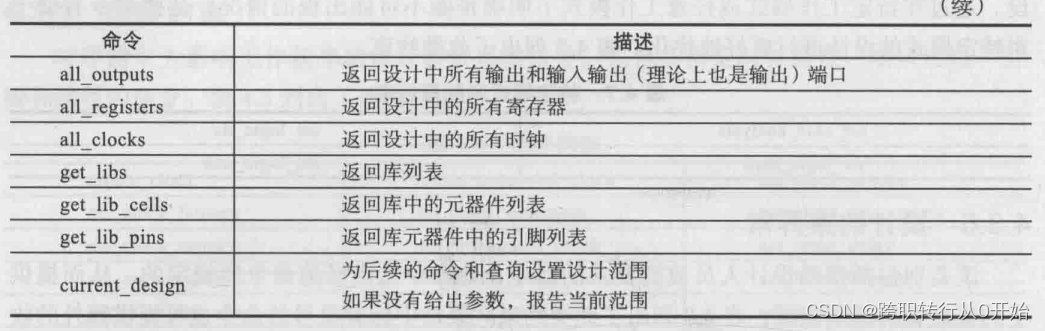

2.8 查询:

查询指令是在静态时序分析过程中查询的重要指令,学会在pt里寻找相应的pin脚和起始路径,有助提升问题分析速度和精确度。

本人在曾在项目遇到sdf返标时序时出现问题,经大佬指点,利用pt工具很快就完成了错误定位。

总结

本章主要介绍了SDC所有约束,因为本人做过得项目只需要进行时序约束,后面将会主要针对时序约束进行学习,如果有其他时间也会对其他约束进行学习。

3. 常用SDC时序约束

本章将会开始学习时序约束语法,基础的知识这里不做为学习内容,只针对如何编写时序约束和其效果进行学习

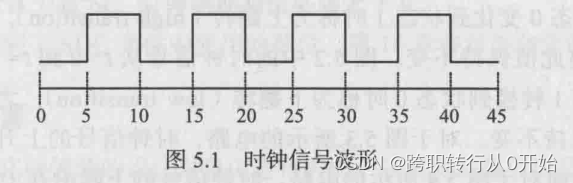

3.1 creat_clock:

含义:在设计中具体说明时钟信号

creat_clock -period period_value

[source_objects]

[-name clock_name]

[-waveform edge_list]

[-add]

[-comment comment_srting]

-period :定义时钟周期,默认时间ns,时钟周期必须大于0;

-name:给时钟信号命名;

-waveform :占空比;

-add:在时钟源指定多个时钟;

-comment:添加注释,不影响综合和时序。

示例:

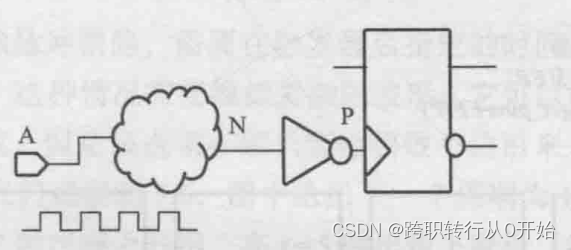

(1)标识时钟源

creat_clock -period 10 [get_ports A]

creat_clock -period 10 [get_nets N]

creat_clock -period 10 [get_pins FF/P]

(2)指定占空比

creat_clock -period 10 -name CKL -waveform {5 10} [get_ports A] ;#如果不指定,默认50%

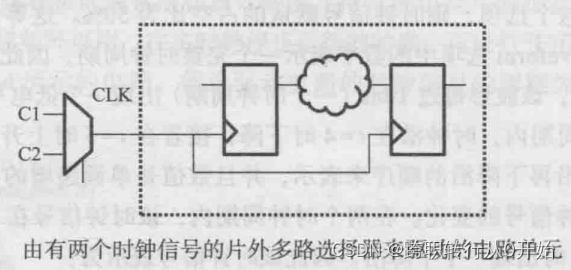

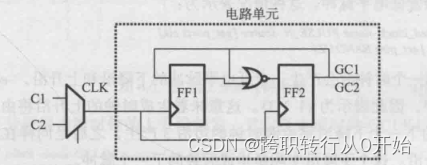

(3)同源多时钟

creat_clock -name C1 -period 10 [get_ports CLK]

creat_clock -name C2 -period 10 [get_ports CLK] -add

通常设计都会按照最快的时钟频率去约,约束最严格

3.2 creat_generated_clock:

含义:设定生成时钟

creat_generated_clock [source_objects]

-source clock_source_pin

[-master_clock master_clock_name]

[-name generated_clock_name]

[-edges edge_list]

[-divide_by factor]

[-multiply_by factor]

[-invert]

[-edge_shift shift_list]

[-duty_cycle percent]

[-combinational]

[-add]

[-comment comment_string]

-source :设定生成时钟的源;

-master_clock :

-name:时钟命名;

-edges:对应源时钟边沿的整数列表;

-divide_by:生成时钟通过某个因子分频

-multiply_by:生成时钟通过某个因子倍频

-invert:反向

-edge_shift:在时间单元内每一个时钟沿的位移

-duty_cycle:占空比

-combinational:是能组合电路路径

-add:在某一点可定义多个时钟

案例:

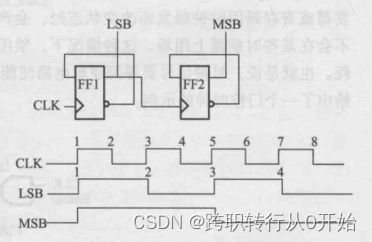

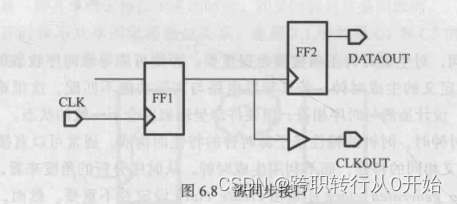

(1)生成倍频和分频时钟

create_clock -priod 10 -name CLK [get_ports CLK]

creat_generated_clock -name LSB -source [get_ports CLK]

-divide_by 2 [gen_pins FF1/Q]

creat_generated_clock -name MSB-source [get_pins FF1/Q]

-divide_by 2 [gen_pins FF2/Q]

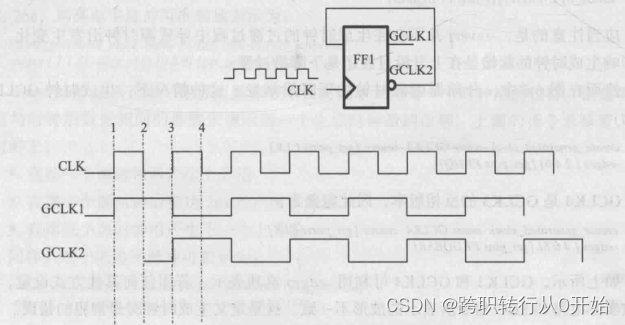

(2)反向时钟

create_clock -priod 10 -name CLK [get_ports CLK]

creat_generated_clock -name GCLK -source [get_ports CLK]

-divide_by 2 [gen_pins FF1/Q]

creat_generated_clock -name GCLK2 -source [get_ports CLK]

-divide_by 2 [gen_pins FF1/QBAR]

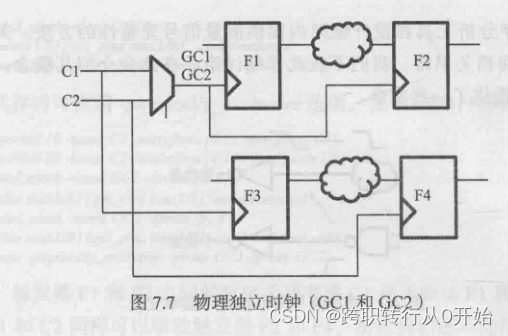

(3)多个时钟源:

create_clock -priod 10 -name C1 [get_ports CLK]

create_clock -priod 10 -name C2 [get_ports CLK] -add

#基于C1特性的生成时钟

creat_generated_clock -name CG1 -divide_by 3-source [get_port CLK]

-master_clock C1 [gen_pins FF2/Q]

#基于C2特性的生成时钟

creat_generated_clock -name CG2 -divide_by 3-source [get_port CLK]

-master_clock C2 [gen_pins FF2/Q] -add

(4)使能组合电路路径:

creat_generated_clock -name CLKOUT -combinational -source [get_pins FF1/Q[get_ports CLKOUT]

3.3 set_clock_group:

含义:忽略任何异步或者互斥时钟之间的时序路径或串扰分析

set_clock_groups [-name group_name]

[-group clock_list]

[-logically_exclusive]

[-physically_exclusive]

[-asynchronous]

[-allow_paths]

[-comment comment_string]

-name:提供时钟组唯一的名称

-group:将这些时钟分入各组

-logically_exclusive:对互斥耦合关系时钟使用

-physically_exclusive:时钟并不共存

-asynchronous:时钟彼此不能共享相位关系

allow_paths:希望执行串扰分析而不禁用时钟之间的时序电路路径

(1)设置时钟组

create_clock -priod 10 -name C1 -wavefrom {0 5}[get_ports C1]

create_clock -priod 20 -name C2 -wavefrom {0 12}[get_ports C2]

creat_generated_clock -name GC1 -source [get_ports C1] [get_pins mux1/A] -combinational

creat_generated_clock -name GC2 -source [get_ports C2] [get_pins mux1/B] -combinational

set_clock_groups -logically_exclusive -group GC1 -group GC2

(2)异步时钟

set_clock_groups -asynchronous -group [get_clocks {clk1 clk2 clk3}] -group [get_clocks {clk4 clk5 clk6}]

1.clk1 异步于clk4、clk5、clk6

2.clk2 异步于clk4、clk5、clk6

3.clk3 异步于clk4、clk5、clk6

4.clk1、clk2、clk3之间没有假设关系

5.clk4、clk5、clk6之间没有假设关系

小结:本人在项目中只用过group指令,详细介绍请看书

3.4 其他时钟特性

3.4.1 set_clock_transition

含义:时钟的过渡

set_clock_transition [-rise]

[-fall]

[-max]

[-min]

clock_list

transition_time

-rise:提供时钟上升沿的过渡时间;

-fall:提供下降沿的过渡时间;

-max/-min:设定过渡时间的最大和最小操作条件

set_clock_transition -fall -rise 0.2 [get_clocks C1]

set_clock_transition -fall -min 0.2 [get_clocks C2]

set_clock_transition -fall -max 0.4 [get_clocks C2]

set_clock_transition 0.3 [all_clocks]

3.4.2 set_clock_uncertainty

含义:将时钟偏斜和抖动模型化

set_clock_uncertainty [-form | -rise_from | -fall_from from_clock]

[-to | -rise_to | -fall_to to_clock]

[-setup]

[-hold]

[-rise]

[-fall]

[object_list]

Uncertaunty_value

3.4.3 set_clock_latency

含义:时钟延迟

set_clock_latency [-rise]

[-fall]

[-min]

[-max]

[-source]

[-late]

[-early]

[-clock clock_list]

delay

object_list

3.4.4 set_clock_sense

含义:制定路径传递的敏感性

set_clock_sense [-positive | -negative | -stop_propagation]

[-pulse pulse]

[-min]

[-clock clock_list]

pin_list

3.4.5 set_ideal_network

含义:定义理想器件

set_ideal_network [-no_propagate]

object_list

小结:

本章仅仅介绍了一写语法,因为项目中暂时没遇到过,需要的同学请自行查阅资料,后续如果在项目中遇到将进行补充

4 端口延迟

4.1 set_input_delay

含义:输入端口延迟

set_input_delay [-clock clock_name]

[-clock_fall]

[-level_sensitive]

[-rise]

[-fall]

[-max]

[-min]

[-add_delay]

[-network_latency_included]

[-source_latency_included]

delay_value

port_pin_list

-clock:指定参考时钟

-clock_fall:默认上升沿,如果使用下降沿用此指令

-level_sensitive:如果器件是个锁存器,不是寄存器用此函数

-rise:限定输入延迟与输入端口信号的上升沿对应

-fall:限定输入延迟与输入端口信号的下降沿对应

-max:用于限定指定的延迟值与输入端口信号的最迟到达时间对应

-min:用于限定指定的延迟值与输入端口信号的最早到达时间对应

-add_delay:表示额外的约束,不会覆盖前一个约束

-network_latency_included:网络延迟开关

-source_latency_included:时钟源延迟开关

delay_value:延迟值

port_pin_list:延迟端口

4.2 set_output_delay

含义:输出端口延迟

set_output_delay [-clock clock_name]

[-clock_fall]

[-level_sensitive]

[-rise]

[-fall]

[-max]

[-min]

[-add_delay]

[-network_latency_included]

[-source_latency_included]

delay_value

port_pin_list

-clock:指定参考时钟

-clock_fall:默认上升沿,如果使用下降沿用此指令

-level_sensitive:如果器件是个锁存器,不是寄存器用此函数

-rise:限定输出延迟与输出端口信号的上升沿对应

-fall:限定输出延迟与输出端口信号的下降沿对应

-max:用于限定指定的延迟值与输出端口信号的最迟到达时间对应

-min:用于限定指定的延迟值与输出端口信号的最早到达时间对应

-add_delay:表示额外的约束,不会覆盖前一个约束

-network_latency_included:网络延迟开关

-source_latency_included:时钟源延迟开关

delay_value:延迟值

port_pin_list:延迟端口

本节语法较少,但涉及扩展内容较多,建议直接看书第九章。

5 完整的端口约束

本章简单介绍一些驱动和负载语法,作者暂时没有在工作中遇到过

set_drive;#指定驱动器等效电阻

set_driving_cell;#指定驱动单元

set_input_transition;#直接指定过渡时间

set_fanout_load;#扇出负载

set_load;#负载

set_port_fanout_number;#扇出数

3187

3187

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?