目录

前言

从本节开始,进入到FPGA端的介绍,即固件与FPGA通过GPIF II接口的交互。学习本节内容之前,应对Cyusb3014芯片原理的部分比较熟悉,包括固件中的各术语概念,以及数据流中各部分的映射即配置。

1.简介

关于这个部分,目的是使固件与FPGA的数据传输能够正确进行,同时包括上行数据和下行数据。为达到这一目的,准备介绍的内容如下:①明确固件的配置。举个简单例子,GPIF II Designer中可以设置引脚的名称,也可以设置不同状态以及状态切换的条件,因此不同的固件配置应该适配不同的逻辑代码,明确固件配置就是表明我的全部的FPGA相关理论是基于这个特定配置的。②时序分析,包括了读写时序分析,以及芯片原理部分提及的短包,零包,并介绍短包、零包的应用以及本质。③分析一些现象,例如缓冲区的切换;pclk时钟反相180°的原因;官方AN65974xilinx代码的错误等。④介绍标志的使用,固件原理提到了有三种标志,具体使用时应该怎么操作,有哪些注意事项?⑤逻辑开发中,一些编程经验的分享。以上内容均会穿插在文章中体现,阅读时注意对号入座。

2.固件配置

实际开发过程中,使用xlinx的K7系列的一颗FPGA芯片,GPIF II Designer中IO映射由具体的硬件PCB确定,现说明固件的配置。使用名为BulkDownUp.img的固件配合FPGA开发。在GPIF工程中,修改IO映射为实际板卡的连接(不写出);GPIF II接口类型配置为sync_slavefifo同步从模式;数据总线位宽为32bit;使用外部晶振,上升沿有效;默认小端模式不做修改(建议改成大端模式,我没修改是因为开发过程没注意这个细节);地址总线位宽为2bit,也就是可以使用四个线程传输数据;关于外部引脚的命名,状态机的状态,状态切换的条件,状态执行的动作均不做修改;修改标志的配置,配置四个标志,FLAGA对应线程0专用标志、FLAGB对应线程0局部标志;FLAGC对应线程3专用标志、FLAGD对应线程3局部标志;FLAGA-D初始化配置均为0,设置为低电平有效。

在固件工程中,设置两个端点,分别是用于上行数据传输0x81、用于下行数据传输的端点0x01;使用时钟频率为100MHz,即PCLK的时钟大小为100MHz,此时在固件中应通过CyU3PsysClockConfig_t 结构的 setSysClk400 参数指定 FX3 器件的主时钟被设置为高于 400 MHz 的频率。即clkCfg.setSysClk400 = CyTrue。否则会发生固件的溢出错误,在control center中表现为error 997;设置两个局部标志的水印值为6;设置上行DMA自动通道的缓冲区个数为4个,每个大小为16KB,下行DMA自动通道的缓冲区个数为8个,每个大小为16KB。

3.固件配置说明

3.1程序框图

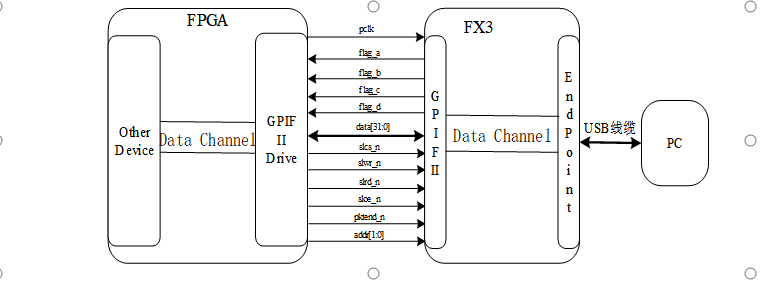

关于程序框图,前面介绍的很多了,如下图所示,“放大”了FPGA与FX3连接的细节,指向FX3的信号代表了FPGA的控制信号,通过这些信号进行数据的读写控制,数据由双向数据总线db[31:0]完成传输;指向FPGA的信号即flag信号是在数据传输过程中FX3发出的用于指示内部数据通道情况的,即用于完成流控制,避免空读或者满写的情况发生。所谓流控制,当FX3内部缓冲区没有数据的时候,通过flag向外发出这个状态,从而期望外部控制器不在请求读数据,避免空读发生未知错误。同样,在FPGA想FX3写数据的时候,当FX3内部缓冲区满后,通过flag告诉FPGA已满,从而期望FPGA停止写操作,避免数据溢出造成丢失。

3.2DMA通道

数据的传输方向是由自动DMA通道所连接的生产者套接字和消费者套接字决定的。当PIB作为生产者,UIB作为消费者套接字是,此DMA通道的数据传输方向是由GPIF到USB端点,即对于FPGA来说,是一个上行传输通道。关于缓冲区大小和个数为以上组合的考虑有二,其一,为了最大可能的提升数据传输带宽,什么样的配置组合能最大化吞吐量在芯片原理的有关章节已描述清楚;其二,FX3固件内部的缓冲区的资源大小是有限的,因此考虑到我的应用中要保障下行数据的带宽,因此下行通道的数量更多。顺便一提,使用100MHz就是将PCLK设置成100MHz,这样做的目的也是为了获得最大带宽。理论阶段说明了USB3.0的传输速度在5Gbps,实际速度实测中在370MB/s(加入了GPIF II),PCLK最大可设置为100MHz,也就是说数据通过FX3芯片,速率瓶颈在GPIF II,因为100MHz的时钟,32bit带框,理论传输速率为400MB/s。

3.3关于FLAG

全部FLAG的初始值为0,并且信号是低电平有效,这是为了FPGA代码开发中方便。如果FPGA写数据的代码写成“缓冲区非满就一直写”,那么上电之后由于FLAG初始化值为1,那么可能会导致未知风险,因此将初始值设置为0,固件初始化完成,缓冲区准备就绪之后,flag才会正确的指示缓冲区的状态。还有一个问题是,为啥要使用一个专用标志和一个局部标志的组合标识一个线程的(或者说一个缓冲区)的状态?举上行数据通道说明,本例中,FLAGA用于上行数据通道,指示“是否可以写”,当FLAGA为1的时候可以往里写(通常还要等待局部标志为1之后,代表局部标志做好准备),但是什么时候停呢?FLAGA并不能实时指示缓冲区的“满”的状态(缓冲区满了后不能该信号实时显示满状态,延后3个周期才可以),因此该信号不能作为“停止写”的依据,这就用了局部标志,它会在将要满的时候告诉你,还差几个周期满,这样可以准确的停止写,实现精准流控制。就像AN65974文档中提到的“局部标志仅用于决定传输结束的时间。必须在开始传输时监控满/空标志,以确保套接字的可用性。这意味着,不能单独使用局部标志,而必须和满/空标志结合使用。”

另外需要说明的是FLAGA、FLAGB使用于从设备FIFO写入操作,而FLAGC、FLAGD使用于从设备FIFO读取操作。flaga_d、flagb_d、flagc_d、flagd_d均为实际的FLAGA,FLAGB,FLAGC,FLAGD信号采样后的信号。(为了时序分析时区分)

4.引脚功能说明

| 信号名称 | 信号说明 |

| SLCS# | 这是从设备 FIFO 接口的芯片选择信号。必须激活它,才可以访问从设备 FIFO。 |

| SLWR# | 这是从设备 FIFO 接口的写入选通信号。必须激活它,才可对从设备 FIFO 执行写入操作。 |

| SLRD# | 这是从设备 FIFO 接口的读取选通信号。必须激活它,才可对从设备 FIFO 执行读取操作。 |

| SLOE# | 这是输出使能信号。该信号激活后, FX3 就可驱动从设备 FIFO 接口的数据总线。必须激活它,才可以对从设备FIFO 执行读取操作。 |

| FLAGA-D | 这些信号均是 FX3 的标志输出。它们表示 FX3 套接字是否可用。 FLAGA、 FLAGB 使用于从设备 FIFO 写入操作,而 FLAGC、 FLAGD 使用于从设备 FIFO 读取操作。 |

| A[1:0] | 这是从设备 FIFO 的 2 位地址总线。 |

| DQ[31:0] | 这是从设备 FIFO 的 16 位或 32 位数据总线。 |

| PKTEND# | 激活该信号后,可将短数据包或零长度数据包写入从设备 FIFO 内。 |

| PCLK | 这是从设备 FIFO 接口的时钟。 |

5.传送门

● 我的主页

END

🔈文章原创,首发于CSDN论坛。

🔈欢迎点赞❤❤收藏⭐⭐打赏💴💴!

🔈欢迎评论区或私信指出错误❌,提出宝贵意见或疑问❓。

9

9

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?