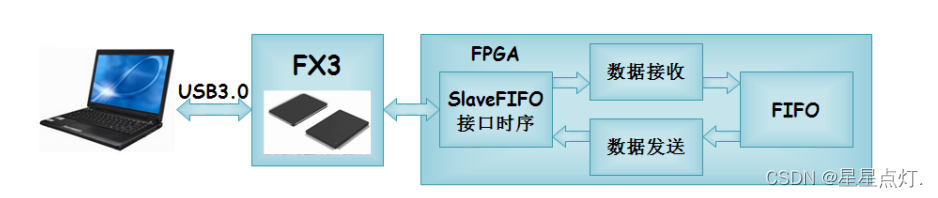

一、功能概述

PC 端发送数据到 FX3,FX3 通过指示信号 flaga 告知 FPGA 有数据待读取,FPGA 端便通过 SlaveFIFO 接口读取 PC 端发送过来的数据缓存到 FPGA 内部的 FIFO 中,FPGA 在完成读取操作后,发起一次 SlaveFIFO 的写入操作,将接收到的数 据通过 FX3 最终返回到 PC 端。

二、FPGA代码解析

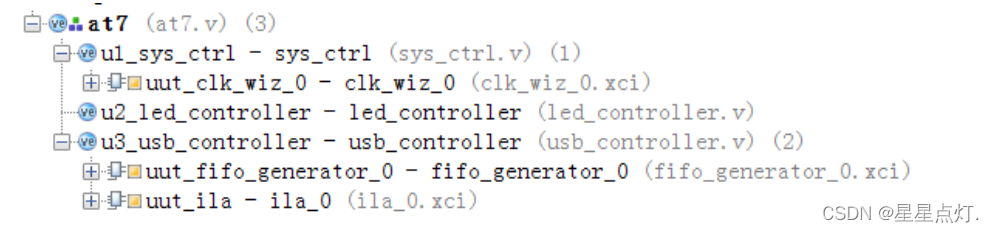

2.1工程层次及模块基本功能介绍

【模块1:sys_ctrl.v 】与系统时钟和复位信号产生相关

【模块2:led_controller.v】好像没什么用........就闪烁

【模块3:usb_controller.v】超级重要!!!该模块产生 FX3 的 SlaveFIFO 读写操作时序,该模块检测 FX3 的 SlaveFIFO 中是否有发送来的数据,并将这些数据读取和缓存到 FPGA 的片内 FIFO 中,随后将这些数据写回到 FX3 的 SlaveFIFO 中。此模块中例化了fifo和ila分别供数据缓存和信号观察。

2.2相关知识点简介

2.2.1 FIFO IP核简介

PL端25~27:Vivado 中 FIFO IP 核使用与设计_哔哩哔哩_bilibili https://www.bilibili.com/video/BV1P5411A7Dx?p=1正点原子官方视频,讲解了FIFO IP核的使用。

https://www.bilibili.com/video/BV1P5411A7Dx?p=1正点原子官方视频,讲解了FIFO IP核的使用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2317

2317

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?