问题描述

在测试一个项目的I2C信号的SI时,发现I2C CLK 信号下降沿有过冲。

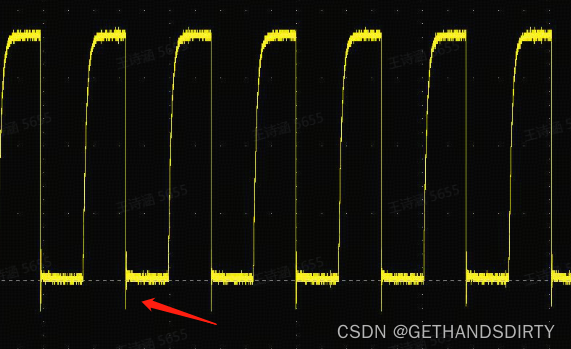

波形如下:

原因分析& 解决方案:

该路I2C的时钟频率为400kHz,属于fast mode;

实测I2C CLK的上升沿为200ns,下降沿为2ns;

在PCB上走微带线,走线长度为5000mil。

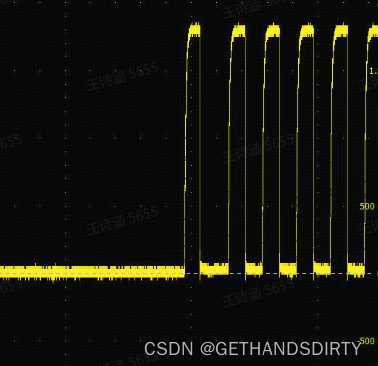

猜测是由于走线过长,下降沿过快,高频分量在源端和终端之间发生多次反弹,导致振铃(过冲)现象发生。解决的办法是在源端增加一个22ohm串联电阻,增加后过冲消失,波形如下:

设计总结:

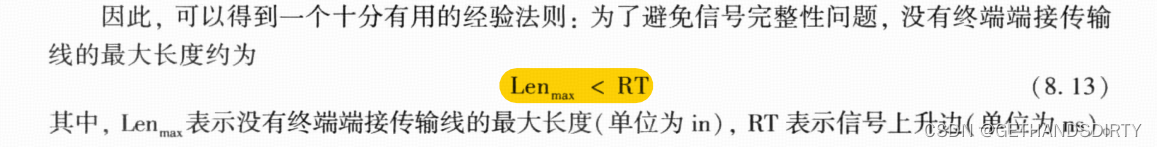

那么走线多长的信号需要增加端接呢?这与走线长度(传输时延)、信号频率(上升沿、下降沿时间)有关。《信号完整性与电源完整性分析》的第八章有详细讲述,书中有一个比较方便的估算法则是:

在本例中下降沿为2ns,那么也就是走线长度在2in以上就需要端接,换算成mil就是2000mil,而我们的走线是5000mil,是需要端接来保证信号完整性的。

1359

1359

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?