一.什么是时钟系统

时钟是工作中的同步节拍。S5PV210裸机开发中时钟是一个很重要的部分,需要通过一定的频率来控制信号的发送。系统中有很多器件协同工作,就需要这些时钟信号来协调管理。而这些时钟信号就是由时钟系统提供并且管理的。系统时钟一般由外部低频24MHZ晶体振荡器通过控制逻辑PLL倍频器倍频(实际上PLL倍频器的功能就是放大运行频率)产生。然后再时钟系统中就是通过不同的DIV分频器分频,来给不同的部件提供所需要的时钟的。

二.时钟域

因为S5PV210的时钟体系复杂,内部有众多模块,可以把内部的时钟划分为3大类时钟,及划分了3个域,使用四个倍频器(PLL),对应3个域分别是APLL为MSYS域提供使用、MPLL供DSYS使用、EPLL供PSYS使用,而剩余一个VPLL供video等相关的时钟使用。关于时钟域。

-

MSYS 复杂时钟系统中的主要核心的时钟信号又称为主系统时钟。包含CPU处理器内工作的时钟信号,及主频ARMCLK,为DMC0和DMC1使用的高频时钟HCLK_MSYS等,MSYS同时还为dram控制器,IRAM、IROM、中断控制器提供时钟信号。

-

DSYS 是和显示有关的时钟模块,包含高频时钟HCLK_DSYS、低频时钟PCLK_DSYS。

-

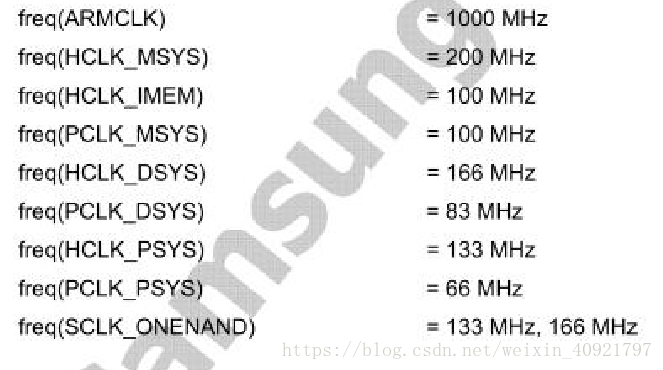

PSYS 和各个外围设备有关的时钟模块,比如各种接口。包含高频时钟HCLK_PSYS、低频时钟PCLK_PSYS、SCLK_ONENAND。

各类时钟参考值:

三.时钟源

s5pv210外部有四个晶振接口,我们设计板子硬件时,可以根据需要决定在哪里接入晶振。接了晶振之后,相应的模块就能产生震荡,产生原始时钟,原始时钟因为频率不一不好控制,所以经过一系列的筛选开关进入相应的PLL电路生成倍频后的高频信号,高频信号再经过分频到达芯片内部各个模块上。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

733

733

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?