EDA 电子设计自动化VHDL系列课程1–加【减】法器的设计

本EDA系列介绍的系统环境是:

软件: VHDL编程语言 ;

工具: Quartus13.0

FPGA 芯片是: Cyclone III : EP3C10E144C8

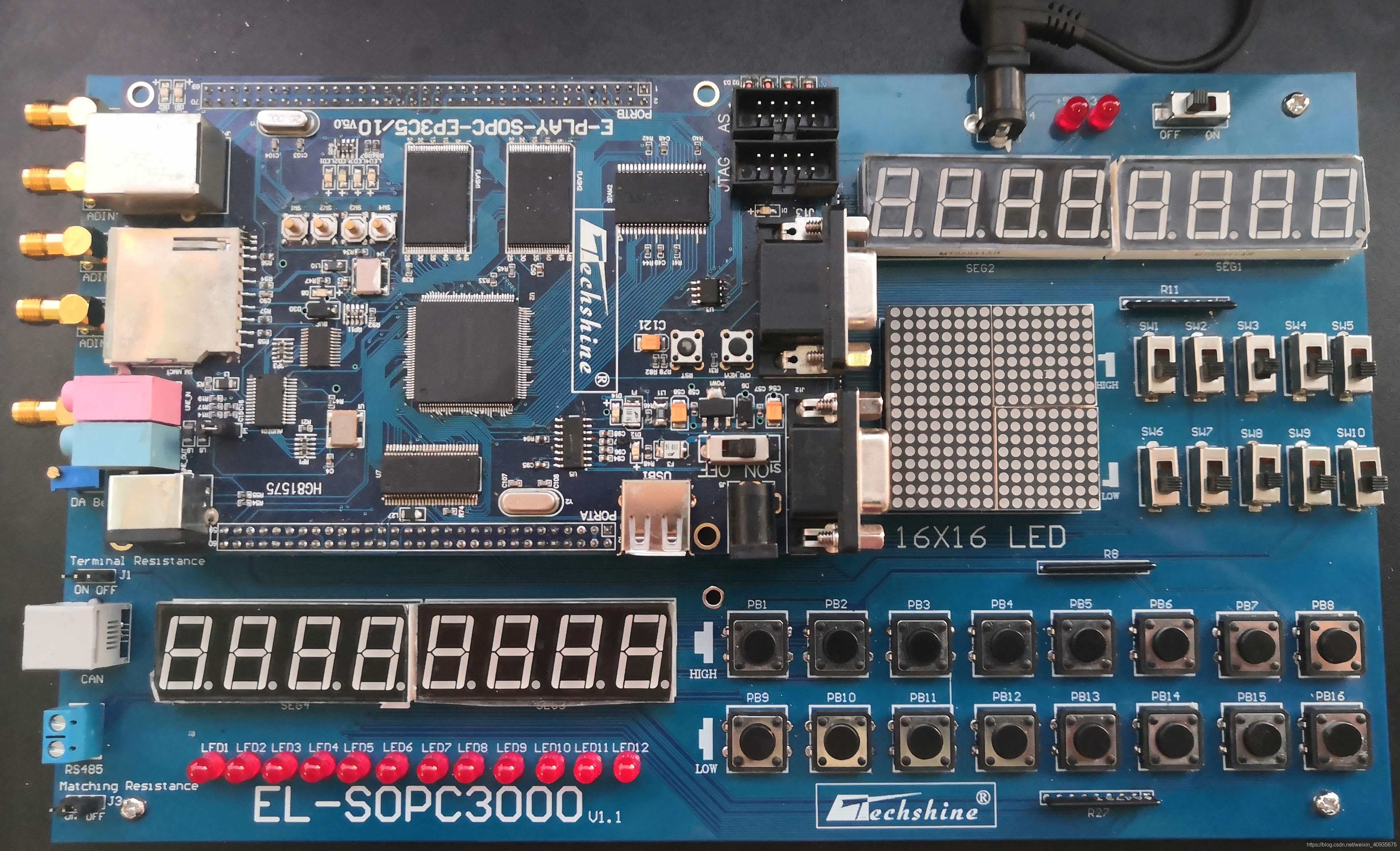

实验电路板:

该电路板 有 10个机械开关输入端,和 16个机械按钮 输入端。(机械开关表示上升沿和下降沿产生抖动调变,对时序电路产生不良影响)。

有16个 LED 8段码显示器,和16*16 点阵式显示器。

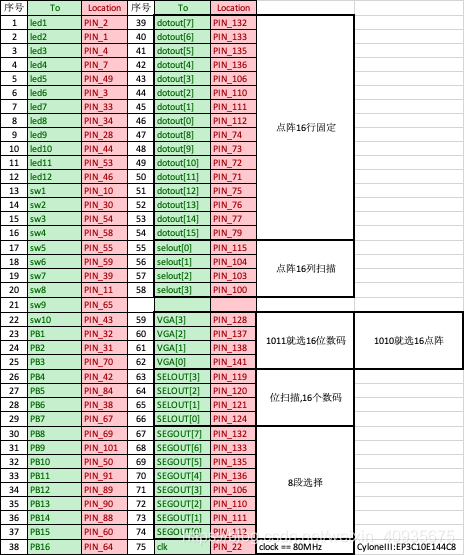

引脚链接方式:

1)一位半加器【加法器】的设计:

逻辑表达式:

Si=Ai⊕Bi

Co=Ai·Bi

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY ssum IS

PORT

(

A : IN STD_LOGIC; B : IN STD_LOGIC;

S : OUT STD_LOGIC; CO : OUT STD_LOGIC

);

END ssum;

ARCHITECTURE bdf_

该博客是EDA电子设计自动化VHDL系列课程的第一部分,主要讲解如何设计加法器。内容涵盖了一位半加器和一位全加器的逻辑表达式,以及使用Quartus13.0工具和Cyclone III FPGA芯片进行设计的环境介绍。实验电路板具有10个开关输入和16个LED显示输出,详细阐述了加法器的引脚链接方式和设计过程。

该博客是EDA电子设计自动化VHDL系列课程的第一部分,主要讲解如何设计加法器。内容涵盖了一位半加器和一位全加器的逻辑表达式,以及使用Quartus13.0工具和Cyclone III FPGA芯片进行设计的环境介绍。实验电路板具有10个开关输入和16个LED显示输出,详细阐述了加法器的引脚链接方式和设计过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

674

674

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?