EEPROM读写测试实验

EEPROM

EEPROM简介:EEPROM (Electrically Erasable Progammable Read Only Memory, E2PROM)即电可擦除可编程只读存储器,是一种常用的非易失性存储器(掉电数据不丢失)

领航者 ZYNQ开发板上使用的是 ATMEL 公司生产的 AT24C 系列的AT24C64这一型号。

AT24C64 存储容量为 64Kbit,内部分成 256 页,每页 32 字节, 共有 8192 个字节,且其读写操作都是以字节为基本单位。可以把 AT24C64 看作一本书,那么这本书有 256 页,每页有 32 行,每行有 8 个字,总共有 256328=65536个字,对应着 AT24C64 的 64*1024=65536 个 bit

因为AT24C64 共有 8192 个=2^13个字节,所以字地址共有13位即A0~A12

由于 AT24C64 采用两线串行接口的双向数据传输协议——I2C 协议实现读写操作,所以我们有必要了解一下 I2C 协议。

IIC协议

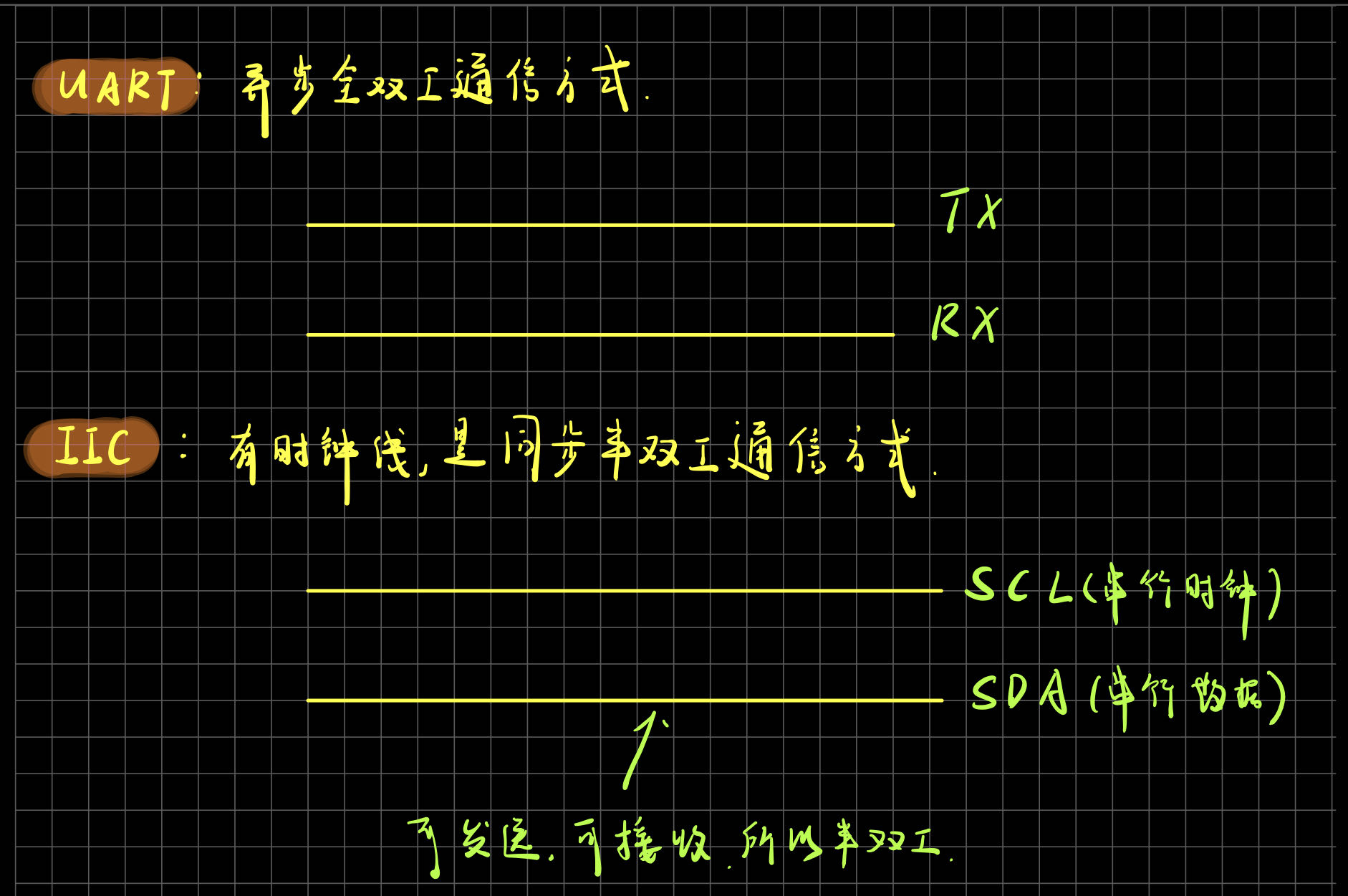

I2C 即 Inter-Integrated Circuit(集成电路总线),一种简单、双向、二线制总线标准。多用于主机和从机在数据量不大且传输距离短的场合下的主从通信。主机启动总线,并产生时钟用于传送数据,此时任何接收数据的器件均被认为是从机。

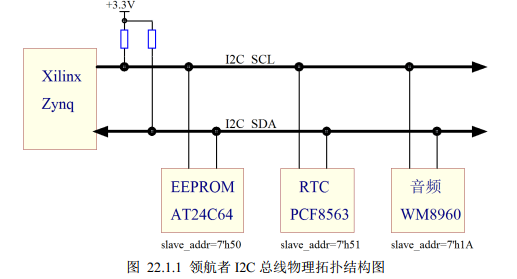

I2C 总线由数据线SDA和时钟线 SCL构成通信线路,既可用于发送数据,也可接收数据。 在主控与被控 IC 之间可进行双向数据传送 ,各种被控器件均并联在总线上,通过器件地址(SLAVE ADDR,具体可查器件手册)识别。我们领航者 I2C 总线物理拓扑结构如下图所示。

图中的 I2C_SCL 是串行时钟线, I2C_SDA 是串行数据线(一根双向数据线,所以IIC是半双工通信方式),由于 I2C 器件一般采用开漏结构与总线相连,所以 I2C_SCL 和 I2C_SDA 均需接上拉电阻,也正因此,当总线空闲时,这两条线路都处于高电平状态,当连到总线上的任一器件输出低电平,都将使总线拉低,即各器件的 SDA 及 SCL 都是“线与”关系。

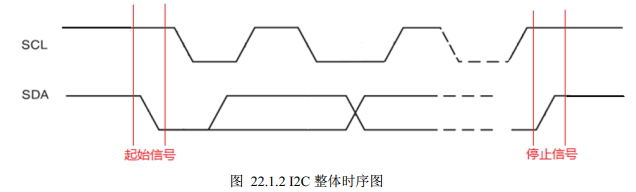

空闲状态 :SCL 和SDA都拉高

起始信号 :SCL 为高电平时将 SDA 线拉低

停止信号 :SCL 为高电平时, SDA 从低电平跳变到高电平

采用两线结构的 I2C 虽然只有一根数据线,但由于还有一条时钟线,可以让数据线在时钟线的带领下有顺序的传送,就好像单条道路上的车辆在交警或信号指示灯的指示下有规则的通行。那么_I2C 遵循怎样的规则_呢?

规则如下:

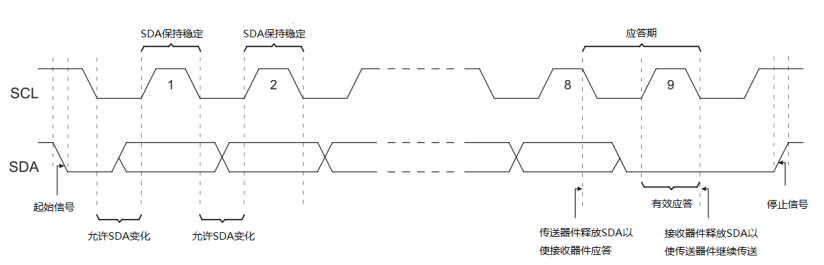

SCL 为高电平状态时, SDA 要求保持稳定

SCL 为低电平状态时, SDA 允许改变传输的数据位

当多个 I2C 器件挂接在总线上时,怎样才能与我们想要传输数据的器件进行通信

这就涉及到了器件地址(也称从机地址, SLAVE ADDRESS)

每个 I2C 器件都有一个器件地址,有些 I2C 器件的器件地址是固定的,而有些 I2C 器件的器件地址由一个固定部分和一个可编程的部分构成

比如 EEPROM 器件一般会留下 3 个管脚用于可编程地址位

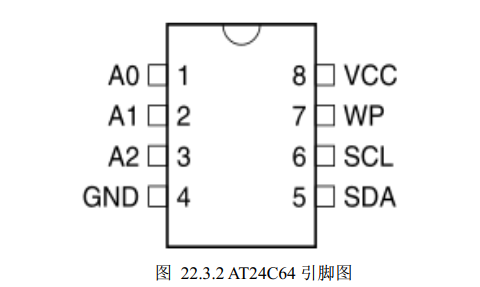

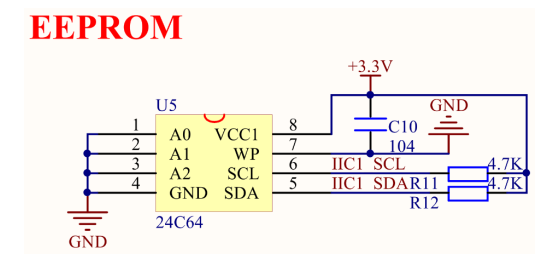

AT24C64 而言,其器件地址为 1010 加 3 位的可编程地址, 3 位可编程地址由器件上的 3 个管脚 A2、 A1、 A0(见图 22.3.2)的硬件连接决定。

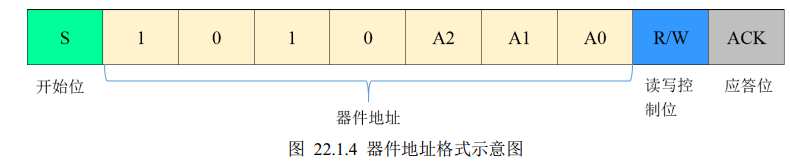

对于 AT24C64 来说,其传输器件地址格式如下图所示。

进行数据传输时,主机首先向总线上发出开始信号,对应开始位 S,然后按照从高到低的位序发送器件地址,一般为 7bit,第 8bit 位为读写控制位 R/W,该位为 0 时表示主机对从机进行写操作,当该位为 1时表示主机对从机进行读操作,然后接收从机响应。

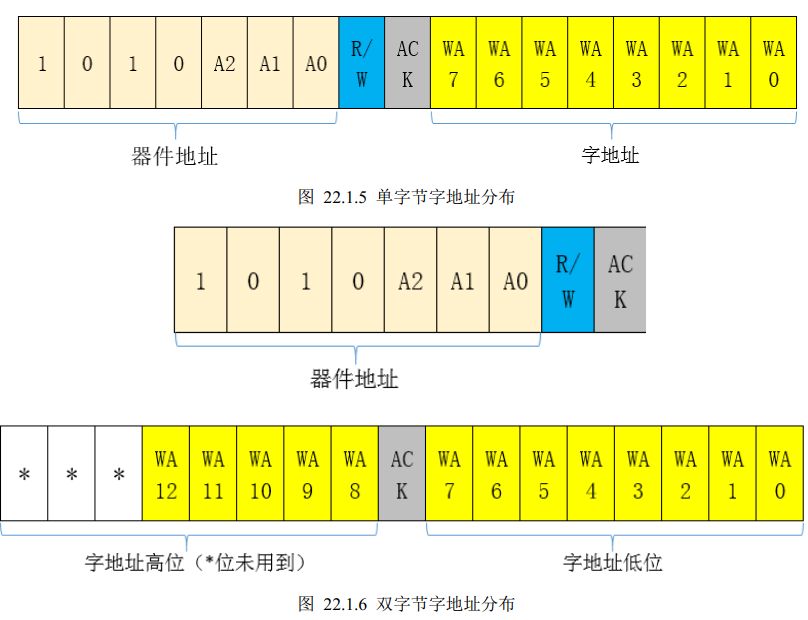

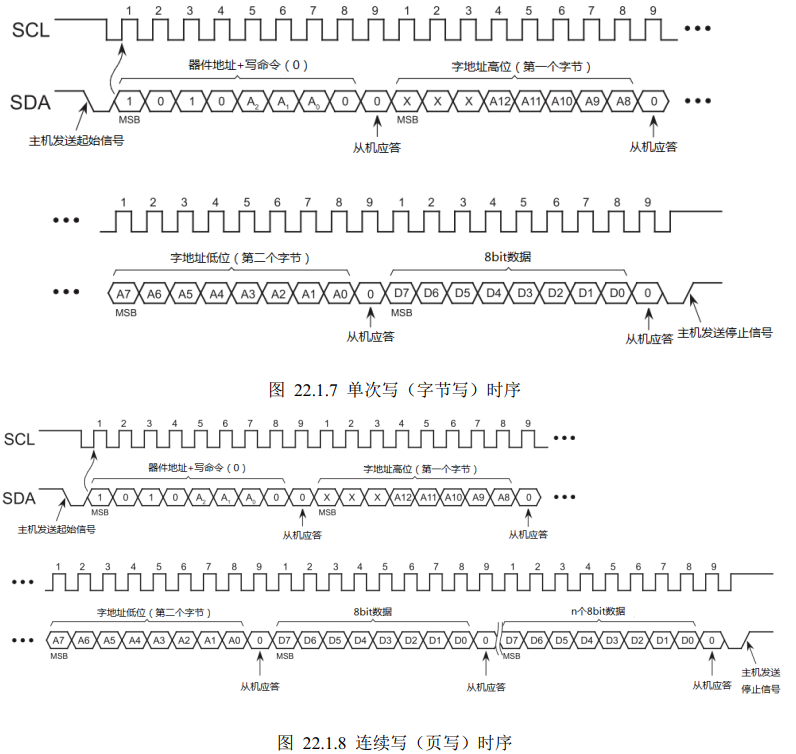

进行读写时,首先要指定存储单元的地址即字地址,然后再向该地址写入内容。该地址为一个或两个字节长度, 具体长度由器件内部的存储单元的数量决定,当存储单元数量不超过一个字节所能表示的最大数量(2^8=256)时,用一个字节表示,超过一个字节所能表示的最大数量时,就需要用两个字节来表示

AT24C02 的存储单元容量为 2Kbit=256Byte(一般 bit 缩写为 b, Byte 缩写为 B) ,用一个字节地址即可寻址所有的存储单元,而 AT24C64 的存储单元容量为 64Kb=8KB,需要 13 位(2^13=8KB)的地址位,而 I2C 又是以字节为单位进行传输的,所以需要用两个字节地址来寻址整个存储单元

写数据分为单次写(对于 EEPROM 而言,称为字节写)和连续写(对于 EEPROM 而言,称为页写)

硬件设计

AT24C64 的引脚功能如下:

A2,A1,A0:可编程地址输入端。

GND:电源地引脚

SDA: SDA(Serial Data,串行数据) 是双向串行数据输入/输出端。

SCL: SCL(Serial clock,串行时钟)串行时钟输入端。

WP(写保护) : AT24C64 有一个写保护引脚用于提供数据保护,当写保护引脚连接至 GND 时,芯片可以正常写,当写保护引脚连接至 VCC 时,使能写保护功能,此时禁止向芯片写入数据,只能进行读操作。

VCC:电源输入引脚

领航者 Zynq 开发板上 EEPROM 的原理图如图

程序设计

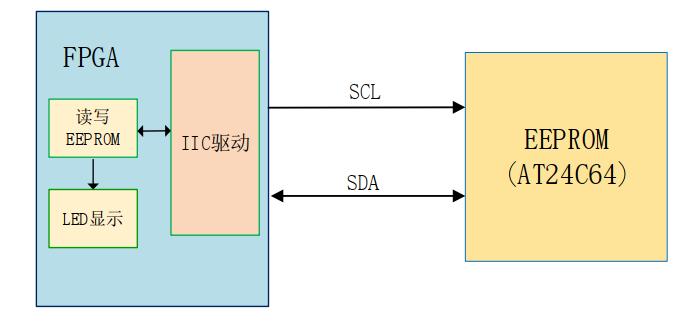

我们可以大致规划出系统的控制流程:首先 FPGA 向 EEPROM 写数据,写完之后从

EEPROM 读出所写入的数据,并判断读出的数据与写入的数据是否相同,如果相同则 LED 灯常亮,否则LED 灯闪烁。由此画出系统的功能框图如下图所示:

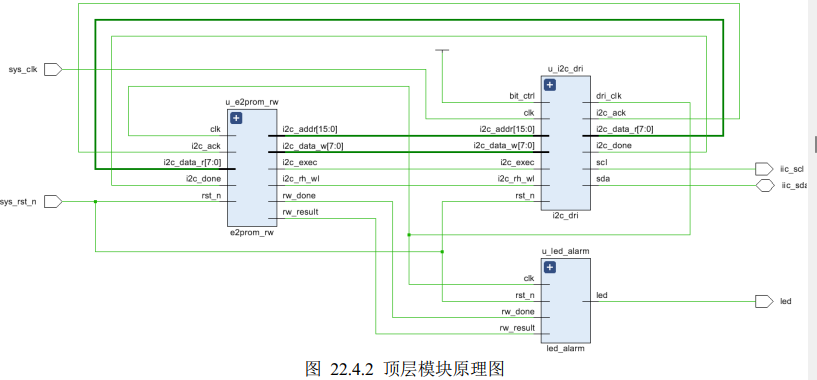

由系统总体框图可知, FPGA 部分包括四个模块, 顶层模块(e2prom_top)、读写模块

(e2prom_rw)、 I2C 驱动模块(i2c_dri)和 LED 灯显示模块(led_alarm) 。 其中在顶层模块中完成对其

余模块的例化。

各模块端口及信号连接如下图所示:

i2c_dri 为 I2C 驱动模块,用来驱动 I2C 的读写操作。当 FPGA 通过 EEPROM 读写模块 e2prom_rw 向EEPROM 读写数据时,拉高 i2c 触发控制信号 i2c_exec 以使能 I2C 驱动模块,并使用读写控制信号i2c_rh_wl 控制读写操作,当 i2c_rh_wl 为低电平时, I2C 驱动模块 i2c_dri 执行写操作,当 i2c_rh_wl 为高电平时, I2C 驱动模块 i2c_dri 执行读操作。此外, e2prom_rw 模块通过 i2c_addr 接口向 i2c_dri 模块输入器件字地址,通过 i2c_data_w 接口向 i2c_dri 模块输入写的数据,并通过 i2c_data_r 接口读取 i2c_dri 模块读到的数据,rw_done 信号是读写测试完成的标志, rw_result 是读写测试的结果。

口向 i2c_dri 模块输入写的数据,并通过 i2c_data_r 接口读取 i2c_dri 模块读到的数据,rw_done 信号是读写测试完成的标志, rw_result 是读写测试的结果。

5186

5186

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?