高速AD/DA实验

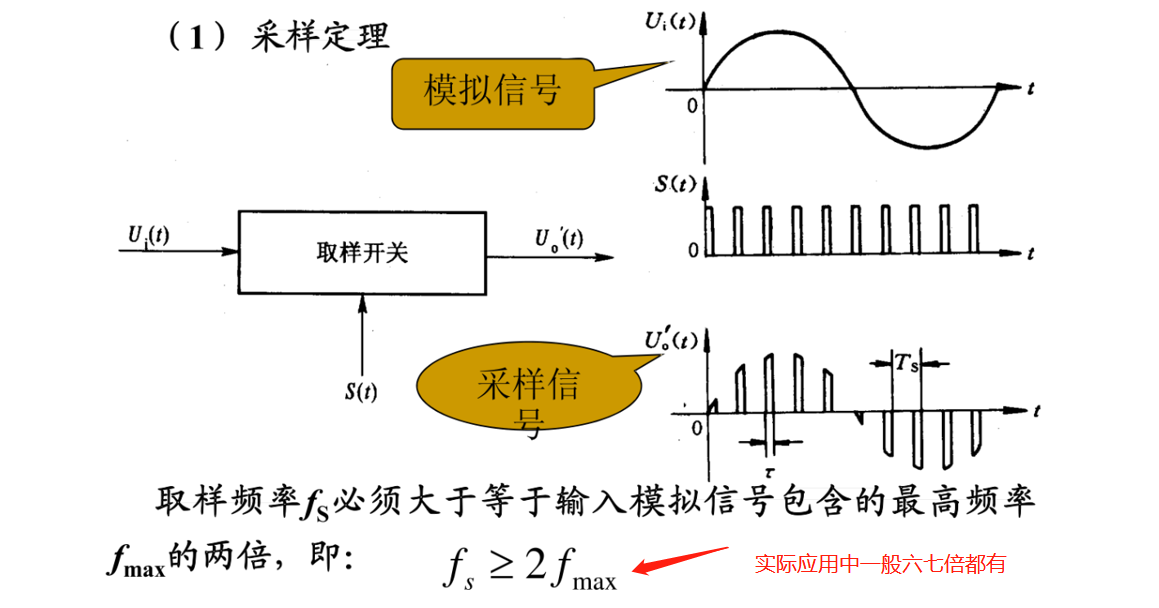

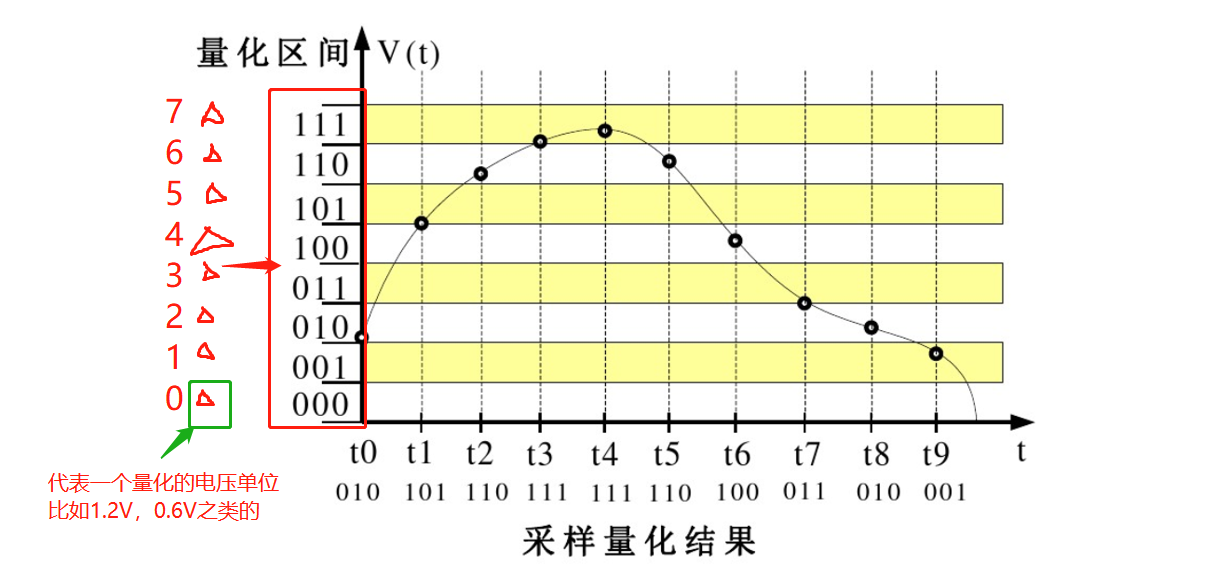

AD/DA原理

D/A: 就是将_数字量转换成模拟量_

A/D: 就是将_模拟量转换成数字量_,模拟量可以是电压电流等电信号也可以是声、光、压力、湿度等连续变化的非电物理量,但是这些非电物理量最终都要通过一定手段转换成电信号

分类

DAC

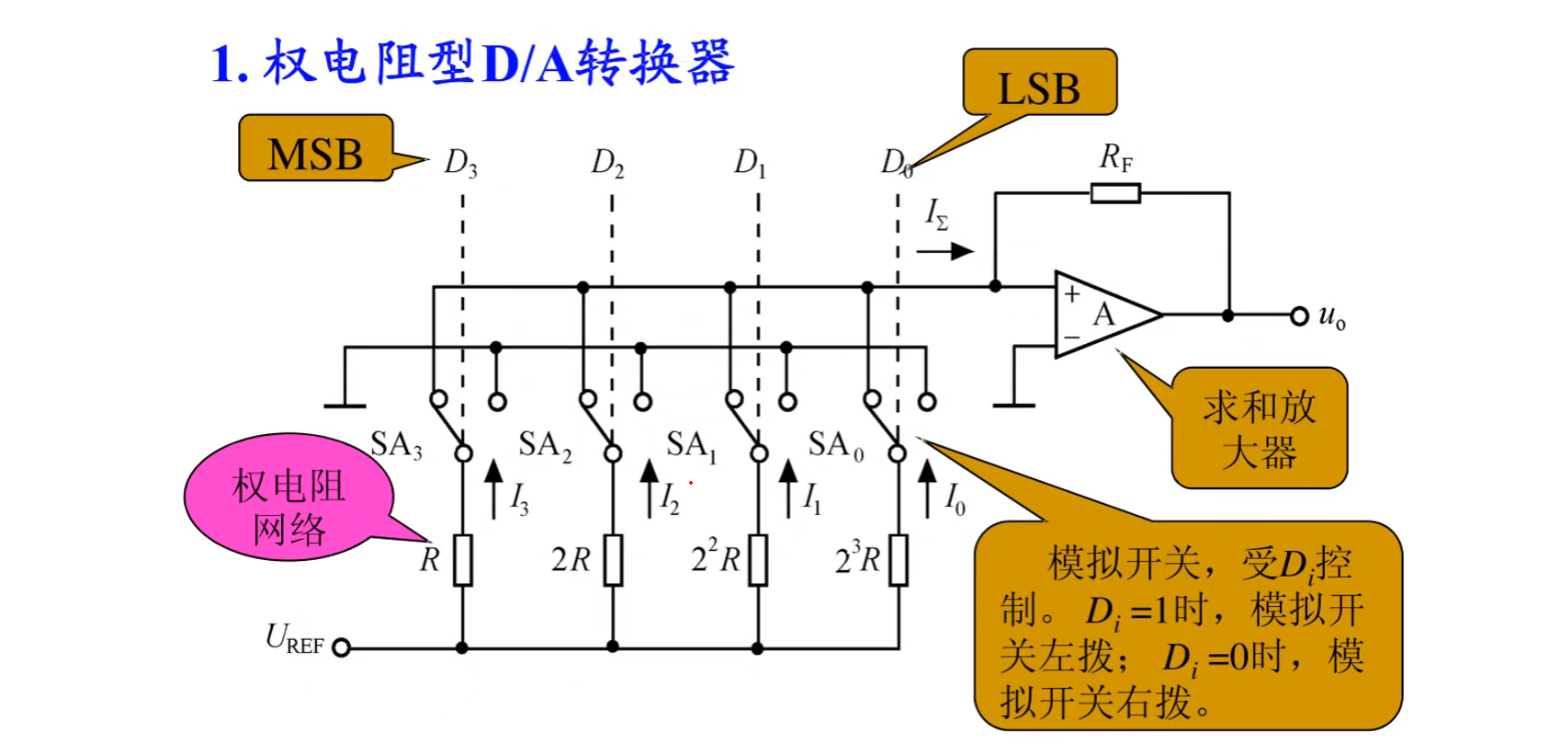

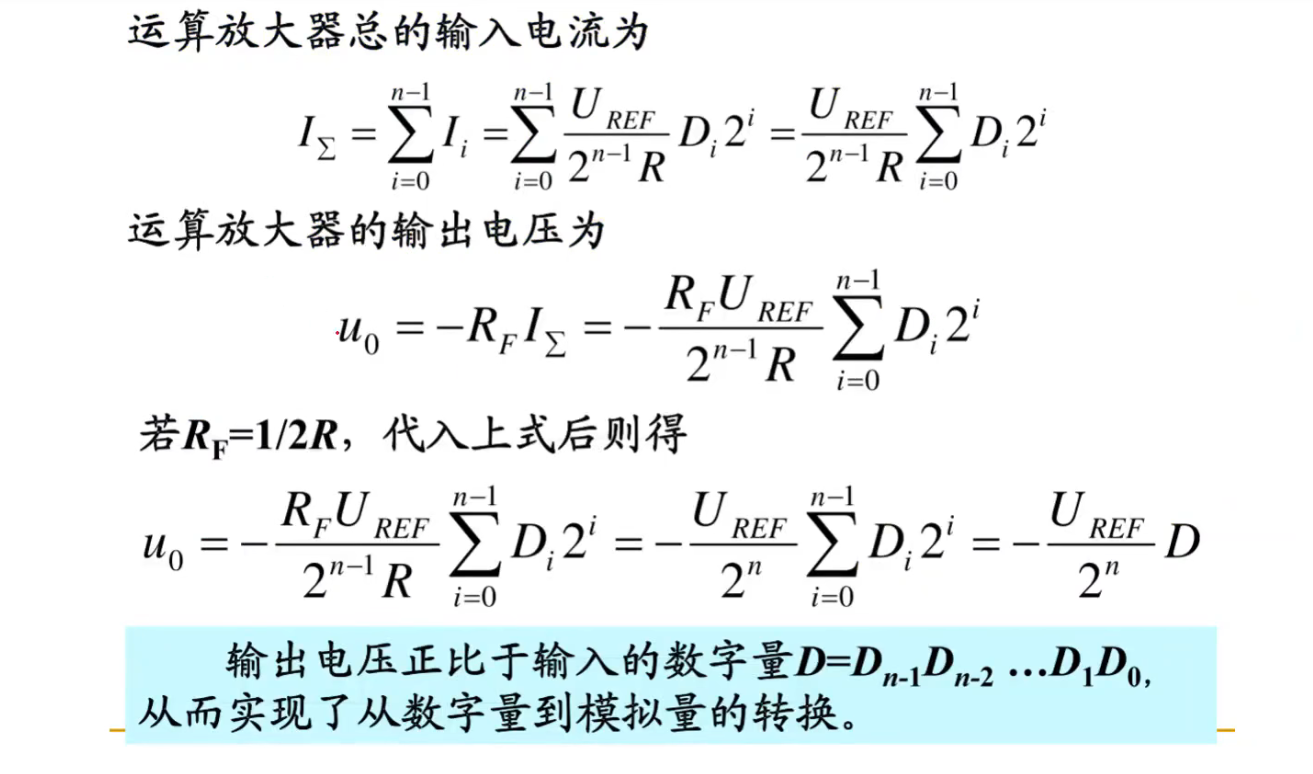

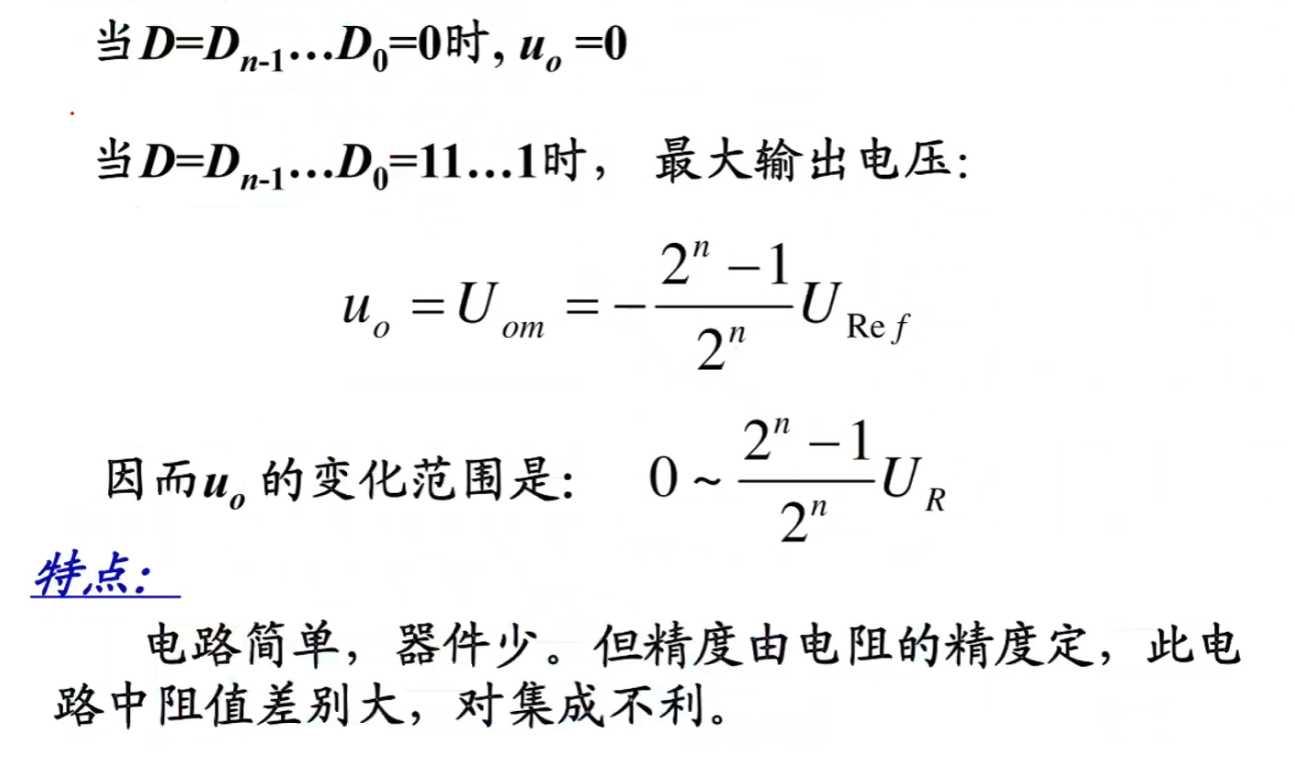

网络权电阻DAC(本次实验所用类型)

倒梯形电阻网络DAC

权电流型DAC

权电容型DAC

开关树型DAC

ADC

直接ADC

间接ADC

输入/输出方式

并行

串行

高速AD/DA简介

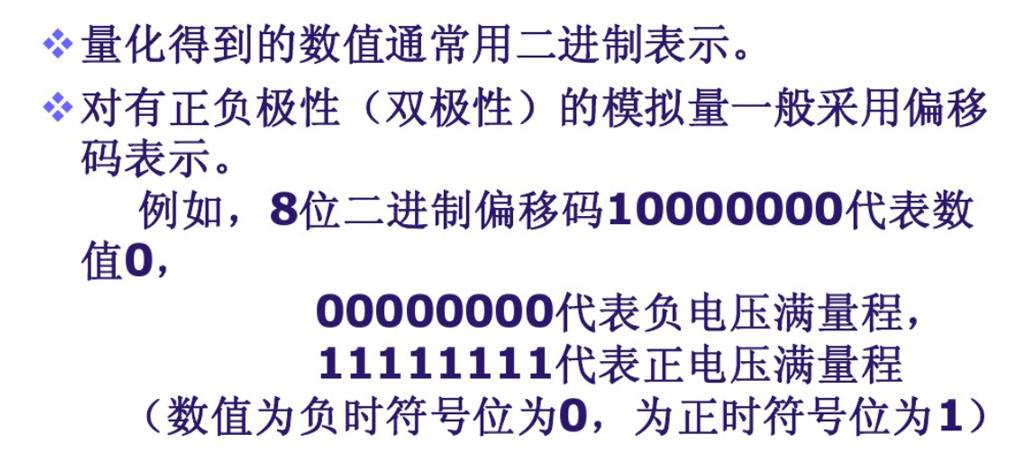

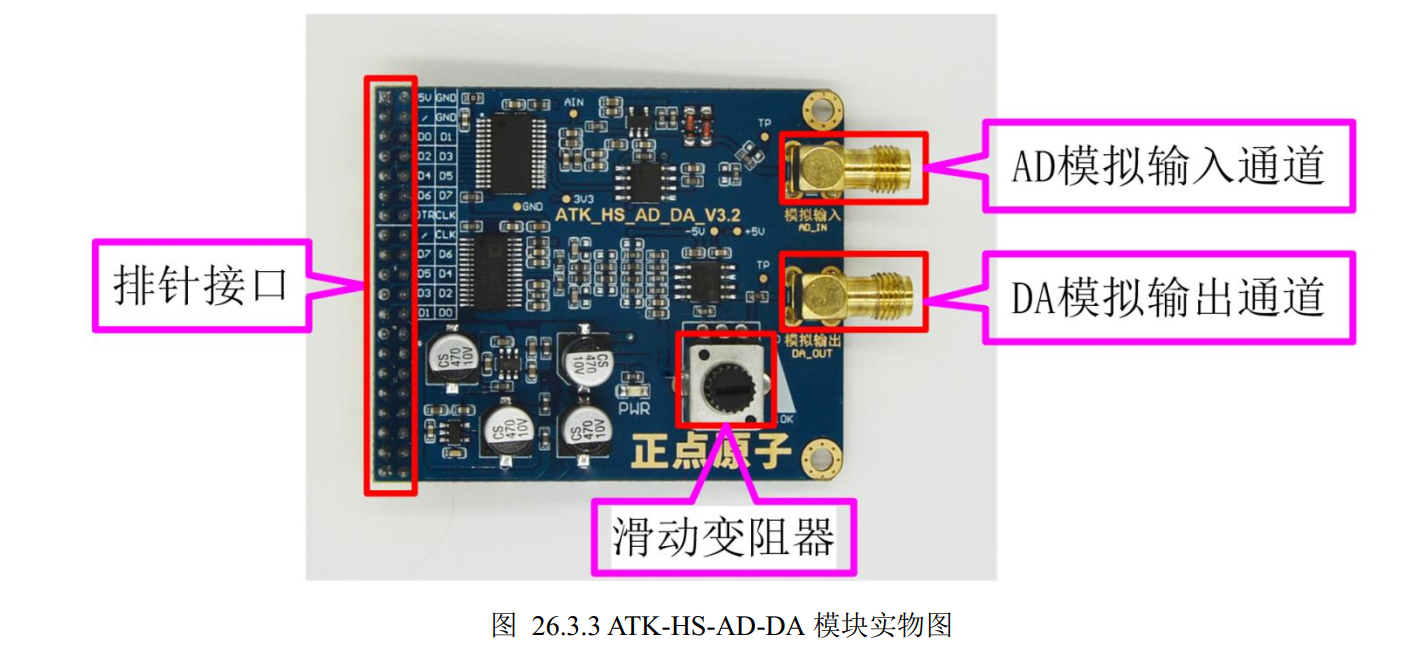

本章我们使用的 AD-DA 模块是正点原子推出的一款高速模数-数模转换模块(ATK_HS_AD_DA) ,高速 AD 转换芯片和高速 DA 转换芯片都是由 ADI 公司生产的,分别是 AD9280/3PA9280(两款芯片兼容)和 AD9708。

ATK_HS_AD_DA 模块的硬件结构图如下图所示。

AD9708 芯片 AD9708 Data Sheet (waveshare.net)

AD9280 芯片 AD9280 Data Sheet (waveshare.net)

硬件设计

ATK_HS_AD_DA 模块由 DA 转换芯片(AD9708) 和 AD 转换芯片(AD9280) 组成。

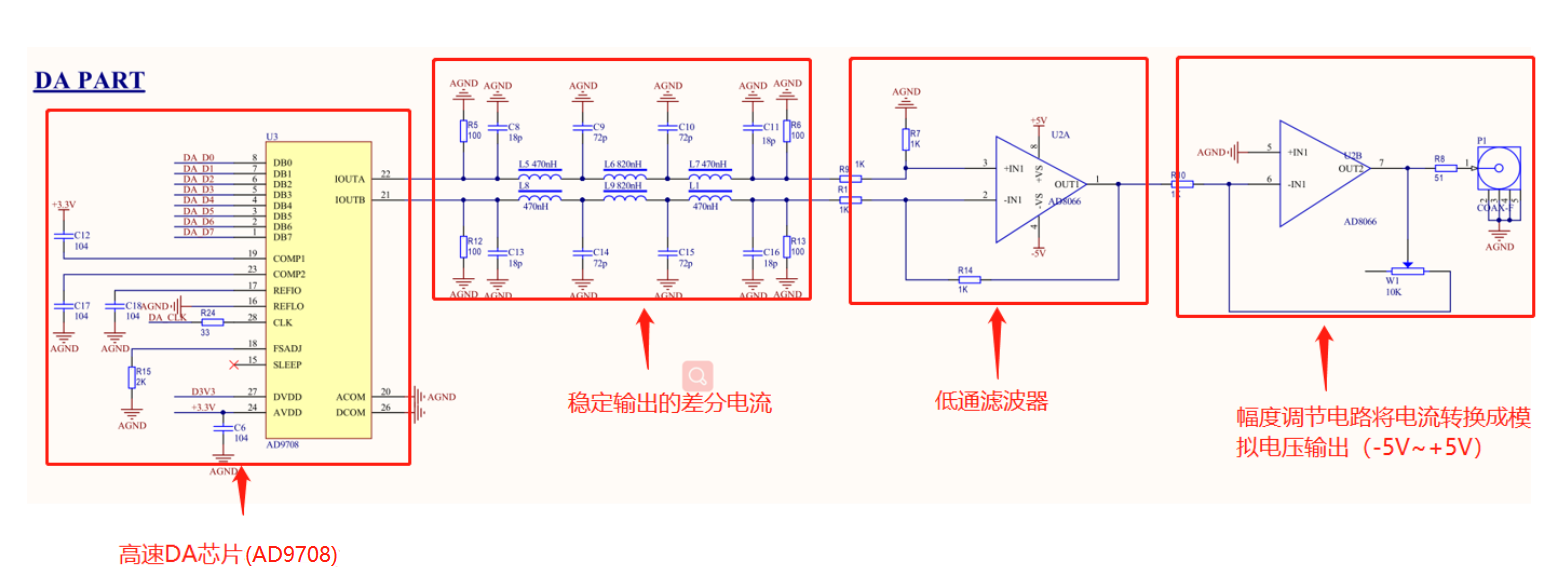

AD9708 的原理图如下图所示。

由上图可知, AD9708 输出的一对差分电流信号先经过滤波器,再经过运放电路得到一个单端的模拟电压信号。 图中右侧的 W1 为滑动变阻器, 可以调节输出的电压范围,推荐通过调节滑动变阻器,使输出的电压范围在-5V 至+5V 之间, 从而达到 AD 转换芯片的最大转换范围。

AD9280 的原理图如下图所示

上图中输入的模拟信号 SMA_IN(VI) 经过衰减电路后得到 AD_IN2(VO) 信号,两个模拟电压信号之间的关系是 VO=VI/5+1, 即当 VI=5V 时, VO=2V; VI=-5V 时, VO=0V。

ATK_HS_AD_DA 模块的实物图如下图所示。

本实验中,各端口信号的管脚分配如下表所示。

| 信号名 | 方向 | 管脚 | 端口说明 | 电平标准 |

|---|---|---|---|---|

| sys_clk | input | U18 | 系统时钟, 50Mhz | LVCMOS33 |

| sys_rst_n | input | N16 | 系统复位, 低有效 | LVCMOS33 |

| da_clk | output | R18 | DA(AD9708)驱动时钟 | LVCMOS33 |

| da_data[0] | output | R17 | 输出给DA的数据 | LVCMOS33 |

| da_data[1] | output | R16 | 输出给DA的数据 | LVCMOS33 |

| da_data[2] | output | W19 | 输出给DA的数据 | LVCMOS33 |

| da_data[3] | output | W18 | 输出给DA的数据 | LVCMOS33 |

| da_data[4] | output | P16 | 输出给DA的数据 | LVCMOS33 |

| da_data[5] | output | P15 | 输出给DA的数据 | LVCMOS33 |

| da_data[6] | output | Y19 | 输出给DA的数据 | LVCMOS33 |

| da_data[7] | output | Y18 | 输出给DA的数据 | LVCMOS33 |

| ad_data[0] | input | V16 | AD输入数据 | LVCMOS33 |

| ad_data[1] | input | W16 | AD输入数据 | LVCMOS33 |

| ad_data[2] | input | T14 | AD输入数据 | LVCMOS33 |

| ad_data[3] | input | T15 | AD输入数据 | LVCMOS33 |

| ad_data[4] | input | Y17 | AD输入数据 | LVCMOS33 |

| ad_data[5] | input | Y16 | AD输入数据 | LVCMOS33 |

| ad_data[6] | input | T16 | AD输入数据 | LVCMOS33 |

| ad_data[7] | input | U17 | AD输入数据 | LVCMOS33 |

| ad_otr | input | V17 | 模拟电压超出量程标志 | LVCMOS33 |

| ad_clk | output | V18 | AD(AD9280)驱动时钟 | LVCMOS33 |

程序设计

根据本章的实验任务, ZYNQ 需要连续输出正弦波波形的数据,才能使 AD9708 连续输出正弦波波形的模拟电压,如果通过编写代码使用三角函数公式运算的方式输出正弦波数据, 那么程序设计会变得非常复杂。在工程应用中, 一般将正弦波波形数据存储在 RAM 或者 ROM 中,由于本次实验并不需要写数据到 RAM 中,因此我们将正弦波波形数据存储在只读的 ROM 中,直接读取 ROM 中的数据发送给 DA 转换芯片即可

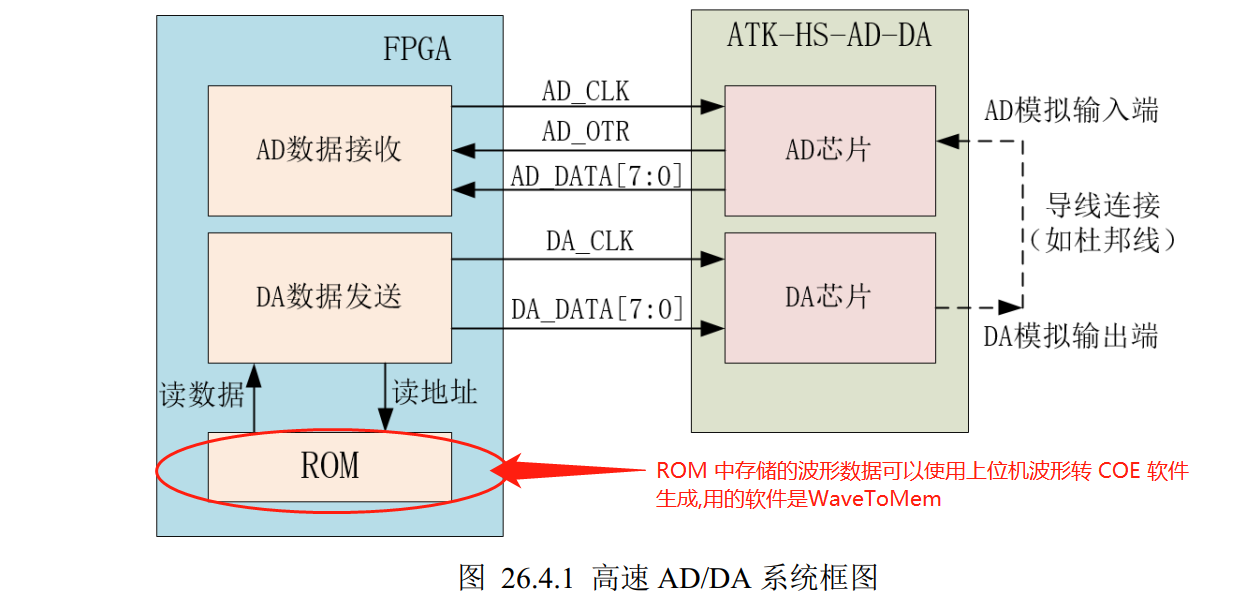

图 26.4.1 是根据本章实验任务画出的系统框图。 ROM 里面事先存储好了正弦波波形的数据, DA 数据发送模块从 ROM 中读取数据,将数据和时钟送到 AD9708 的输入数据端口和输入时钟端口; AD 数据接收模块给 AD9280 输出驱动时钟信号和使能信号,并采集 AD9280 输出模数转换完成的数据。

高速 AD/DA 实验的系统框图如图 26.4.1 所示:

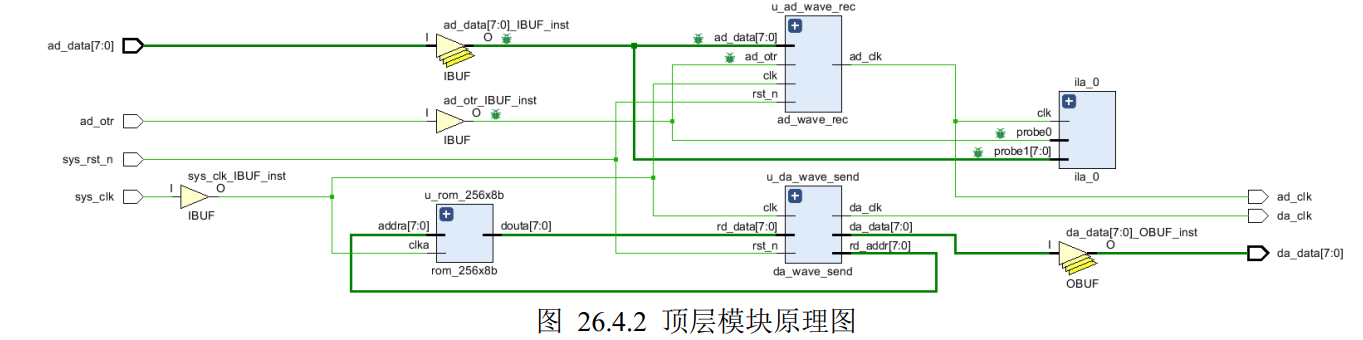

顶层模块的原理图如下图所示:

FPGA 顶层模块(hs_ad_da) 例化了以下三个模块: DA 数据发送模(da_wave_send)、 ROM 波形存储模块(rom_256x8b)和 AD 数据接收模块(ad_wave_rec) 。

DA 数据发送模块(da_wave_send) : DA 数据发送模块输出读 ROM 地址, 将输入的 ROM 数据发送至 DA 转换芯片的数据端口。

ROM 波形存储模块(rom_256x8b): ROM 波形存储模块由 Vivado 软件自带的 Block Memory Generator IP 核实现, 其存储的波形数据可以使用波形转存储文件的上位机来生成.coe 文件。

AD 数据接收模块(ad_wave_rec): AD 数据接收模块输出 AD 转换芯片的驱动时钟和使能信号,随后接收 AD 转换完成的数据。

顶层模块(hs_ad_da)

module hs_ad_da(

input sys_clk , //系统时钟

input sys_rst_n , //系统复位,低电平有效

//DA芯片接口

output da_clk , //DA(AD9708)驱动时钟,最大支持125Mhz时钟

output [7:0] da_data , //输出给DA的数据

//AD芯片接口

input [

本文详细介绍了高速AD/DA转换实验,包括AD/DA原理、硬件设计和程序设计。在硬件部分,重点讲解了AD9708和AD9280芯片的工作原理及电路设计。在程序设计中,提到了如何利用ROM存储正弦波数据,并通过FPGA实现数据发送和接收。在实验过程中遇到的ILA波形显示问题及超量程问题,通过调整采样时钟频率和相位得到了解决。

本文详细介绍了高速AD/DA转换实验,包括AD/DA原理、硬件设计和程序设计。在硬件部分,重点讲解了AD9708和AD9280芯片的工作原理及电路设计。在程序设计中,提到了如何利用ROM存储正弦波数据,并通过FPGA实现数据发送和接收。在实验过程中遇到的ILA波形显示问题及超量程问题,通过调整采样时钟频率和相位得到了解决。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9749

9749

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?