EEPROM是什么

EEPROM (E2PROM,Electrically Erasable Progammable Read Only Memory)即电可擦除可编程只读存储器,是一种常用的非易失性存储器。不同厂家的产品,相同厂家不同型号、系列的产品,它们的寿命也不尽相同,100万次为常见主流产品。

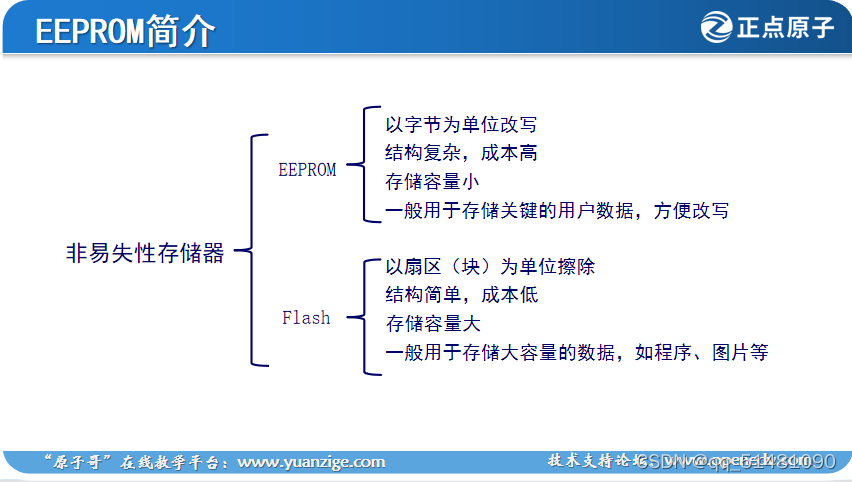

这是正点原子的ppt,讲述EEPROM与FLASH的区别。

简单说,就是EEPROM对数据的操作更加细腻,能够精确到每个字节进行操作,且存储容量较小,一般用于存储一些重要数据,例如传感器的关键参数。

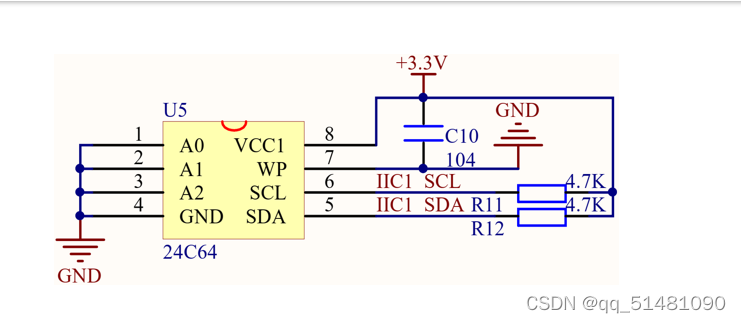

一般的EEPROM芯片具有以下的接口

其中A0,A1,A2为地址线,(IIC器件地址: 每一个IIC器件都有一个器件地址,有的器件地址在出厂时地址就设定好了,用户不可以更改,比如OV7670的地址为0x42。有的器件例如EEPROM,前四个地址已经确定为1010,后三个地址是由硬件链接确定的,所以一IIC总线最多能连8个EEPROM芯片。)GND为底线提供相对电压,WP为writeprotect,控制是否进行写操作,SCL与SDC为IIC接口,其中SCL为时钟线(同步),SDA为数据传输线(双向),但由于只有一根数据线属于半双工通信方式。

IIC与UART

IIC (I2C,Inter-Integrated Circuit)即集成电路总线,是一种两线式串行总线,由PHILIPS公司开发用于连接微控制器及其外围设备。多用于主机和从机在数据量不大且传输距离短的场合下的主从通信。

可有多个从机但只能有一个主机。

分为标准,快速,高速三种模式。

其中标准约为100k/s

快速约为400k/s

高速约为3.4M/s

其中传输速度由芯片所接电压决定

通常一个FPGA芯片的SCL与SDA接口能同时接多根线,达到节省串口的目的。通俗来说,所有从机的SDA线都接到主机的SDA总线上,SCL线同理。

总的来说,I2C 总线在物理连接上非常简单,分别由SDA(串行数据线)和SCL(串行时钟线)及上拉电阻组成。通信原理是通过对SCL和SDA线高低电平时序的控制,来产生I2C总线协议所需要的信号进行数据的传递。在总线空闲状态时,SCL和SDA被上拉电阻Rp拉高,使SDA和SCL线都保持高电平。

协议层上,具有开始,结束,应答等多种时序状态。

而UART是一种通用串行数据总线,用于异步通信。该总线双向通信,有两根数据线,可以实现全双工传输和接收。在嵌入式设计中,UART用来主机与辅助设备通信,如汽车音响与外接AP之间的通信,与PC机通信包括与监控调试器和其它器件,如EEPROM通信。

对EEPROM进行读写操作

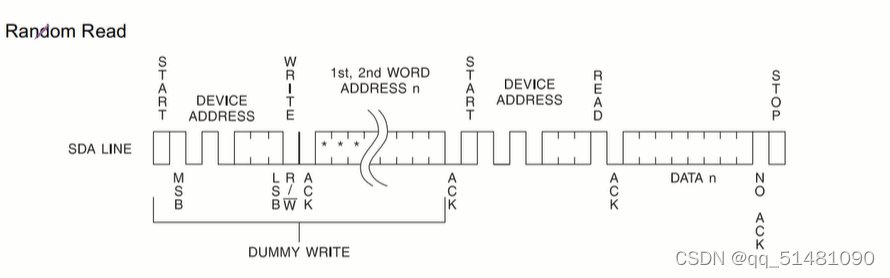

先说IIC接口的基本时序。拿随机读举例。

没有数据交互的情况下,SDA与SCL线通过上拉电阻同时拉高。

要传输数据,先让SCL保持不变,SDA变为低,此为一个start信号。

然后SCL开始进入工作状态。(001000100....)

而由于要达成稳定的工作状态,必须SDA传输的数据在SCL为低的时候变化,在高的时候保持不变,所以下一步传输device address的时候一位一位的在SCL为0时往前传。

然就下一步,传输word address。

下一步,传输一个byte的data。

最后传输一个stop位。与start类似。SCL保持高电平。SDA由低电平变为高电平。

注:要使实现的IIC接口通用,需要设置address(word)的位数,来区分状态机的不同状态。

首先,EEPROM有三种工作模式。

第一,当前地址读,根据上一次写的工作指针来开始进行读操作,读一次自动加一,读完一个page会使page自动加一,而不像在写操作时会返回到该page的第一个byte开始写。

第二,随机读,灵活性较强。但是先要进行一次dummy write 来调整工作指针位置,所谓dummy write 指的是进行一次写操作,但是不写入任何数据,来进行当前地址读的操作。要读第1952个字节的数据,如果按照当前地址读的方式,最差的时间得用先读N个字节才行,其中N为字节总数。

第三,连续读。未读完之前,不发送stop位。节约时间,除第一次外,一直发送data即可。

注:address传输完后一般有ack位确认收到(由从机EEPROM发出)

1755

1755

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?