ADC_内部电路Rsh和Csh和转换速率Tconv以及频率fs

芯片内部的ADC结构

GD32F103芯片特征参数

与STM32F103x8对比

主要关注以下参数

fs(Sampling rate)=采样率

fADCCONV( ADC conversion time)=ADC转换时间

RADC( Input sampling switch resistance)=输入采样开关电阻

CADC( Input sampling capacitance)=输入采样电容

在原子的例程中 配置如下:

- 配置的STM32的系统时钟频率,例如:72MHZ。

- 设置的ADC分频因子,例如:RCC_PCLK2_Div6,即6分频。

- 设置的ADC采样时间,例如:ADC_SampleTime_239Cycles5, 即239.5个周期。(平常配的最大值)

计算可得

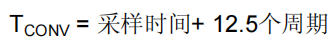

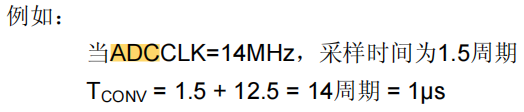

以系统时钟频率为72MHZ,ADC分频因子为RCC_PCLK2_Div6, ADC的采样时间为ADC_SampleTime_1Cycles5,进行计算

ADCCLK(ADC的时钟频率 ) = 72MHZ(系统时钟频率) / 6 (ADC分频因子) = 12MHZ。

一个ADC周期占用的时间 = 1 / 时钟频率 = 1 / 12MHZ = 0.0833334 uS

一次采样总的时间 = 采样时间 + 12.5个周期 = 1.5周期 + 12.5周期 = 14周期 = 14 * 0.0833334 = 1.166667 uS

两次采样间隔时间 = 1.166667 uS (ADCCLK为12MHZ时的最小采样间隔时间)

同理,计算ADCCLK为12MHZ时的最大采样间隔时间 = 239.5周期 + 12.5周期 = 252周期 = 252/12Mhz=21 uS

以下是裁剪STM32F103x8芯片手册中Rain中的最大值表格

TI德州仪器计算工具

参数有点差异,不过是类似的用法

ADC误差以及硬件用法

3492

3492

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?