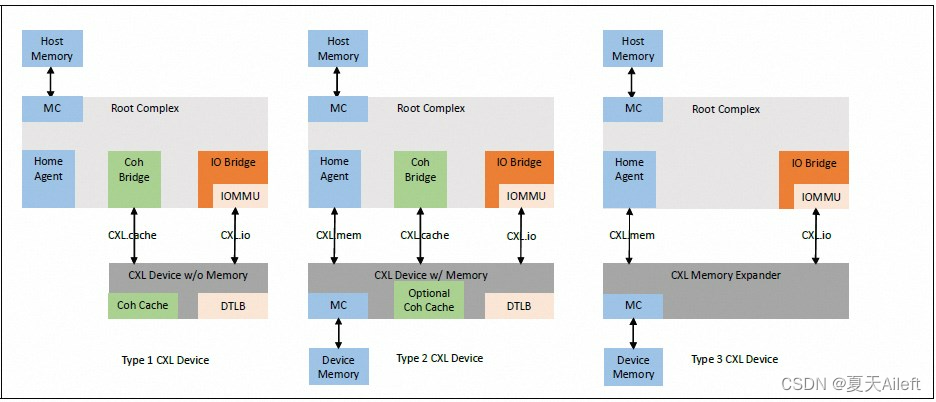

1.CXL三种设备类型

1.1 CXL支持三种设备类型:

Type1类支持CXL.io、CXL.cache;Type2类型设备支持CXL.io、CXL.cache以及CXL.mem;Type3类型设备支持CXL.io、CXL.mem。

无论哪种类型,CXL.io都是不可缺少的,因为设备的发现,枚举,配置等都是由CXL.io来负责。

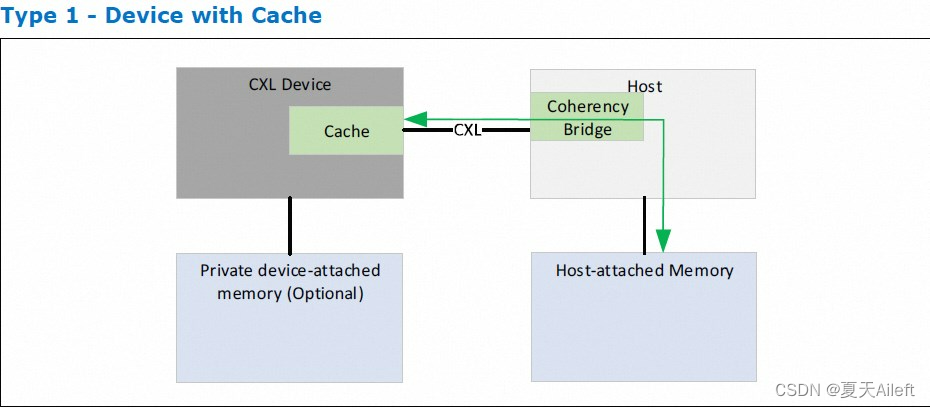

2.Type1 CXL设备

2.1应用设备类型:

Type 1设备的典型应用是网卡这类高速缓存设备。Type 1 CXL设备,应用于拥有完全一致性缓存的设备。对于这种设备,标准的生产者-消费者模型效果一般,比如,设备需要执行复杂的原子操作,而这些原子操作又不属于PCIe的标准原子操作。基本缓存一致性允许加速器实现它选择的任何排序模型,并允许它实现无限数量的原子操作。它们往往只需要少量的缓存,可以很容易地通过标准的处理器监听过滤(Snoop Filter)机制轻松跟踪。

Type 1设备支持的缓存大小取决于主机的监听过滤能力。CXL使用CXL.cache链接支持此类设备,加速器可以通过该链接使用CXL.cache协议进行缓存一致性事务。

总结来说,Type 1 CXL设备适用于具有完全一致性缓存的设备,通过支持基本缓存一致性和使用CXL.cache协议,加速器可以实现各种排序模型,并且能够执行大量的原子操作。这些设备通常只需要小量的缓存,并且可以通过标准的处理器监听过滤机制来管理和跟踪缓存一致性事务。

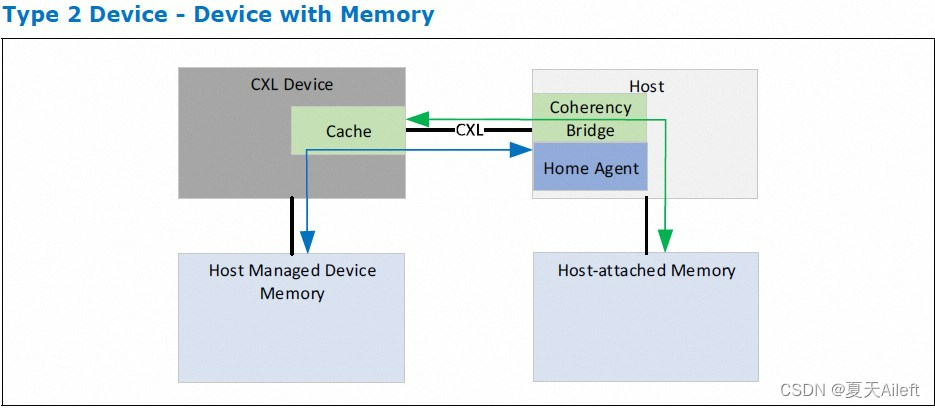

3.Type2 CXL设备

3.1应用设备类型:

Type 2设备的典型应用是GPU,FPGA,AI这类的加速器。Type 2设备除了一致性高速缓存外,还具有连接到设备的内存,例如DDR、高带宽内存(High Bandwidth Memory,HBM)等。这些设备的性能依赖于加速器和设备挂载内存(Device-attached Memory)之间的巨大带宽。CXL的关键目标是为主机提供一种将操作数推入设备挂载内存的方法,并为主机提供从设备挂载内存中提取结果的方法,这样就不会增加抵消加速器好处的软件和硬件成本。CXL将一致的系统地址映射设备连接内存称为“主机管理的设备内存“(Host-managed Device Memory,HDM)。

(HDM和传统PDM区别:HDM和传统IO/PCIe专用设备内存(Private Device Memory,PDM)之间有一个重要区别。用带有GDDR的GPGPU来举例,GPGPU往往将其GDDR视为私有。这意味着主机无法访问GDDR,并且与系统的其余部分不一致。它完全由设备硬件和驱动程序管理,主要用作具有大型数据集的设备的中间存储。这种模型的明显缺点是,在引入操作数并将结果写回时,它涉及大量从主机内存到设备连接内存的来回拷贝。HDM虽然也是挂载在设备端,但可以被主机直接访问)

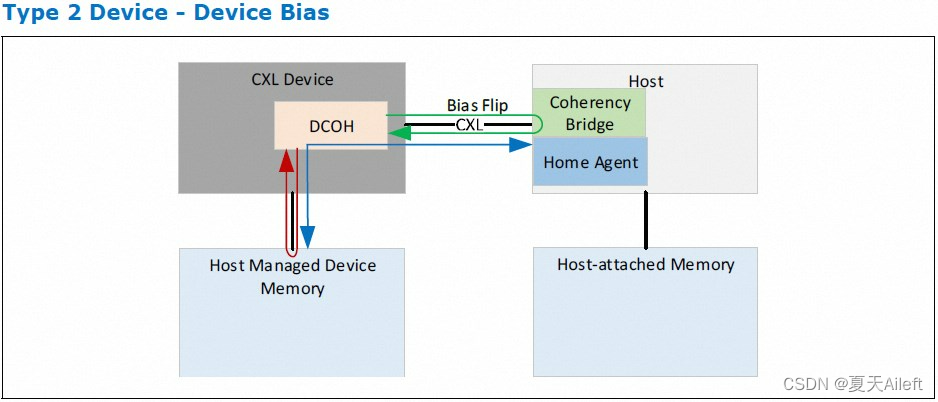

3.2 偏向一致性协议

3.2.1 两种状态

3.2.1.1 偏向主机(Host Bias):

当设备挂载内存偏向主机时,该内存就像常规的主机连接内存一样。也就是说,如果设备需要访问该内存,设备需要向主机发送一个请求,主机将解析请求的一致性。

偏向设备(Device Bias):当设备挂载内存处于偏向设备时,要保证主机中没有对应的缓存行副本。这样设备可以随意的访问设备挂载的存储,而不需要向主机发送任何的请求事务。

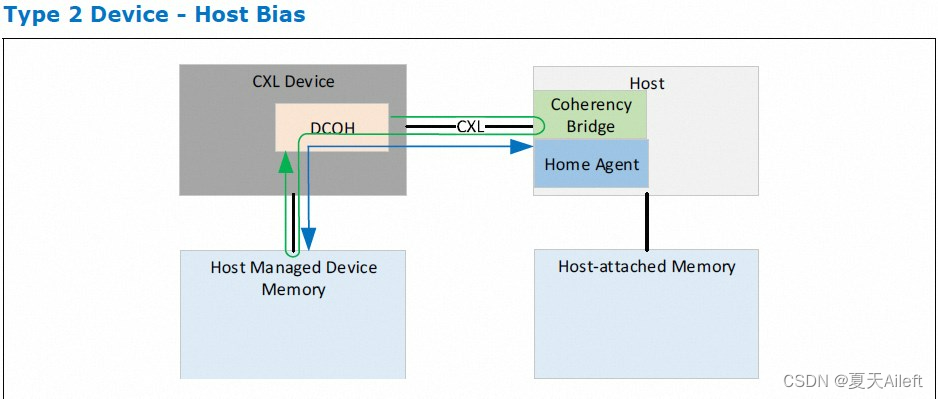

主机偏向性:

主机偏向模式通常是指在工作提交期间主机将操作数据写入内存,或在工作完成后从内存读取数据。如下图所示,内存挂在设备端。在主机偏向模式下,一致性数据流从主机到设备挂载内存,如图中的蓝色箭头所示。但是,设备对此内存的访问效率不是最佳的,因为需要通过主机,如图中的绿色箭头所示,设备先向主机发起请求,然后通过主机来访问HDM。

**优势:**主机偏向性使主机具有更大的灵活性和控制能力。主机可以更好地管理和协调链路上的设备,根据系统需求进行资源分配和配置。这种架构有助于实现更严格的系统管理和协同处理。

劣势:主机偏向性需要较复杂的主机固件和软件支持,增加了系统设计和开发的复杂度。此外,在主机故障或主机维修时,可能会中断整个链路上的设备工作。

3.2.1.2 设备偏向性:

在设备偏向模式下,设备负责工作提交和完成。在此模式下,设备需要对设备挂载内存完成高带宽和低延迟访问。设备无需询问主机的一致性引擎,而直接发起访问,如图中的红色箭头所示。主机仍然可以访问设备挂载的内存,但可能会被加速器强制放弃所有权,如图中的绿色箭头所示。设备访问HDM内存实现了延迟低,带宽高,但是主机访问HDM会却相反。

优势:设备偏向性减少对主机的依赖,使设备能够自主地进行资源分配和配置。这种架构可以提高系统的可扩展性和灵活性,设备可以更独立地进行协同工作和处理任务。

劣势:设备偏向性可能导致设备之间的协作和配置管理较为复杂,可能需要更多的设备间协议和通信。此外,对于特定系统需求的全局优化,可能需要更多的设备之间的协调和通信,增加了设计和实现的挑战。

**注意:**HDM是附属设备的内存,也就是HDM是挂载在设备端,而不是在主机端

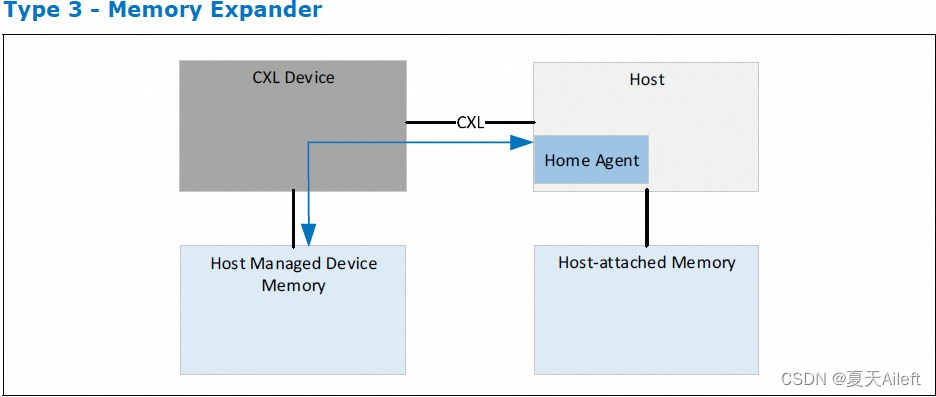

4.Type3 CXL设备

4.1 设备应用类型:

Type 3的典型应用是内存缓冲器,常用作内存带宽或者是容量的扩展。

Type 3 CXL设备支持CXL.io和CXL.mem协议。由于这些设备不是加速器,所以它们不会通过CXL.cache发出任何请求。该设备主要通过CXL.mem运行,为主机发送的请求提供服务。CXL.io协议主要用于设备发现、枚举、错误报告和管理。CXL.io协议允许设备用于其它特定于I/O的应用用途。

5.多逻辑设备(Multi Logical Device,MLD)

CXL 2.0仅支持Type 3的多逻辑组件。MLD组件最多可以将其资源划分为16个独立的逻辑设备(Logical Device,LD)。在CXL.io和CXL.mem协议中,每个逻辑设备都由逻辑设备标识符(LD-ID)标识。每个逻辑设备都作为Type 3设备运行,对虚拟层次结构(Virtual Hierarchy,VH)可见。LD-ID对访问VH的软件是透明的。MLD组件对于所有逻辑设备中的每个协议都有公共事务层和链路层。

MLD组件有一个为FM(Fabric Manager)保留的LD和最多16个可用于主机绑定的LD。FM拥有的LD(FMLD)允许FM跨LD配置资源分配,并管理与多个VCS(Virtual CXL Switch)共享的物理链路。

插播一句,VH是PCIe MR-IOV(Multiple Root I/O Virtualization)里面的一个概念。MR-IOV扩展了SR-IOV规范,允许PCIe设备在多个有独立PCI根的系统之间共享,这些系统通过基于PCIe转换器的拓扑结构与PCIe设备或者PCIe-PCI桥相接。每个VH(一个VH就是一个虚拟独立的SR-IOV设备)拥有独立的PCI Memory,IO,配置空间。

5.1 多逻辑设备和pcie 虚拟化区别和联系:

5.1.1 区别:

**范围:**MLD是CXL协议中的概念,而PCIe中的虚拟化是在PCIe标准中定义的。它们属于不同的协议和标准体系,并且在不同的领域和应用中发挥作用。

支持范围:MLD通常用于高性能计算和数据中心中,主要面向加速器和设备的虚拟化。而PCIe虚拟化广泛应用于服务器和桌面系统中,用于虚拟机和容器等多租户环境中的设备共享和隔离。

5.1.2联系:

**资源划分:**MLD和PCIe虚拟化都允许将一个物理设备划分为多个虚拟设备实例,每个实例都可以独立地配置、管理和使用资源。这样可以提高设备的利用率和灵活性,支持多任务和多租户的需求。

**虚拟设备驱动程序:**在MLD和PCIe虚拟化中,每个虚拟设备实例都需要有相应的驱动程序,用于与主机进行通信和操作。这些驱动程序负责虚拟设备实例的配置、命令传递和数据交互。

**隔离和保护:**MLD和PCIe虚拟化都涉及到对虚拟设备实例之间的隔离和保护。这是为了确保各个实例之间的操作互不干扰,确保安全性和稳定性。

5.2 MLD中如何做到各个实例间的隔离:

在CXL中,多逻辑设备(MLD)之间的隔离主要通过以下方式实现:

虚拟地址空间隔离:每个MLD被分配了自己的虚拟地址空间,使得每个实例在操作内存时互不干扰。这意味着每个MLD都有自己的独立内存映射,防止数据交叉干扰和冲突。

**DMA(Direct Memory Access)隔离:**DMA是一种直接内存访问技术,允许设备通过绕过主机CPU直接读写内存。在MLD中,每个实例具有独立的DMA引擎和DMA传输路径,以确保不同实例之间的DMA操作互不干扰。

**中断和事件隔离:**CXL允许每个MLD拥有独立的中断控制和事件处理机制。这使得每个实例可以接收和处理独立的中断和事件,而不会干扰其他实例的工作。

安全性和权限控制:CXL提供了一套安全性和权限控制机制,用于确保每个MLD实例之间的访问和操作受到严格的限制和控制。这包括访问控制列表、权限级别和访问权限掩码等

6.CXL设备扩展

CXL设备扩展限制只允许每个VH(Virtual Hierarchy)启用一个Type 1或Type 2设备。

文章详细介绍了CXL协议支持的三种设备类型,包括Type1(如网卡)的完全一致性缓存,Type2(如GPU)的额外内存连接,以及Type3(如内存缓冲器)的内存扩展。着重讨论了主机管理和设备偏好的一致性协议,以及多逻辑设备(MLD)在CXL中的应用和与PCIe虚拟化的对比。

文章详细介绍了CXL协议支持的三种设备类型,包括Type1(如网卡)的完全一致性缓存,Type2(如GPU)的额外内存连接,以及Type3(如内存缓冲器)的内存扩展。着重讨论了主机管理和设备偏好的一致性协议,以及多逻辑设备(MLD)在CXL中的应用和与PCIe虚拟化的对比。

1406

1406

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?