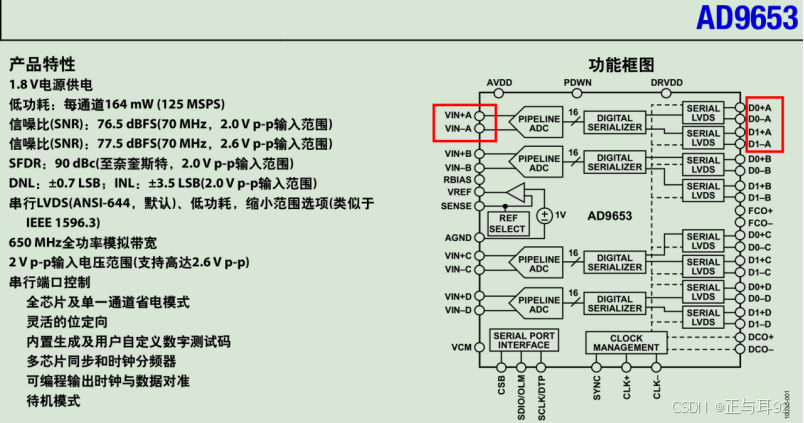

一、AD9653概述

AD9653是一款4通道、16 位、125 MSPS模数转换器(ADC) ,内置片内采样保持电路,专门针对低成本、低功耗、小尺寸和易用性而设计。AD9653是LVDS接口,AD9653和AD9656技术指标一致,但是AD9656是JESD204B接口。以下重点介绍AD9653.

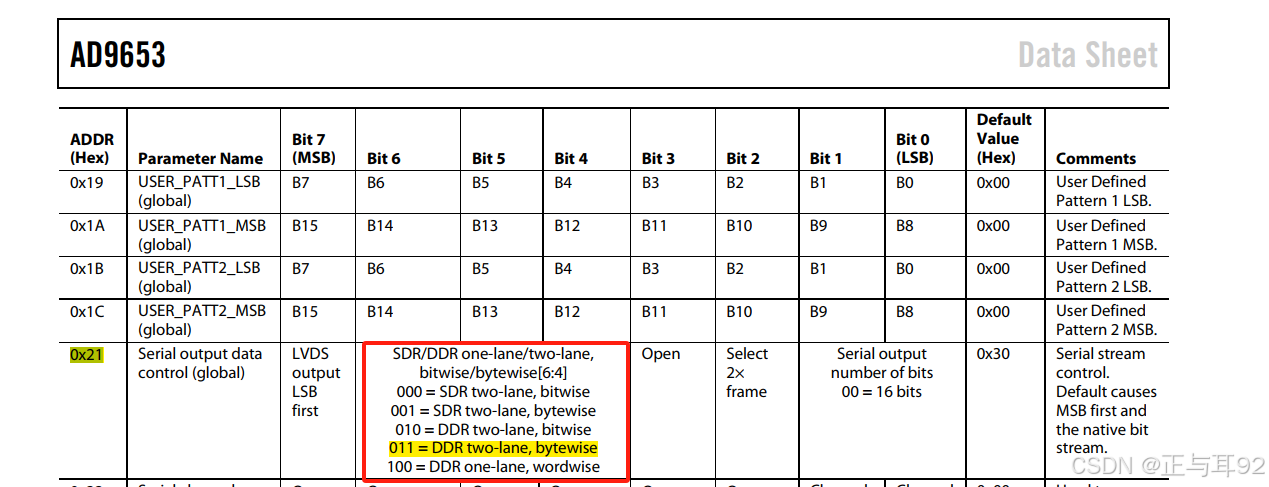

二、串行数据模式

AD9653有5种串行数据模式,实际应用中,5种都测了OK,现在以DDR-2 lane-bytewize为例

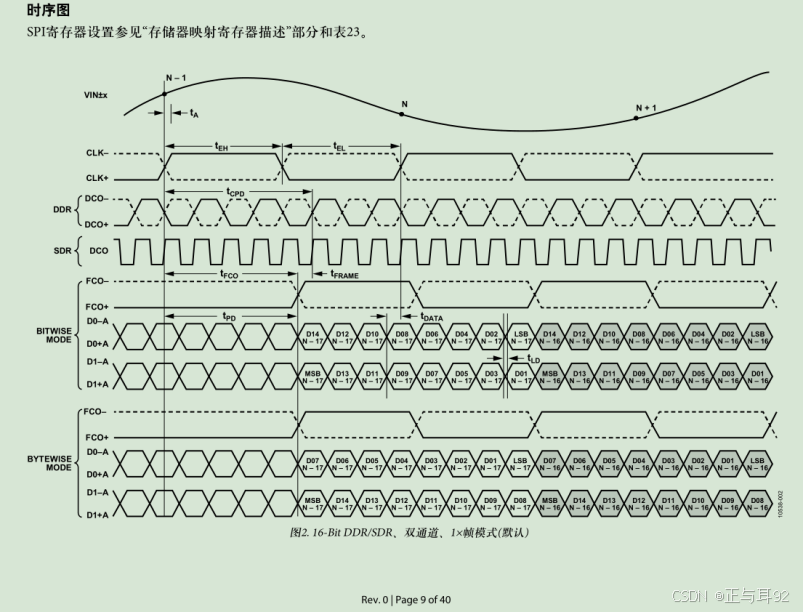

三、时序图

DDR-2 lane-bytewize的时序图,关注一下几点:

1.关注“位时钟”DCO+是在数据D0或D1的正中心,这是后续为什么要对“位时钟”进行自适应对齐的原因,对齐方法参考《一种基于片同步技术的高速ADC与FPGA互连方法_韩琦》;

2.关注DDR的比例8:1,意思是单次iserdese转换出8bit数据,DDR是双沿的,因此快时钟频率=4*慢时钟频率

3.关注FCO,因为FCO和数据DAT是严格对齐的,只要保证FCO和DAT的bitslip是一致的,那么DCO采集FCO稳定时,采集数据DAT同样是稳定的。其实FCO就是串行LVDS的同步码,在这里就是0xF0。

4.关注DAT的映射关系。比如当前采样点是16bit的S0,D1A是S0的高8bit;D0A是S0的低8bit。将D0A/DA1拼接在一起就还原了S0。

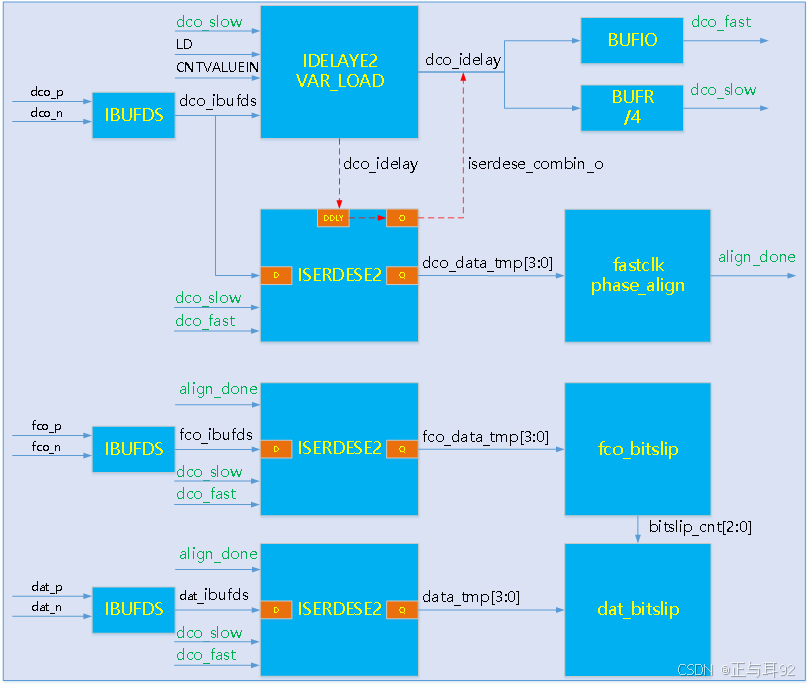

四、方案框图

熟悉了AD9653的基本功能和时序图后,设计代码的逻辑框图,直接上干货

五、写代码

根据方案框图就可以写代码了,调试时,要注意bitslip的用法,因为iserdese是每次上电转换是随机开始的,我们要用DCO去采集FCO时,判断0xF0去确定位置。

ISERDESE2有bitslip功能,可以自动移位,ISERDESE3没有这个功能,只能手动去实现bitslip功能了。

六、注意事项

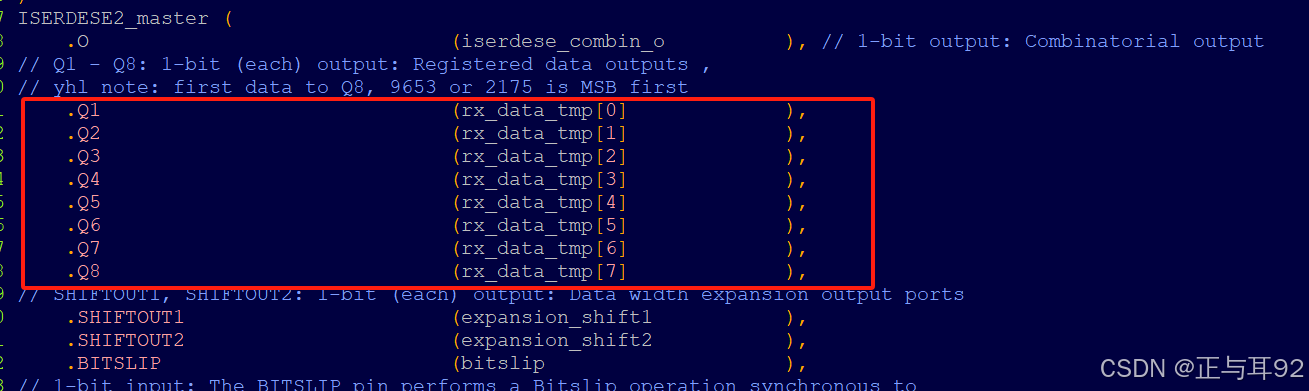

1.数据映射关系问题

ISERDESE2的串转并,先进来的bit是在Q8位,AD9361是高位在前,因此,并口数据可以这样写:

2.DCO对齐问题

根据上文提到的《一种基于片同步技术的高速ADC与FPGA互连方法_韩琦》文章去进行位时钟自动对齐,调试中,如果出现start_tap和end_tap相差3个以上, 就要注意DCO时钟是不是有问题,上升沿太缓了?时钟不稳定?DCO占空比没有使能?终端匹配电阻没有使能?方波信号好些。

3.同步对齐功能

AD9653调试同步,主要是看DCO时钟,同源基本没有问题,建议1分频,另外如果用到了DCO位时钟对齐,建议两个芯片反复配置,保证DCP的bitslip次数是一致的,这样每次上电,DCO采集DAT的相位就是一致的。

【FPGA】AD9653设计和调试总结

最新推荐文章于 2025-04-23 17:37:54 发布

1595

1595

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?