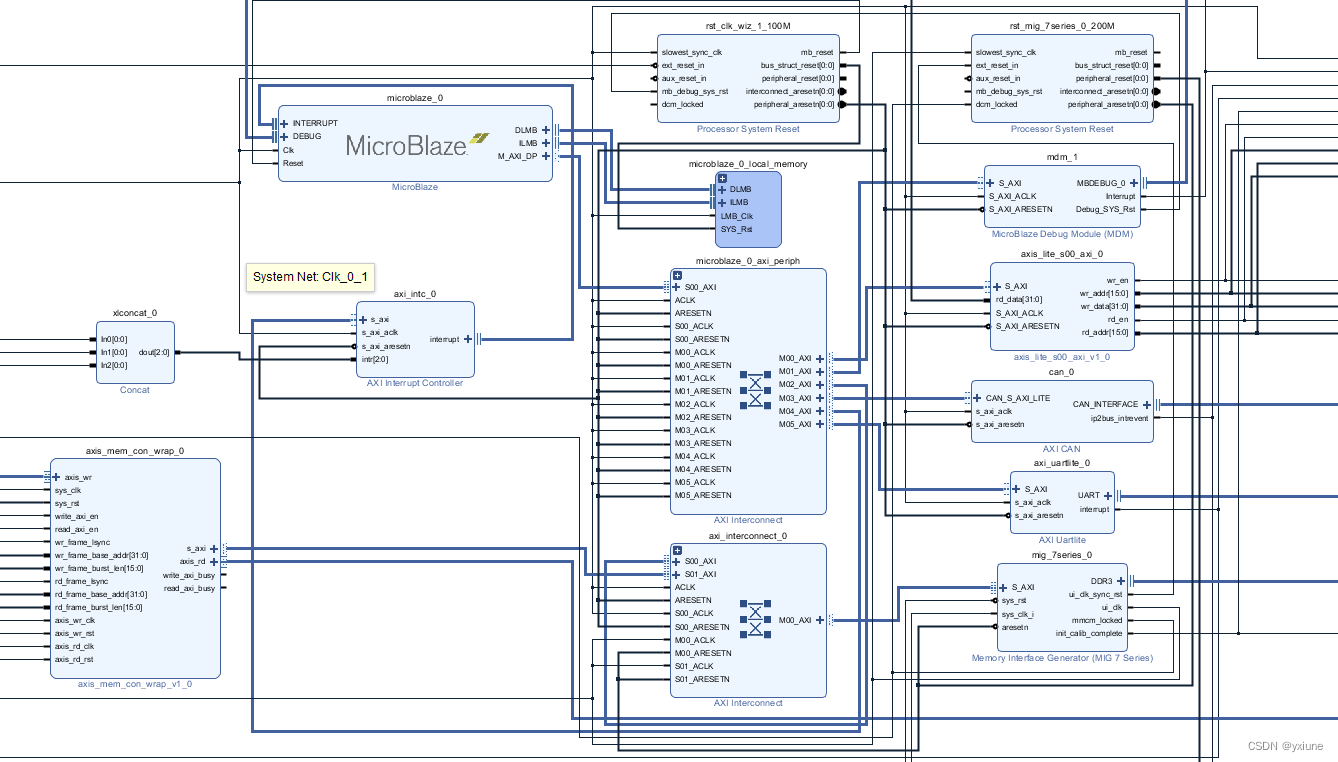

1. 系统搭建

系统主要包含:MicroBlaze软核处理器,Axi-Can控制器,Axi-lite-user用户通信接口,MIG DDR3控制器,中断控制器等。

设计使用Can接收上位机发送的在线设计程序;在软核中解析Can协议;将烧写程序写到DDR中;利用AXI-LITE用户通信接口,给PL端发送在线更新指令,PL实现将DDR中在线升级程序搬到Flash中。

2,软核程序实现

CAN接收数据协议主要在Can接收中断中实现;接收完下载数据后,通过完成标志下发在线更新指令;逻辑收到更新指令,搬运数据到Flash。

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

#include "xil_cache.h"

#include "xil_io.h"

#include "sleep.h"

#include "sys_intr.h"

#include "can_init.h"

#include "can_intr.h"

#define TEST_RX_ONLY

#define MAX_PKT_LEN 8

#define NUMBER_OF_TRANSFERS 20

#define TEST_START_VALUE 1

#define TX_BUFFER_BASE 0x85000000

#define USER_BASE_ADDR 0x45000000

static XCan Can;

static XIntc Intc;

int frame_cnt = 0;

int frame_length = 0;

int recv_frame_done = 0;

void init_intr_sys(void)

{

Init_Intr_System(&Intc);

Intc_Enable(&Intc,CAN_INTR_VEC_ID);

Intc_Start(&Intc);

Init_CanIntr(&Can, CAN_DEVICE_ID);

Can_Setup_IntrSystem(&Intc, &Can, CAN_INTR_VEC_ID);

Setup_Intr_Exception(&Intc);

}

int main(void)

{

// can_frame msg;

int i = 0;

// int frame_length = 0;

// int recv_frame_done = 0;

xil_printf("Can start\r\n");

init_intr_sys();

while(1)

{

if(recv_frame_done) {

xil_printf("frame_length=%d \r\n", frame_length);

Xil_Out32(USER_BASE_ADDR,0x1);

recv_frame_done = 0;

for(i=0;i<frame_length;i++)

{

xil_printf("%d,DDR0 = 0x%x; DDR1 = 0x%x\r\n", i,Xil_In32(TX_BUFFER_BASE+i*8),Xil_In32(TX_BUFFER_BASE+i*8+4));

}

i = 0;

}

}

}

void can_RecvHandler(void *CallBackRef)

{

XCan *CanPtr = (XCan *)CallBackRef;

u32 recv_data[2];

u32 RxFrame[XCAN_MAX_FRAME_SIZE_IN_WORDS] ={0};

XCan_Recv(CanPtr, RxFrame);

recv_data[0] = RxFrame[2];

recv_data[1] = RxFrame[3];

if(recv_data[0] == 0x5555AAAA && recv_data[1] == 0xAAAA5555){

frame_cnt = 0;

}

else if(recv_data[0] == 0xEEEEFFFF && recv_data[1] == 0xFFFFEEEE){

frame_length = frame_cnt;

recv_frame_done = 1;

frame_cnt=0;

}

else {

Xil_Out32(TX_BUFFER_BASE+frame_cnt*8,recv_data[0]);

Xil_Out32(TX_BUFFER_BASE+frame_cnt*8+4,recv_data[1]);

frame_cnt++;

}

}

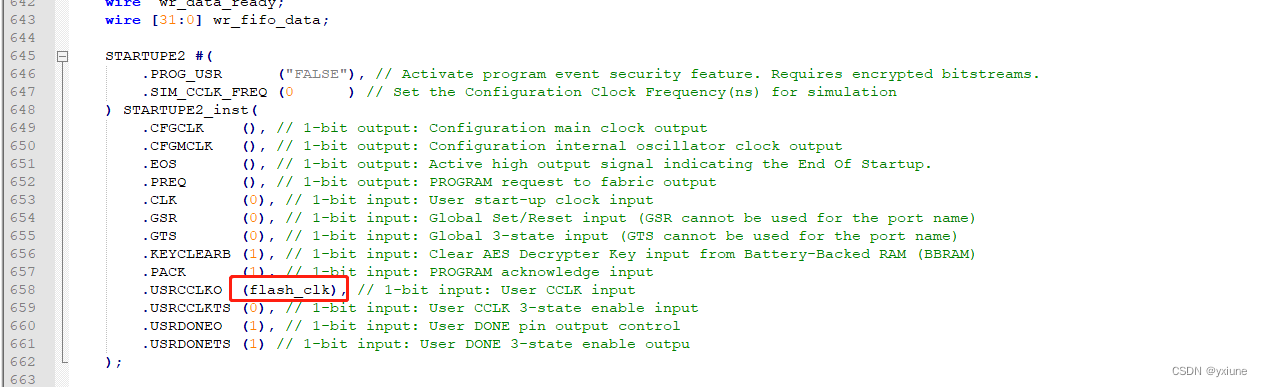

3.Flash通信

Flash通信可见:七、基于FPGA的Flash控制器设计_fpga flash读写_yxiune的博客-CSDN博客

其中Flash clk管脚配置方法:通过原语STARTUPE2

3440

3440

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?