PLC_博图系列☞F_TRIG:检测信号下降沿

文章目录

- PLC_博图系列☞F_TRIG:检测信号下降沿

- 背景介绍

- F_TRIG: 检测信号下降沿

- 说明

- 参数

- 示例

关键字:

PLC、

西门子、

博图、

Siemens 、

F_TRIG

背景介绍

这是一篇关于

PLC编程的文章,特别是关于西门子的博图软件。我并不是专业的PLC编程人员,也不懂电路,所以如果你希望从这里学习PLC编程技术,可能会有些失望。然而,因为工作需要,我开始了解PLC编程,特别是西门子的博图软件,并记录了这些经验。随着我国工业4.0的推进,相信会有更多的人从事类似的工作。如果这篇文章能对你有所帮助,欢迎点赞和关注我❥(^_-)。

F_TRIG: 检测信号下降沿

说明

使用“检测信号下降沿”指令,可以检测输入 CLK 的从“1”到“0”的状态变化。该指令将输入 CLK 的当前值与保存在指定实例中的上次查询(边沿存储位)的状态进行比较。如果该指令检测到输入 CLK 的状态从“1”变成了“0”,就会在输出 Q 中生成一个信号下降沿,即输出的值将在一个循环周期内为 TRUE 或“1”。

在其它任何情况下,该指令输出的信号状态均为“0”。

参数

下表列出了“检测信号上升沿”指令的参数:

参数 | 声明 | 数据类型 | 存储区 | 存储区 | 说明 |

S7-1200 | S7-1500 | ||||

EN | Input | BOOL | I、Q、M、D、L | I、Q、M、D、L、T、C | 使能输入 |

ENO | Output | BOOL | I、Q、M、D、L | I、Q、M、D、L | 使能输出 |

CLK | Input | BOOL | I、Q、M、D、L 或常数 | I、Q、M、D、L、T、C 或常数 | 到达信号,将查询该信号的边沿。 |

Q | Output | BOOL | I、Q、M、D、L | I、Q、M、D、L | 边沿检测的结果 |

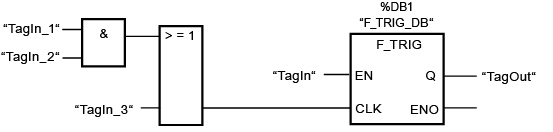

示例

以下示例说明了该指令的工作原理:

输入 CLK 中变量的上一个状态存储在“F_TRIG_DB”变量中。如果在操作数“TagIn_1”和“TagIn_2”或在操作数“TagIn_3”中检测到信号状态从“1”变为“0”,则输出“TagOut_Q”的信号状态在一个循环周期内为“1”。

**注:**以上部分内容来之博图V16帮助文档。

7838

7838

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?