题: 试分析计数器电路的分频比(Y与CLK的频率之比).

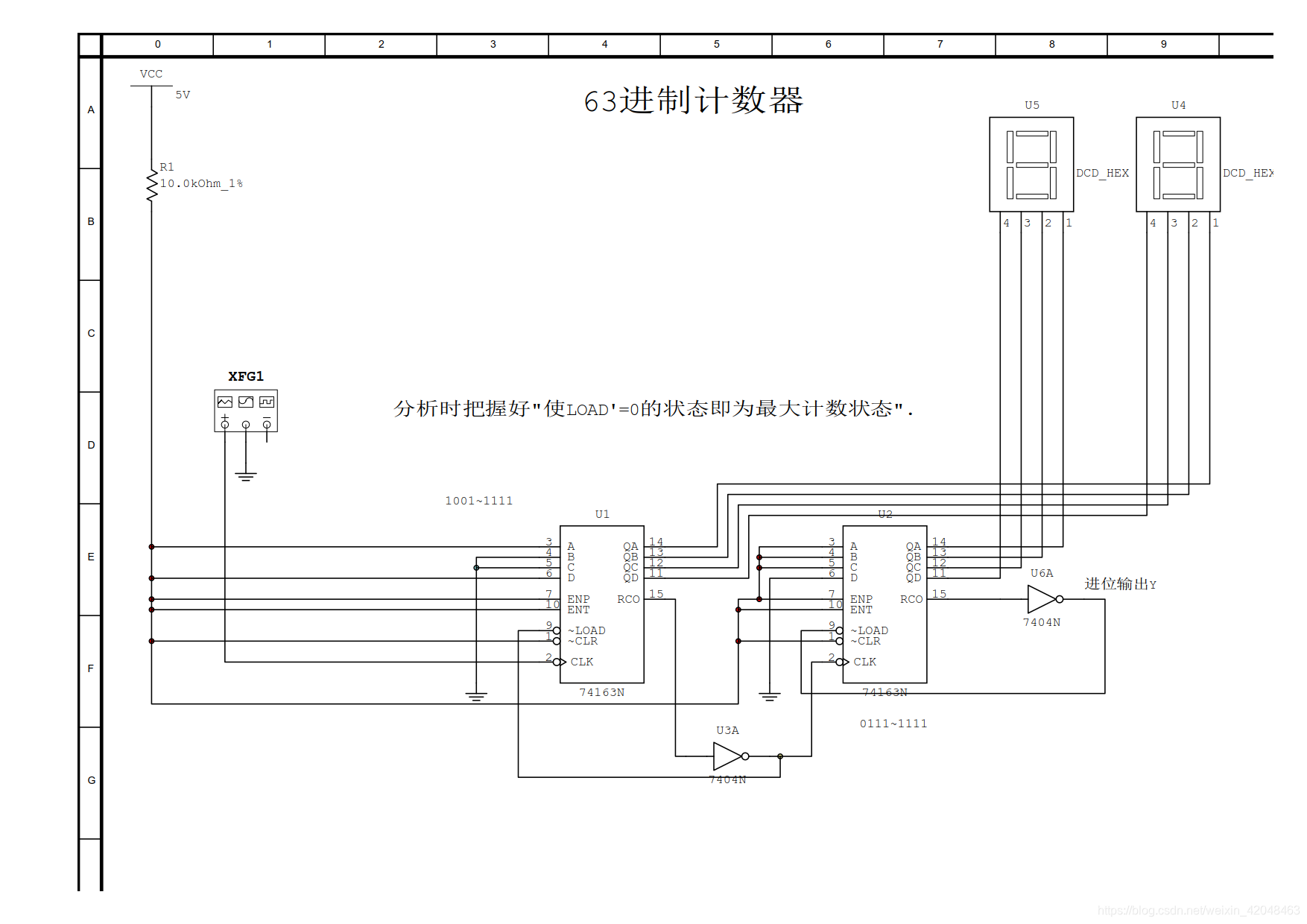

分析: 首先要把握好一条准则"对于加法计数器芯片(74160、74163)来说, 使LOAD'=0的状态即为电路计数的最大状态".

低位74163与高位74163的最大计数状态均为1111B, 低位74163的最小有效计数状态为1001B, 高位74163的最小有效计数状态为0111B.

电路中有两种情况需要仔细分析: ①如电路状态到达7FH后, 下一步如何变化, ②电路状态到达FFH后, 下一步如何变化.

①电路状态到达7FH后, 低位74163的RCO=1, 则其LOAD'=RCO'=0, 当下一系统CLK信号到来时, 低位74163按照DCBA的取值被置为1001B=9H, 其RCO引脚通过非门后

产生一个上升沿脉冲, 即高位74163此时获得一个CLK上升沿脉冲, 则高位74163计数一次, 其状态由7变为8, 现在电路的状态变为89H.

②电路状态到达FFH后, 低位74163和高位74163的RCO均为1, 则它们的LOAD'均为0, 当下一系统CLK信号到来时, 低位74163按照DCBA的取值被置为1001B=9H, 其

RCO引脚通过非门产生一个上升沿脉冲, 即高位74163此时获得一个CLK上升沿脉冲. 高位74163的LOAD'此时=0, 则高位74163按照DCBA的取值被置为0111B=7H, 现在电路

的状态变为79H. 此时低位74163和高位74163的LOAD'均=1, 在下一系统CLK上升沿到来时, 计数器正常做+1计数.

由于低位74163共有7个有效计数状态, 高位74163共有9个有效计数状态, 则该电路为63进制计数器, 则分频比为1:63.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?