问题背景

实现一个以太网数据发送的AD采样的数据,但是我仅仅修改ip地址就会导致其输出的udp包出现大量的误码的情况

实际上,修改的东西是非常有限的,而且目前遇到的很多的问题都是这种仅仅修改了非常小的东西,就会出现类似这样的意料之外的事情

作为一个fpga 的新手,我觉得也是时候了解一下,实际硬件综合后的结果是什么样的了。

问题探索思路

对于同一个功能观察一下硬件电路实际综合后出来的结果是什么,进行实际的对比。

可用的参考资料如下:

亚稳态相关:https://zhuanlan.zhihu.com/p/148572372

本人采用的是vivado2018 的版本。

实验探索

可用board 1

不可用board 2

学到知识总结

默认未接的线连接的是低电平

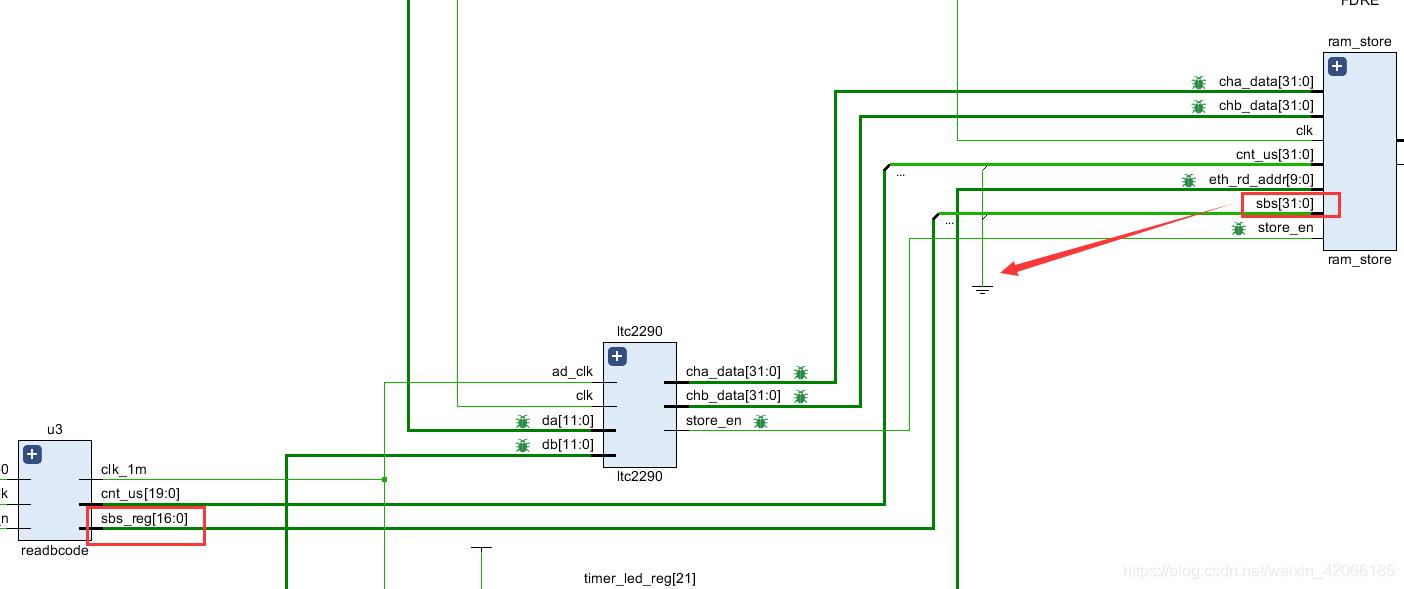

如下图所示的,其为17长度,但是实际上,最后所有的高位都会接入低电平

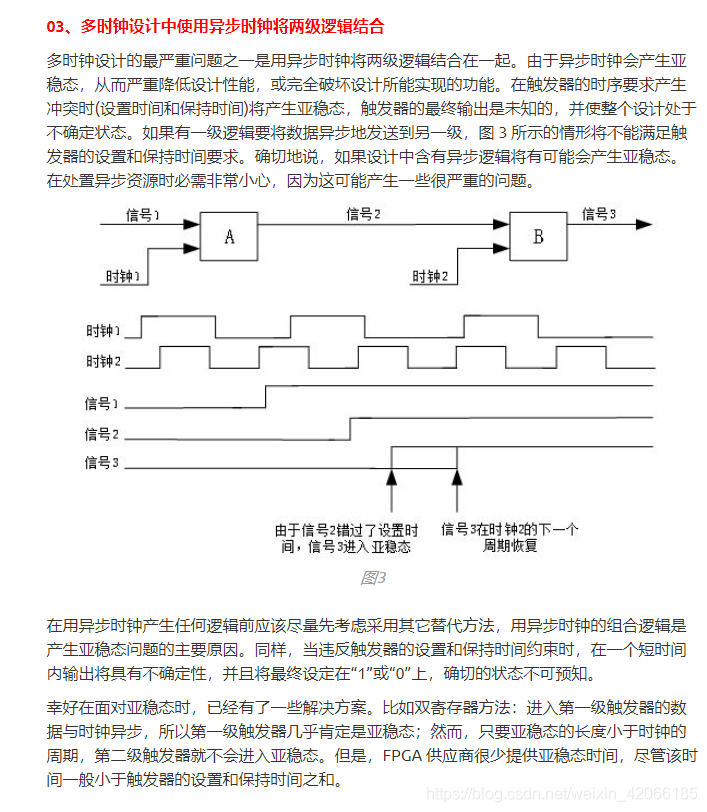

多时钟域导致亚稳态的问题剖析

布局布线后,数据扇出太多,导致数据出错

**

**

欢迎关注我的微信公众号

嵌入式硬件、软件的学习文章、个人感悟、学习交流分享,欢迎关注分享,共同进步。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?