文章目录

概要

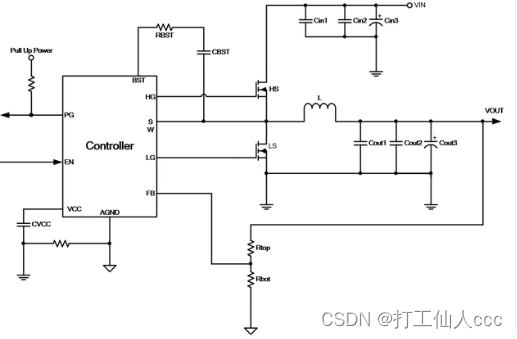

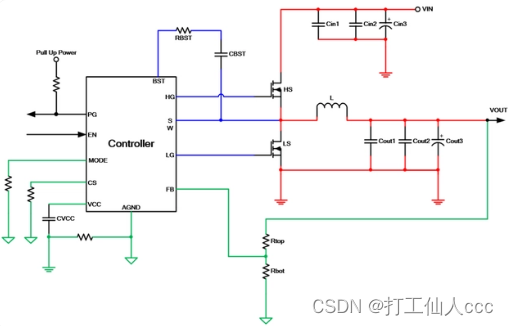

Buck电路(Controller)主要是由几个部分组成:1、控制器及外围线路;2、功率MOS;3、功率电感;4、输入/输出滤波电容

Buck电路(Converter)相比Controller主要集成了功率MOS;

如果电流在1A~10A之间,一般选择集成MOSFET的稳压器;具体情况集体分析。

控制器及外围线路设计

提示:多相控制器通过并联多个开关电源阶段(相)来提高总体输出电流,每个相位都有自己的控制回路和开关元件。

1、控制器分为单相和多相,根据负载大小选择相数,相数少可能会造成功率器件温度过高导致损坏,相数太多造成浪费。输出电流30A以下选择单相控制器。

2、控制器协议差异,常见的协议有I2C或PMBUS(国产平台)、SVID(Intel平台),SVI3(AMD平台),PWMVID(NVIDIA平台)等。

3、控制器分为数字和模拟。数字控制器外围简单是未来发展趋势。

技术名词解释

例如:

- VCC

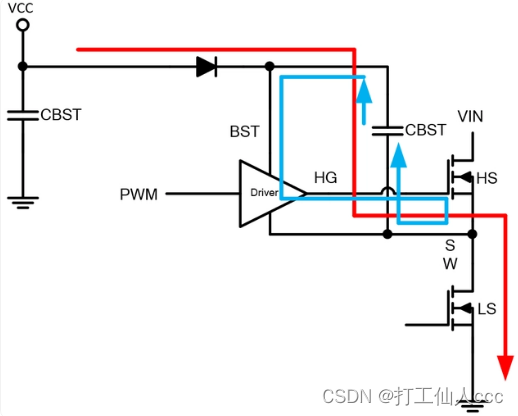

控制器内部逻辑和驱动电路的供电电源 - CBST

自举电容,主要是维持高边MOS的导通

LS导通时,SW的电压降为0,VCC通过红色路径给CBST充电;

HS导通时,HG变高的过程中HS开始导通,SW电压开始升高,电容电压不能突变,HS的Vgs电压差大于等于电容两端电压。 - PG

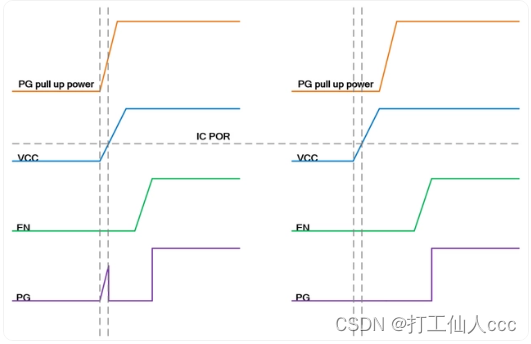

Power Good信号在IC内部Open Drain,需要外部上拉。值得注意的是上拉电源的上电时间,需要在VCC上电之后,避免上拉电源上电时IC无法控制,导致PG出现毛刺。下图分别是PG上拉电源位于VCC之前和之后上电,PG的波形。

功率MOS

(1)VDS耐压

Buck实际工作时DS电压小于VDS,防止MOS实际工作时被击穿;实际工作时MOS的波形会有振铃,VDS一般选择比输入电压大10V。

(2)MOS的Id电流

选型时MOS的Id电流小于输出的峰值电流,MOS的datasheet标明的电流是基于Rdson和最大功率Pd计算得来的,没有考虑开关损耗;因此不能直接和Irms值比较,需要考虑MOS的整体损耗来确定选型。

(3)Rdson和Qg

原则上管选择Qg更小的,下管选择Rdson更小的。如果buck的占空比较大(>50%),上管的导通损耗也不容忽视,需要Qg和Rdson都小。

(4)MOS的驱动信号增加串联电阻

通过调节这个电阻改变MOS的开关速度;影响开关时的振铃也影响效率。

功率电感

提示:功率电感则主要从电感值和电流两个方面来选型

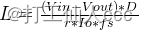

(1)Buck电路的感值可通过如下公式进行计算:

电感感值计算公式:

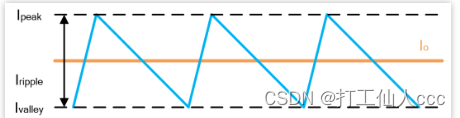

r是电流纹波率,一般选择0.3-0.5。电感值会影响输出纹波率和动态响应;实际应用时可以根据测试情况调整。

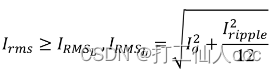

(2)电感电流主要分为饱和电流Isat和温升电流Irms;

选择电感时饱和电流Isat要大于Ipeak;避免电感饱和造成MOS和电感损坏。

温升电流考虑的是电感的损耗和温度,一般选择电感时Irms大于Io;

(3)对于CPU和GPU的核心电源,在选择电感时还需要注意DCR的精度,这类电源一般都会用电感DCR做电流检测,为了保证电流检测的一致性,电感的DCR精度尽量选择±5%以内。

输入和输出电容

输入和输出的电容主要作用是滤除电源噪声,并且在电源跳变时提供和吸收能量,使电压保持稳定。

(1)为了避免被击穿,电容降额使用,具体降额看设计要求。

(2)电容的容值主要影响滤波和稳压效果;大电容虑低频,小电容虑高频,根本的原因在于SFR(自谐振频率)值不同。电感的阻抗与频率成正比,电容的阻抗与频率成反比。

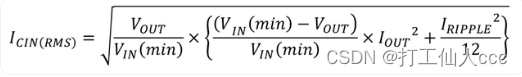

(3)电容纹波电流有效值,主要是选择输入电容时需要注意的(特别是电解电容),如果实际的输入电容纹波电流有效值超过电容的额定值,会造成电容失效。

(4)电容的ESR主要影响电源纹波,同时也跟电容的纹波电流有效值相关,一般情况下,ESR越小的电容,纹波电流有效值越大。

Layout

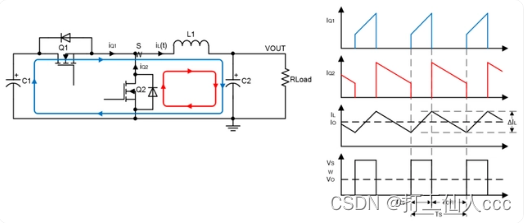

开关电路可以分为以下三个部分:

(1)红色部分为功率转换的路径,电流和电压变化快,且幅度大,走线宽度要足够,同时需要跟其他信号保持安全距离,避免干扰;

(2)蓝色部分为驱动信号,平均电流不大,但是瞬间电流较大,且电压和电流变化极快,会造成强烈的干扰,layout时要非常小心;

(3)绿色部分是反馈信号和IC的功能设置,非常敏感,需要避开干扰源。

功率转换模块Layout设计

功率转换模块包括MOS、电感、输出电容等

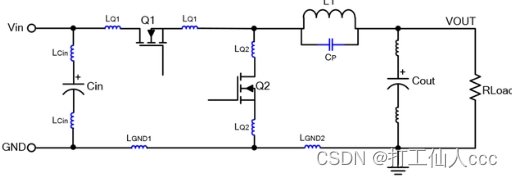

可以看出输入电容和MOS电流变化剧烈,电感和MOS组成的区域SW电压变化剧烈。功率转换模块等效模型,图中标出了寄生电感和电容,layout设计要求:尽可能减小寄生电感和寄生电容。

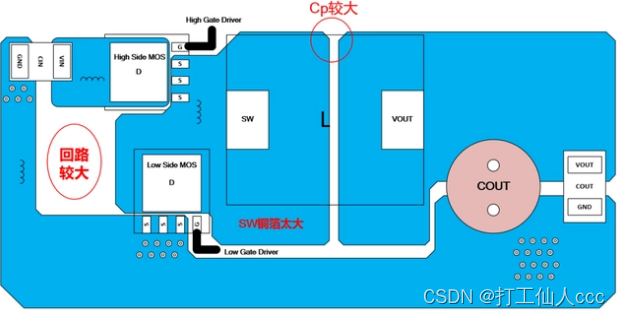

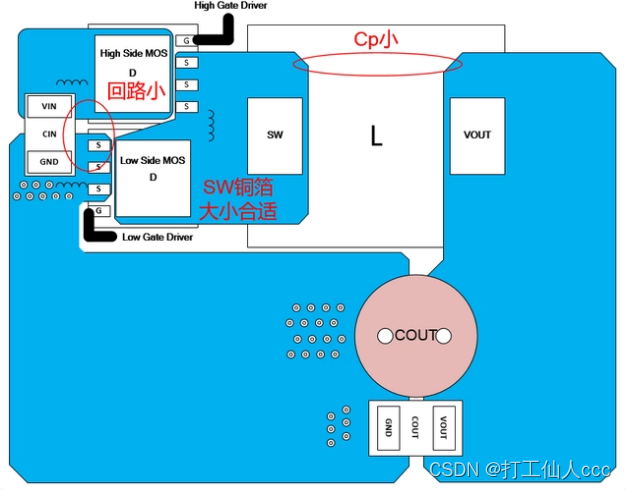

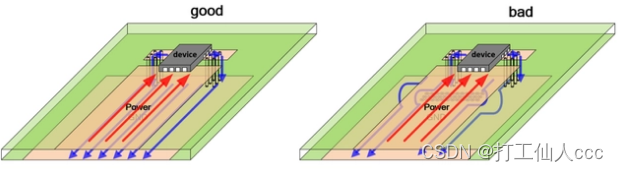

(1)下图是buck电路功率转换模块layout较差的例子,输入电容跟MOS形成的回路较大,产生较大的寄生电感,容易形成严重的高频振荡;电感两个PIN的铜箔距离近,并且耦合面积大,产生的寄生电容CP比较大,影响电感性能;SW的区域太大,容易对外辐射,干扰周边电路。

(2)buck电路功率转换模块layout较好的例子如下,输入电容和MOS形成的回路小,寄生电感小;电感两个PIN的距离远,寄生电容CP小;SW区域大小合适,不易造成严重干扰。

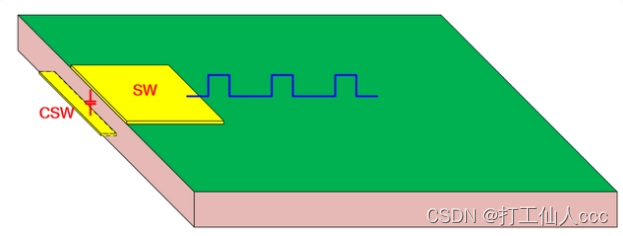

(3)SW的铜箔跟相邻层的铜箔会形成一个寄生电容CSW,SW的电压剧烈变化,通过这个寄生电容对相邻层造成强烈的干扰,因此SW下方不能有其他信号的走线,需要用地层或稳定的电源层隔开。

(4)功率地应尽量完整,避免被其他信号或过孔打断,影响电流回流路径的完整性。

驱动信号Layout设计

(1)驱动信号是控制MOS开关,电压变化快且瞬间电流大。因此走线要粗而短,走线宽度要求20mil以上。

(2)驱动信号本身干扰极强,容易影响其他信号,因此不能跟其他信号平行或重叠,至少要有地层隔离。

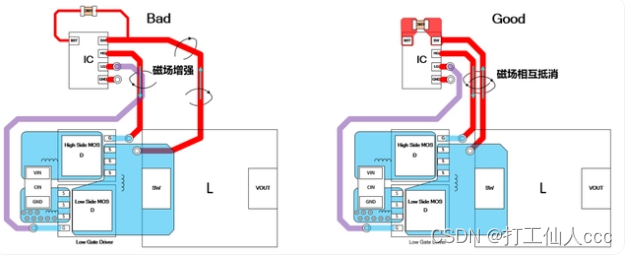

(3)上管和下管的驱动信号不能平行的走线,也不能交叉(相邻层,没有地层隔离的情况下),以免互相干扰引起MOS误动作,导致MOS烧坏。

(4)驱动信号的电流回路面积尽量小,减少电磁干扰

(5)BST电容尽量靠近PIN脚摆放,并用短而粗的线连接,减小回路面积

反馈信号及IC功能信号Layout设计

(1)反馈信号很敏感,所以layout时远离干扰源,例如高压电源层,驱动信号,开关节点(SW),电感,I2C信号等电压电流变化大的信号。

(2)成对的反馈信号,需要按照差分走线,线宽7~10mil,间距6mil,与其他信号的距离要15mil以上,同层噪声源距离20mil以上,且不可在相邻层跟噪声源重叠(相邻层距离也需要20mil以上)。

(3)电流检测信号从电感或者精密电阻两端拉线时,要注意采样的位置,需要从焊盘中间拉线或者焊盘中心打孔后走线。

(4)反馈信号尽量参考地层,即相邻层是完整的地层,或者参考低压且稳定的电源层,避免被干扰。

(5)IC功能设置的电阻电容,例如mode,OCP设置电阻,软启动电容等器件,靠近IC的PIN脚摆放,且GND与IC的AGND连在一起,如果没有AGND,则单独打孔连接到完整的地层,避免跟功率器件的地连在一起。

(6)IC如果有单独的AGND,需要先连在一起,然后通过单点接到地层,一般是通过电阻或short pad接到VCC电容的GND;VCC电容要尽可能靠近IC的PIN脚摆放。

控制器整体布局

控制器是控制整个buck电路工作的核心,因此需要摆放在相对干净的位置,远离噪声源,例如功率电感,开关节点,驱动信号,高压电源层,功率器件地层等。

一般来说,控制器可以摆放在离功率器件较远的位置,只要控制信号和检测信号注意避开干扰源即可,但是对于集成MOS驱动的控制器,则需要靠近MOS摆放,避免驱动信号走线过长。

控制器尽量参考完整的地层,不要参考输入电源层和负载动态变化大的电源,例如12V输入,CPU或GPU核心电源层。

Buck电路原理图设计

控制器根据电流需求选择合适的相数,以及满足输入输出电压范围要求

VCC,AGND这些PIN脚的外围电路需要按照控制器要求进行设计

Power good上拉电源需要在VCC之后上电

MOS选型,上管选择Qg小的型号,下管选择Rdson小的型号

电感的饱和电流和温升电流要大于实际的峰值电流和平均电流,对于DCR做电流检测的,需要选择DCR精度在±5%以内的电感

输入输出电容需要确保耐压满足要求,可选择不同类型的电容混搭,输入电容还需要注意纹波电流有效值

Buck电路layout设计

功率器件的电流回路面积尽量小,电感两个PIN的距离尽量远,SW区域下方不要有其他信号走线

驱动信号走线尽量短而粗,并且跟其他信号保持距离,避免干扰到其他信号

反馈信号需要差分走线,并避开干扰源

IC功能设置的器件靠近对应的PIN脚摆放

AGND通过单点接到GND

VCC电容尽可能靠近IC PIN脚摆放

控制器放在环境噪声小的位置,参考完整的地层

4936

4936

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?