概念总结:

提示:个人总结观点。

Pixel&Tunnel

在MAX96714/F/R系列芯片的数据手册中,"HIM"(High Immunity Mode)通常指的是一种高抗扰模式,而"Pixel"和"Tunnel"模式是指GMSL2链路中数据传输的两种不同模式。以下是这两种模式的差异:

-

Pixel模式:

- Pixel模式主要用于传输图像数据,它将接收到的MIPI CSI-2数据包在串行器的CSI-2输入接口处解包。

- CSI-2数据包头部的ECC(错误校正码)会在串行器输入端进行检查和移除,同样,数据包尾部的CRC(循环冗余校验)也会进行检查和移除。

- Pixel模式下,视频线路像素数据和视频路由信息(如数据类型和虚拟通道)在CSI-2接口处接收和提取,然后由串行器的调度器进行打包和封装,使用GMSL协议进行数据传输。

- Pixel模式适用于需要对视频数据进行解包和处理的应用。

-

Tunnel模式:

- Tunnel模式则提供了端到端的数据完整性,它允许将MIPI CSI-2接口接收到的数据原封不动地传输到GMSL链路上。

- 在Tunnel模式下,接收到的CSI-2 ECC字节和CRC字节在串行器输入端进行检查,然后与路由和像素数据一起作为字节流传输。

- 数据流被分割成较小的数据包,并使用GMSL2协议进行封装。串行器为每个视频线路的数据添加线路CRC,以保护GMSL通道上的传输。

- 与Pixel模式不同,Tunnel模式不支持对视频数据进行处理,如添加水印或进行有损数据压缩,因为Tunnel模式要求从串行器输入端接收的数据与解串器输出端的数据完全一致。

HIM(如果是指High Immunity Mode)可能是在Tunnel模式下提供的一种增强的抗干扰特性,以确保数据在链路上的稳定传输,特别是在面对电磁干扰或其他可能导致数据传输错误的环境中。

总结来说,Pixel模式适用于需要对视频数据进行解包和处理的场景,而Tunnel模式则适用于需要保持数据完整性和一致性的应用,它确保了从输入到输出的数据保持不变。HIM可能是Tunnel模式下的一个额外特性,用于提高数据传输的抗干扰能力。

LMN1和LMN0的作用

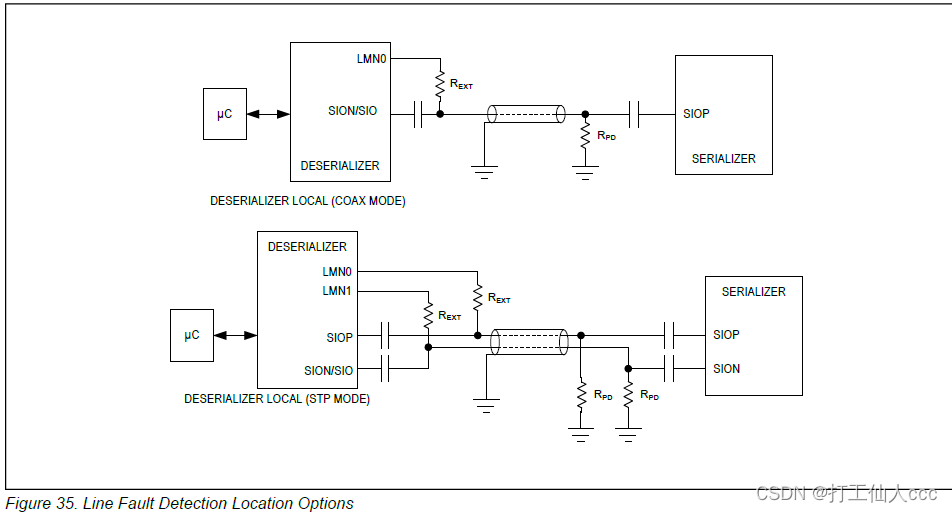

在MAX96714/F/R系列芯片的数据手册中,LMN0和LMN1是与线路故障检测功能相关的引脚。这些引脚的作用如下:

-

线路故障监测:

LMN0和LMN1引脚用于监测连接到GMSL(Gigabit Multimedia Serial Link)链路的电缆的状态。它们可以检测开路、短路到电池、短路到地和线间短路等故障情况。 -

线路故障检测配置:

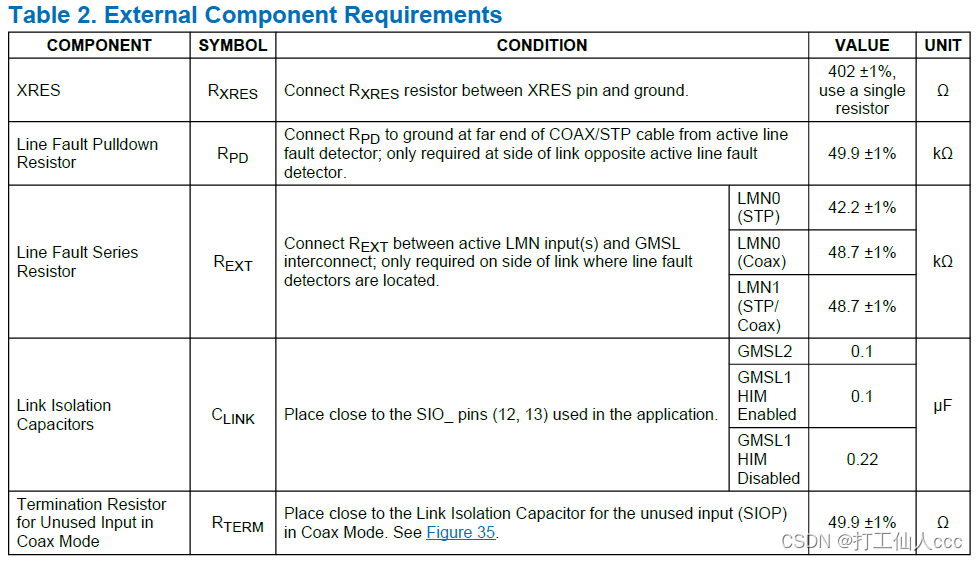

在使用线路故障检测功能时,需要在链路的两端正确配置这些引脚。LMN0和LMN1通常与外部电阻(如REXT和RPD)配合使用,以实现线路故障的检测。 -

线路故障检测模式:

数据手册中提到了两种线路故障检测配置模式:本地侧串行器配置(Local-Side Serializer Configuration)和本地侧解串器配置(Local-Side Deserializer Configuration)。这些配置通常用于显示链路和相机链路,但也可以用于任何设备串行链路系统。 -

线路故障检测的限制:

线路故障监测功能不能与通过同轴供电(Power-over-Coax, PoC)或交流耦合地面应用一起使用。 -

线路故障检测的激活和状态读取:

线路故障监测默认是禁用的,可以通过寄存器进行配置,其状态可以通过INTR2/3和FAULT_STAT寄存器读取。 -

外部电阻器:

为了使线路故障检测功能正常工作,需要在LMN0和LMN1引脚上连接适当的外部电阻器。这些电阻器的值在数据手册的“外部组件要求”部分有详细说明。 -

错误和事件状态指示:

LMN0和LMN1的状态可以通过ERRB引脚报告,该引脚是一个多功能的error-reporting和interrupt status输出。 -

线路故障检测的实现:

线路故障检测的具体实现和配置细节可以在GMSL用户指南中找到,或者联系工厂以获取更多指导。

总结来说,LMN0和LMN1引脚在MAX96714/F/R系列芯片中用于提供线路故障检测功能,这有助于确保系统的可靠性和安全性,特别是在关键应用中,如汽车安全系统。通过这些引脚,系统能够监测和响应链路中的物理层故障

故障检测

-

Line Fault Detection: GMSL2 Deserializer包括一个线路故障检测电路,可以检测并报告开路、短路到电池、短路到地和线间短路。线路故障监控器默认是禁用的,可以通过寄存器配置启用,并通过INTR2/3和FAULT_STAT读取状态。

-

Error and Fault Condition Monitoring: MAX96714/F/R系列设备有一个多功能的错误报告和中断状态输出引脚ERRB,它由各种错误和事件状态指示器的逻辑或驱动。每个能够驱动ERRB的错误和事件都有一个状态标志寄存器。

-

Power Supplies Information, and Overvoltage and Undervoltage: 设备提供全面的电源供应诊断功能,包括对所有供电电压(除VDDIO外)的过电压检测。

-

Eye-Opening Monitor (EOM): EOM允许GMSL2部件在活动链路上监控链路余量,并在低于可接受水平时生成中断。如果链路余量下降,EOM可以触发中断或重置。

-

Functional Safety Features: 包括多个安全特性,如POST(电源上电自检),LBIST(逻辑内置自测试),MBIST(内存内置自测试),以及各种CRC(循环冗余校验)功能。

-

Register Map: 提供了寄存器映射的信息,可以通过读取和写入这些寄存器来进行故障检测和状态监控。

-

Spread Spectrum: 可以用于减少设备发出的电磁干扰。

-

MIPI PHY Registers: 提供了MIPI物理层的配置和状态寄存器,可以用来检测和配置MIPI接口的状态。

-

GPIO Configuration: 通用输入输出(GPIO)引脚可以用来进行额外的故障检测和报告。

-

Line Fault/Short Reporting and CRC Reporting: 提供了线路故障/短路报告和CRC报告的功能。

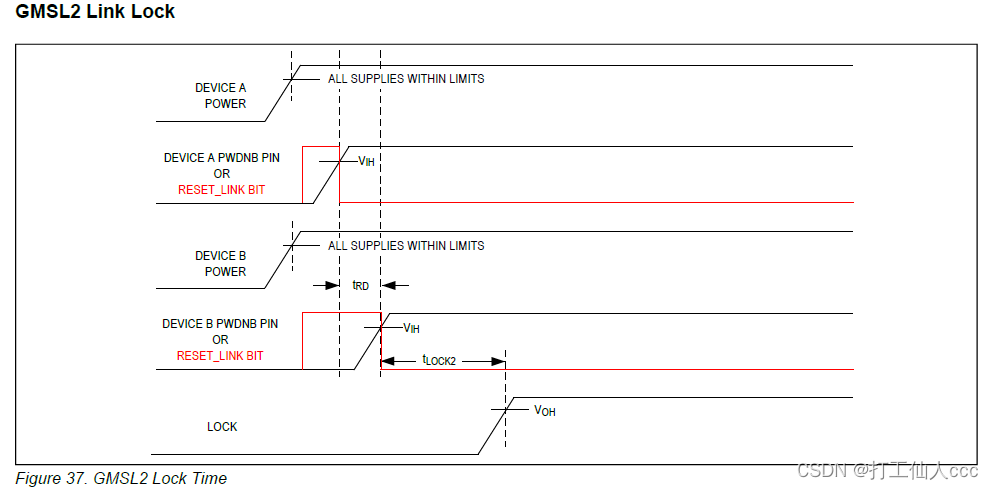

GMSL2链接锁定(Lock)的过程

1、GMSL2 Link Lock - 设备上的GMSL2链接使用晶体作为参考时钟,因此不需要有效的视频输入(PCLK)即可锁定GMSL2链接。锁定过程是在设备上电或从RESET_LINK状态恢复操作后自动进行的,表明电缆已插入并且系统正在运行

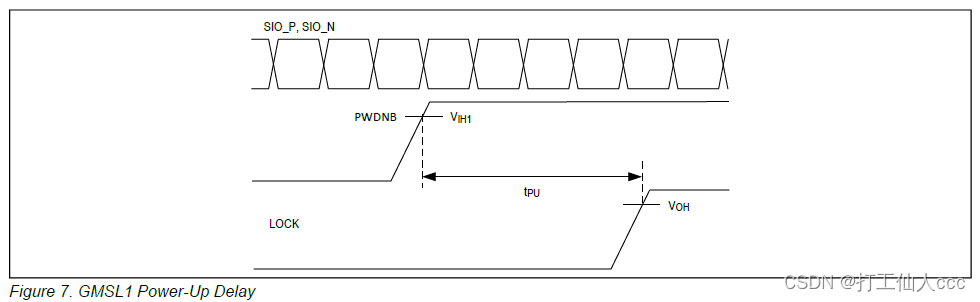

2、Lock Sequence - 锁定序列由释放PWDNB引脚或任一设备中的RESET_LINK位来启动。锁定时间是从释放PWDNB或RESET_LINK到锁定位被断言的时间。

3、包括PWDNB/RESET_LINK状态在两个设备上必须有重叠,以及在锁定过程中之前,两个设备都必须处于PWDNB/RESET_LINK模式。如果使用RESET_LINK来启动锁定,则假定PWDNB在上电后为高(正常操作)。如果使用PWDNB来启动锁定,则假定RESET_LINK在上电后为低(正常操作)。

4、Link and Video Lock - 视频锁定表明解串器正在接收有效的视频数据。在GMSL2链接锁定后,解串器视频输出PLL开始其锁定序列。

中断触发

关于中断触发(INT)的过程,主要涉及错误和事件状态指示器,这些指示器可以通过ERRB引脚报告。以下是与中断触发相关的关键点:

-

ERRB Pin - 这是一个多功能的错误报告和中断状态输出引脚。它由各种错误和事件状态指示器的逻辑或(OR)驱动。

-

Interrupt Enable Registers - 例如INTR0 (0x18), INTR2 (0x1A), INTR3 (0x1B), INTR4 (0x1C), INTR5 (0x1D), INTR6 (0x1E), INTR7 (0x1F)等寄存器,用于启用和配置特定的中断条件。

-

Error and Fault Status Registers - 例如INTR3 (0x1B), INTR5 (0x1D), INTR6 (0x1E), INTR7 (0x1F)等寄存器,包含用于报告特定错误和事件状态的标志位。

-

Interrupt Trigger Conditions - 中断触发条件可能包括但不限于:

- 线路故障(Line Fault)

- 电源电压异常(Overvoltage or Undervoltage)

- 帧同步错误(Frame Sync Error)

- 数据包CRC错误(Packet CRC Error)

- 视频像素CRC错误(Video Pixel CRC Error)

- 眼图监测错误(Eye-Opening Monitor Error)

-

Masking Interrupts - 可以通过寄存器设置来屏蔽(Disable)或启用(Enable)特定中断条件的报告。

-

Status Flag Clearing - 一些状态标志位在读取时会自动清除(Clear on Read),这通常用于清除中断状态。

-

Interrupt Assertion - 当特定的错误或事件状态被检测到,并且对应的中断使能寄存器被设置为启用状态时,ERRB引脚将被拉低,从而触发中断。

-

Automatic Reset - 某些中断条件可能会触发自动重置(Auto Reset),例如在ERRB被断言后,如果设置了自动重置使能(AUTO_ERR_RST_EN)。

-

Error and Fault Reporting - 通过ERRB引脚报告的错误和故障可以通过读取相应的状态寄存器来确定具体的错误类型。

-

Configuration - 为了使中断系统正常工作,需要正确配置中断使能寄存器和状态寄存器,以及任何相关的阈值或行为设置。

中断触发的具体过程通常涉及以下步骤:

- 配置中断使能寄存器以启用特定中断源。

- 系统运行中出现中断触发条件,如检测到线路故障或电源异常。

- 对应的状态寄存器中的旗标位被置位(Asserted)。

- 如果中断使能,且ERRB引脚未被其他更高优先级的事件占据,则ERRB引脚被拉低,触发中断。

- 中断服务程序(ISR)被执行,以处理中断事件,包括读取状态寄存器来确定具体的错误,并采取适当的恢复措施。

具体的中断配置和处理过程可能需要根据实际的硬件设计和软件架构进行定制。

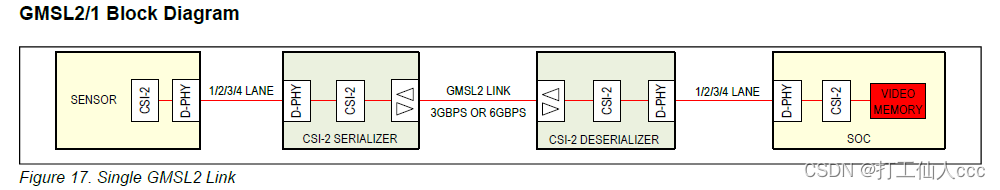

General Description

The MAX96714/F/R deserializers convert a GMSL™2/1 input to MIPI CSI-2 output. The devices allow a simultaneously transmit bidirectional control channel while forward video transmissions are in progress. The MAX96714/F/R operate at a fixed rate of 3Gbps or 6Gbps in the forward

direction and 187.5Mbps in the reverse direction. Data can be transmitted over low-cost 50Ω Coax or 100Ω STP cables that meet the GMSL2 channel specifications.

max96714/F/R解串器将GMSL2/1输入转换为MIPI CSI-2输出。传输正向视频信号时设备允许同时传输双向控制信道。正向支持3Gbps或6Gbps固定速率,反向支持187.5Mbps固定速率。数据可以通过低成本50Ω同轴线缆或者100Ω STP线缆传输。

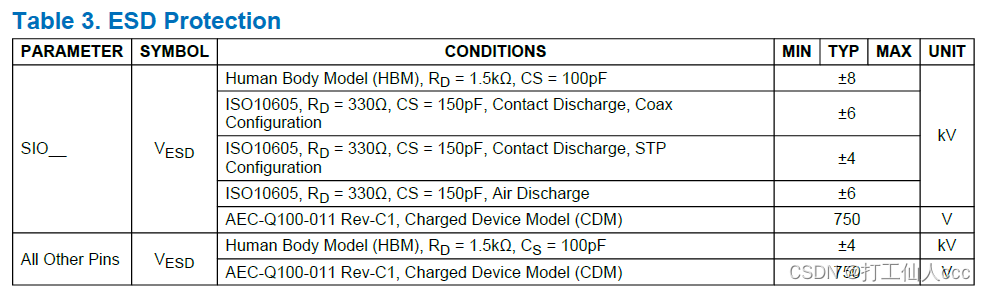

Absolute Maximum Ratings

(All voltages with respect to ground) ............................................

VDDIO .................................................................... -0.3V to +3.9V

VDD18 .................................................................... -0.3V to +2.0V

VDD ........................................................................ -0.3V to +2.0V

VTERM ................................................................. -0.3V to +1.32V

CAP_VDD ............................................................. -0.3V to +1.2V

SIO_(Active State) (Note 1) ................... (VDD18 - 1.1V) to VDD18

SIO_ (Inactive State) (Note 1) ................................-0.3V to +1.1V

D-PHY Pins (Note 2) .............................. -0.3V to (VTERM + 0.1V)

XRES, X2 ................................................ -0.3V to (VDD18 + 0.3V)

All Other Pins (Note 3) ............................ -0.3V to (VDDIO + 0.3V)

Continuous Power Dissipation (Note 4) ..........................1896mW

Storage Temperature Range ..............................-40°C to +150°C

Soldering Temperature (Reflow) .......................................+260°C

Note 1: Active State means the device is powered up and not in power-down modes. Inactive means the device is not powered up or powered up in power-down mode.

有效表示设备通电不在断电模式。无效表示设备断电或低功耗模式通电。

Note 2: Specified maximum voltage or 1.36V, whichever is lower.

Note 3: Specified maximum voltage or 3.9V, whichever is lower.

Note 4: Derate 34.5mW/°C above TA = +70°C. Maximum dissipation is determined using specified θJA and assuming maximum acceptable die temperature of 125°C.

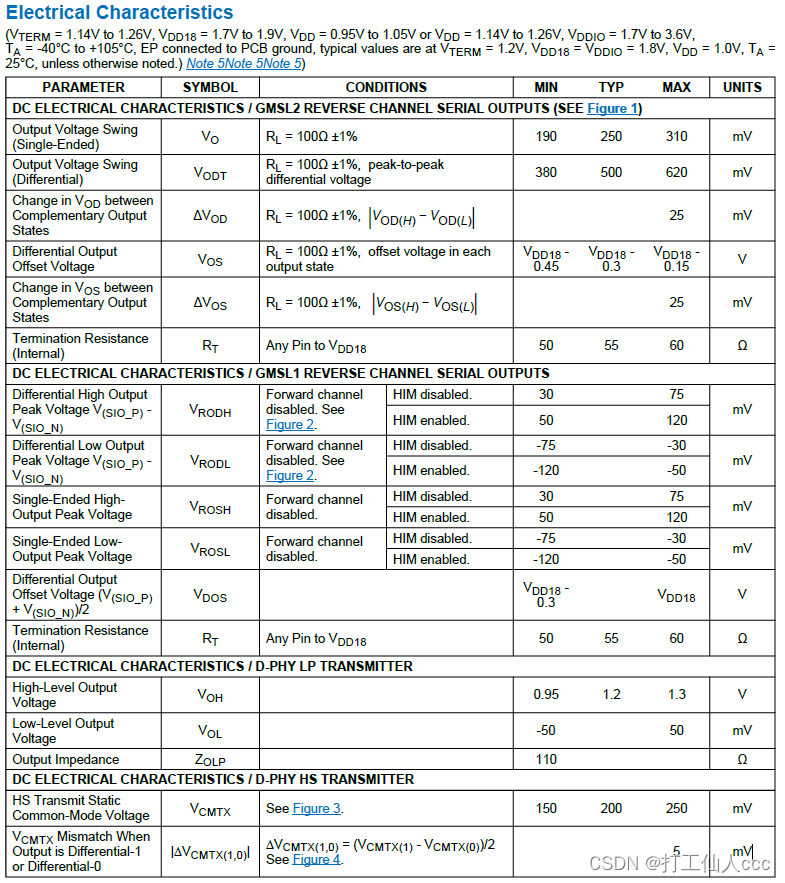

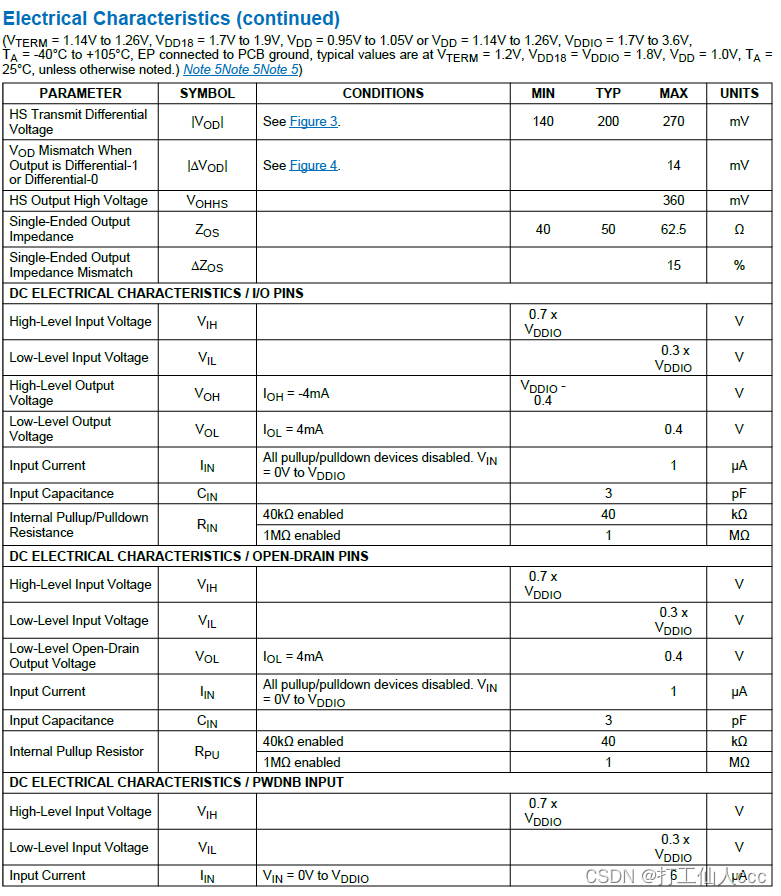

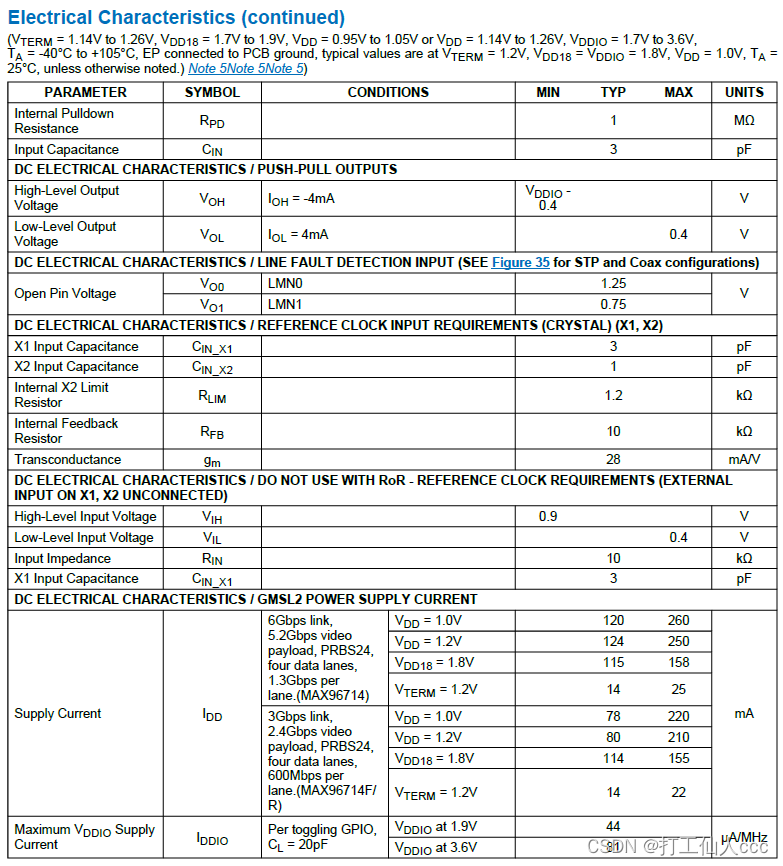

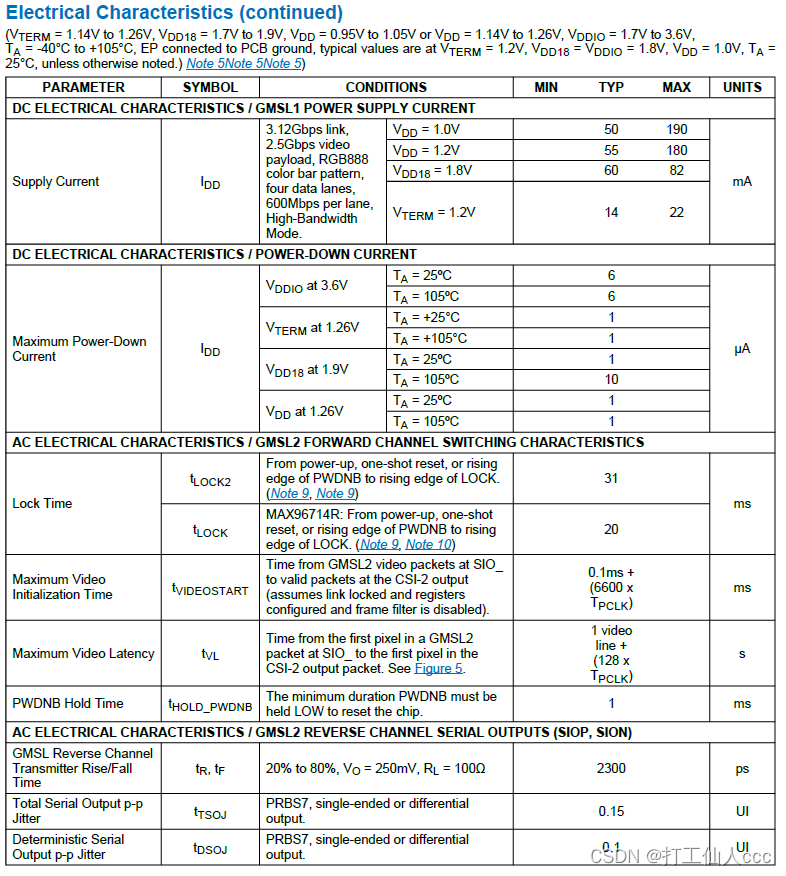

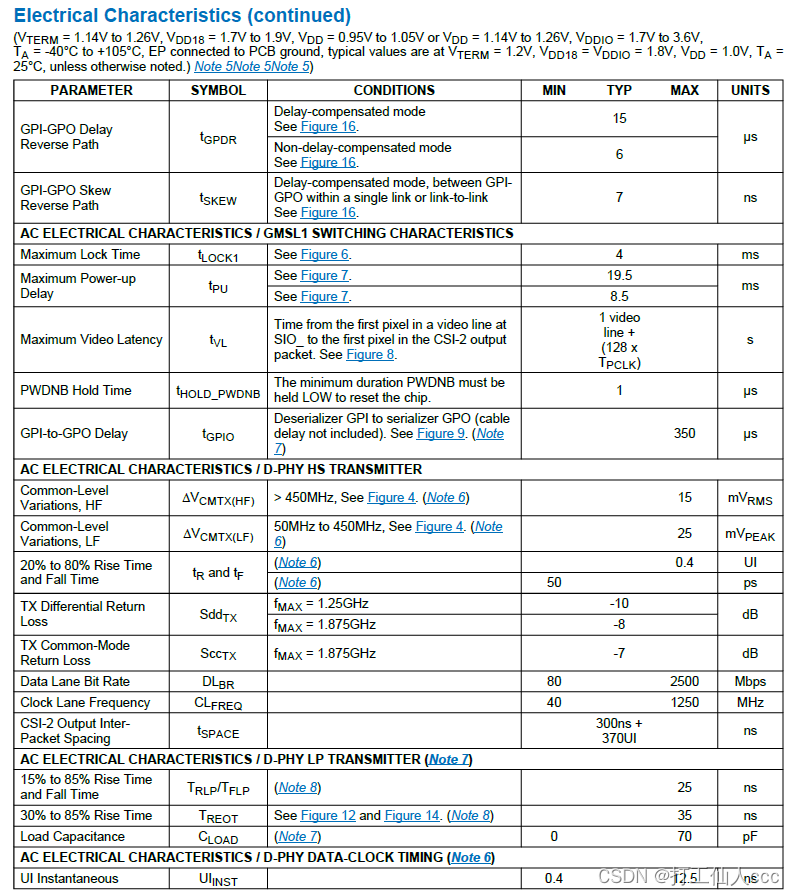

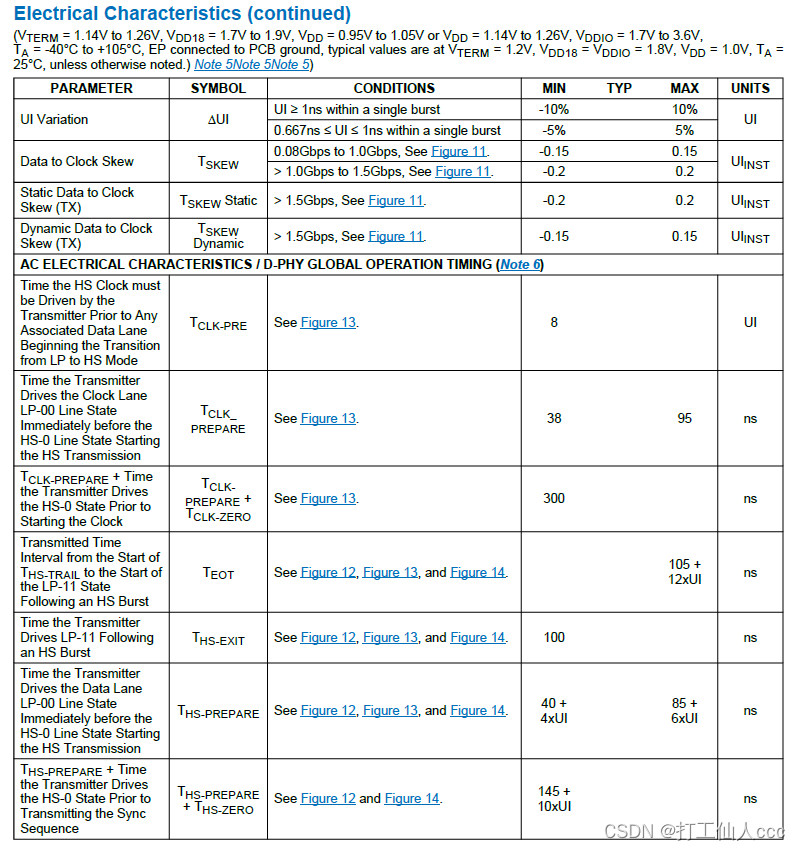

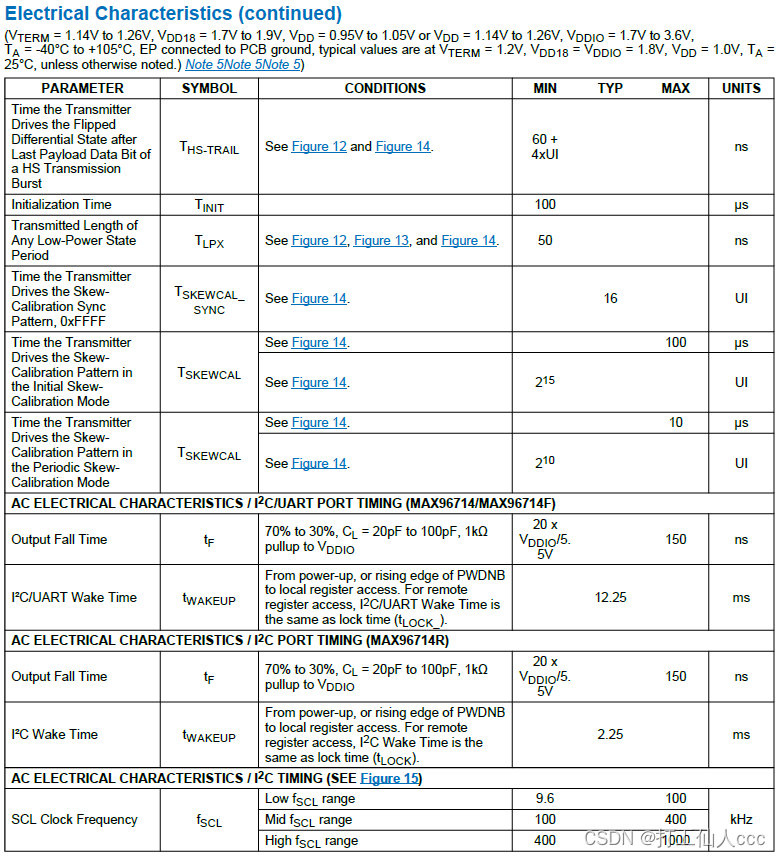

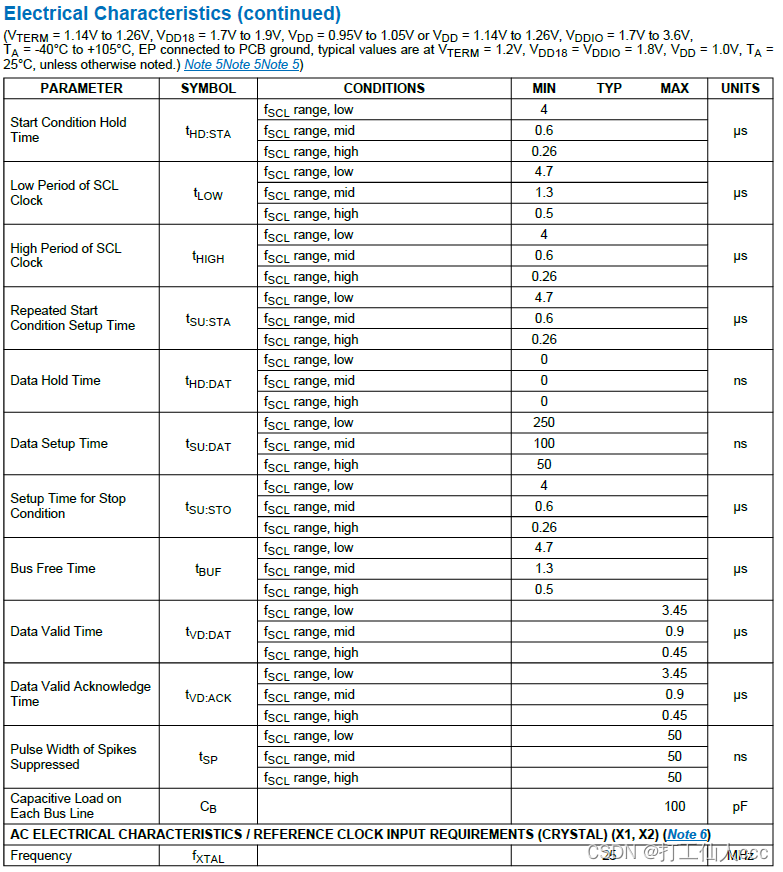

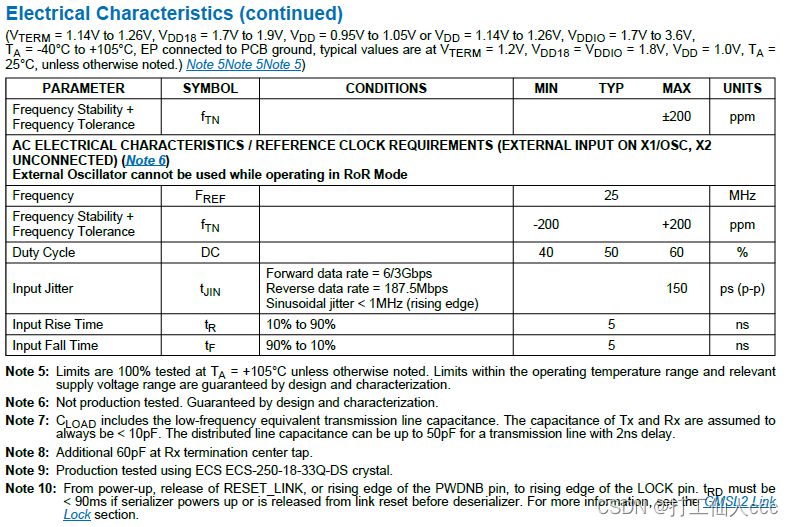

Electrical Characteristics

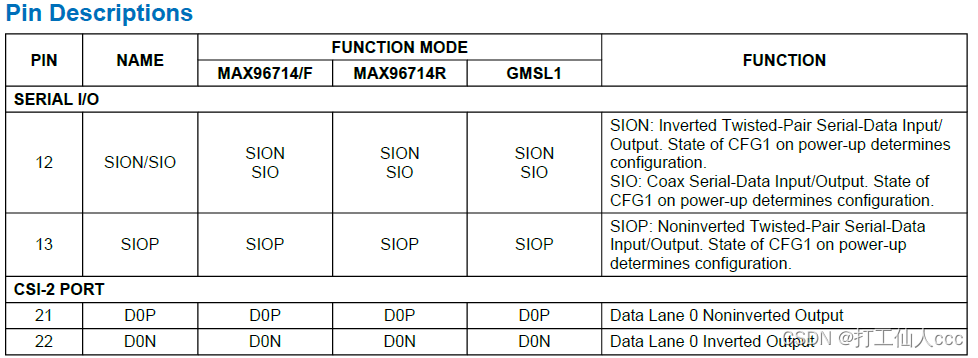

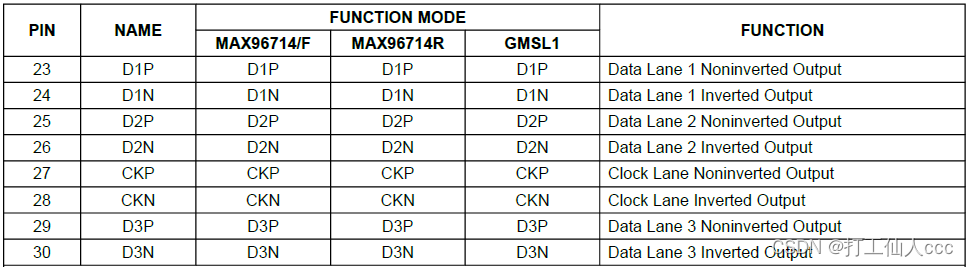

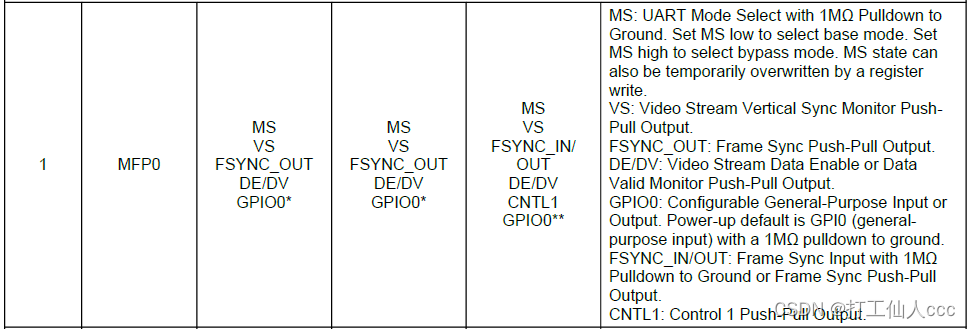

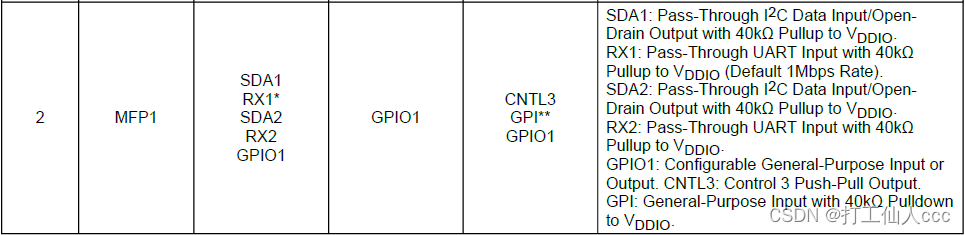

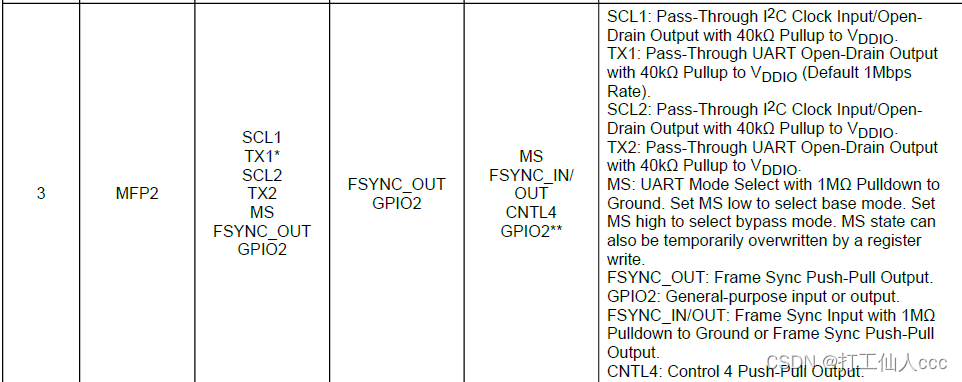

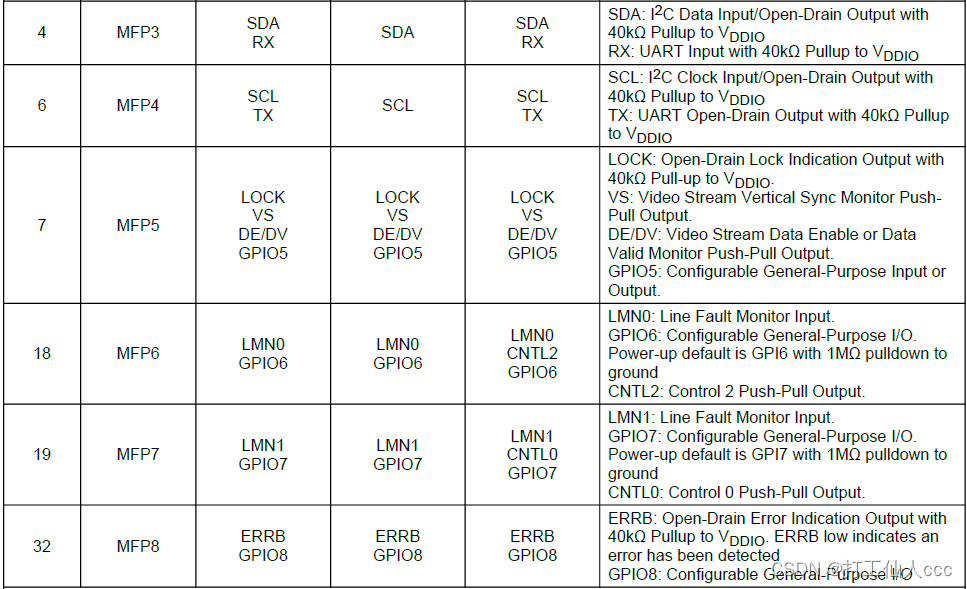

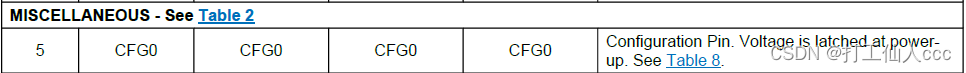

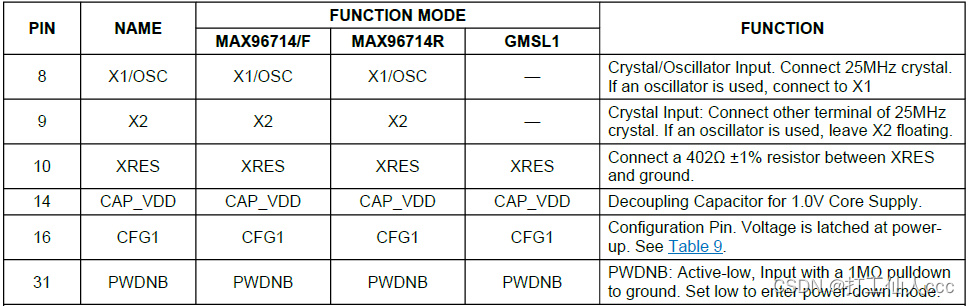

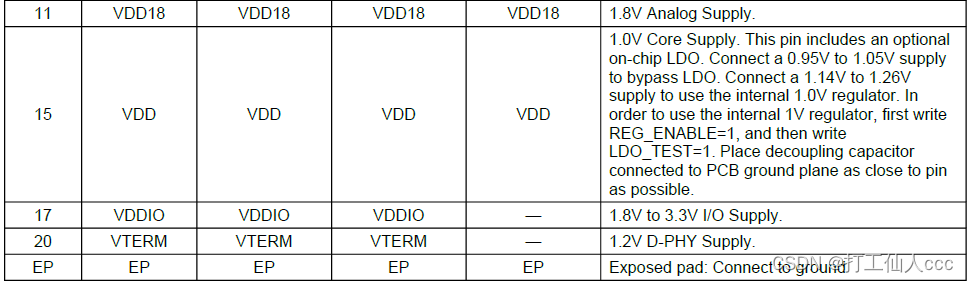

Pin Descriptions

SIO:同轴串行数据输入/输出。通电时的CFG1状态决定配置。

MS:UART模式选择,1MΩ下拉至接地。将MS设置为低以选择基本模式。设置MS高,选择旁路模式。MS状态也可以被寄存器写入临时重写。

MS:UART模式选择,1MΩ下拉至接地。将MS设置为低以选择基本模式。设置MS高,选择旁路模式。MS状态也可以被寄存器写入临时重写。

VS:视频流垂直同步监视器推拉输出。

FSYNC_OUT:帧同步推拉输出。

DE/DV:视频流数据启用或数据有效监视器推拉输出。

GPIO0:可配置通用输入或输出。通电默认为GPI0(通用输入)与1MΩ下拉接地。

FSYNC_IN/OUT:帧同步输入,1MΩ下拉接地或帧同步推拉输出。

CNTL1:控制1推拉输出。

SDA1:通过I2C数据输入/漏极开路输出,40kΩ上拉至VDDIO。

RX1:通过UART输入,40kΩ上拉至VDDIO(默认1Mbps速率)。

SDA2:通过I2C数据输入/漏极开路输出,40kΩ上拉至VDDIO。

RX2:带40kΩ上拉至VDDIO的直通UART输入。

GPIO1:可配置通用输入或输出。CNTL3:控制3推拉输出。

GPI:通用输入,40kΩ下拉至VDDIO。

SCL1:通过I2C时钟输入/漏极开路输出,40kΩ上拉至VDDIO。

TX1:通过UART开漏输出,40kΩ上拉至VDDIO(默认1Mbps速率)。

SCL2:通过I2C时钟输入/漏极开路输出,40kΩ上拉至VDDIO。

TX2:通过UART开漏输出,40kΩ上拉至VDDIO。

MS:UART模式选择,1MΩ下拉至接地。将MS设置为低以选择基本模式。将MS设置为高电平以选择旁路模式。MS状态也可以被寄存器写入临时重写。

FSYNC_OUT:帧同步推拉输出。

GPIO2:通用输入或输出。

FSYNC_IN/OUT:帧同步输入,1MΩ下拉接地或帧同步推拉输出。

CNTL4:控制4推拉输出。

LOCK:开漏输出锁定指示,40kΩ上拉至VDDIO。

LMN0:线路故障监视器输入。

ERRB:开漏错误指示输出,40kΩ上拉至VDDIO。ERRB低表示检测到错误

Detailed Description

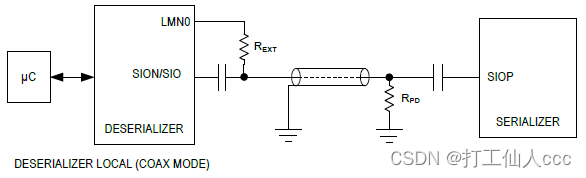

REXT:在有效LMN输入和GMSL互连之间连接REXT;仅在线路故障检测器所在的链路一侧需要。

RTERM:靠近同轴模式下未使用输入(SIOP)的链路隔离电容器

Introduction

Introduction

GMSL2 serializers and deserializers provide sophisticated link management for high-speed, low bit-error-rate,bidirectional serial data transport. The MAX96714/F/R deserializers support two modes: the Pixel mode offers flexible and bandwidth-efficient data transfer, while the Tunnel mode provides end-to-end data integrity of both sensor data and side-channel data.

The MAX96714/F/R support up to 3Gbps or 6Gbps forward and 187.5Mbps reverse packetized data transmission over the fixed-speed link.

MAX96714/F/R解串器支持两种模式:像素模式提供灵活且带宽高效的数据传输,隧道模式提供传感器数据和侧通道数据的端到端数据完整性。

Product Overview 产品概述

具有GMSL1向后兼容性的MAX96714/F/R GMSL2单通道解串器连接到串行器,该串行器将MIPI CSI-2或并行数据转换为CSI-2 MIPI数据输出。它使用I2C/UART通过控制通道与串行器通信。UART在MAX96714R上不可用。双向数据通过符合GMSL2信道规范的低成本50Ω同轴电缆或100ΩSTP电缆进行通信。

MAX96714/F/R具有四通道D-PHY v1.2输出端口,支持每通道80Mbps至2.5Gbps的数据速率。MAX96714/F/R有四个有源D-PHY v1.2通道。MAX96714/F/R最多支持16个虚拟通道。在像素模式下,支持的数据类型包括RAW8/10/12/14/16/20、RGB565/666/888/YUV422 8-/10位、用户定义、EMB8和通用长数据包数据类型。在隧道模式下,支持任何CSI-2数据类型。

具有MIPI CSI-2协议和D-PHY输出的单个传感器,如图17所示,传感器的输出以3Gbps或6Gbps的比特率发送到解串器。传感器数据在MAX96714/MAX96714F/MAX96714R CSI-2端口上输出,以供SoC捕获。

GMSL2 Overview 概述

GMSL2是一种固定速率传输介质,设计用于同时承载多种类型的通信信道。链路比特率基于25MHz晶体/外部振荡器产生的恒定频率链路时钟。链路时钟与视频像素时钟无关,超出了视频带宽不能超过可用链路带宽的自然约束。

GMSL2使用基于分组的协议以灵活的方式无缝共享通信信道之间的链路带宽。带宽分配是动态的,因此如果某个信道不活动,它就不会消耗任何链路带宽,并且所有剩余的活动信道都可以共享完整的链路带宽。最大分组大小是有限的,以防止单个信道在延长的时间内利用链路带宽。在大多数情况下,可用的链路带宽超过了带宽要求。空闲数据包用于填充未使用的链路带宽。相同的数据协议用于前向和反向信道以及视频和控制信道数据。

GMSL2提供了一种灵活的宽带数据链路,可以在远程设备之间传输高带宽双向数据。MAX96714/F/R专为远程高分辨率相机或类似传感器之间的接口而设计。除了链路的核心视频/宽带流部分外,GMSL2设备还提供各种外围/辅助功能,以实现灵活、稳健的系统实现。

GMSL2提供了广泛的数据完整性和安全功能。这些特征中的一些包括CRC错误检测,其使得能够识别视频或控制数据流中的错误。在控制信道CRC错误的情况下,标记分组的自动重传使控制信道速度和可靠性最大化。内部视频存储器包括ECC保护,可检测和校正内部损坏的像素数据。

GMSL2设备包含许多链路裕度优化和监控功能,可确保高链路裕度和强大的功能。连续自适应均衡每秒发生一次,以优化链路裕度,以适应环境变化和电缆老化。令人大开眼界的监视器功能提供了连续的链路裕度诊断,并包括各种阈值警报级别,每当检测到链路退化时都会触发运行时警报。

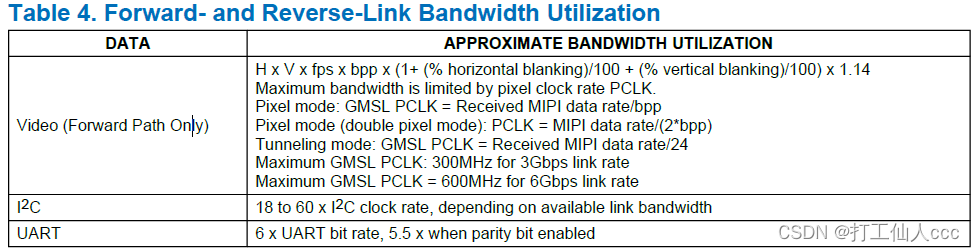

GMSL2 Bandwidth Information and Calculation 带宽信息与概述

MAX96714/F/R前向链路的固定链路速率为3Gbps,而MAX96714-F/R则为6Gbps。反向链路速率固定为187.5Mbps。GMSL2协议和信道编码开销大约为14%。这在正向方向上留下大约2.6Gbps或5.2Gbps的数据吞吐量,在反向方向上留下162Mbps的数据吞吐量。确保最坏的使用情况不会超过前向和反向链路的可用吞吐量。Maxim Integrated的评估套件(EV套件)GUI包括一个带(BW)计算器,可用于初始带宽需求估计。建议向工厂咨询高带宽使用情况,以确保无错误性能。

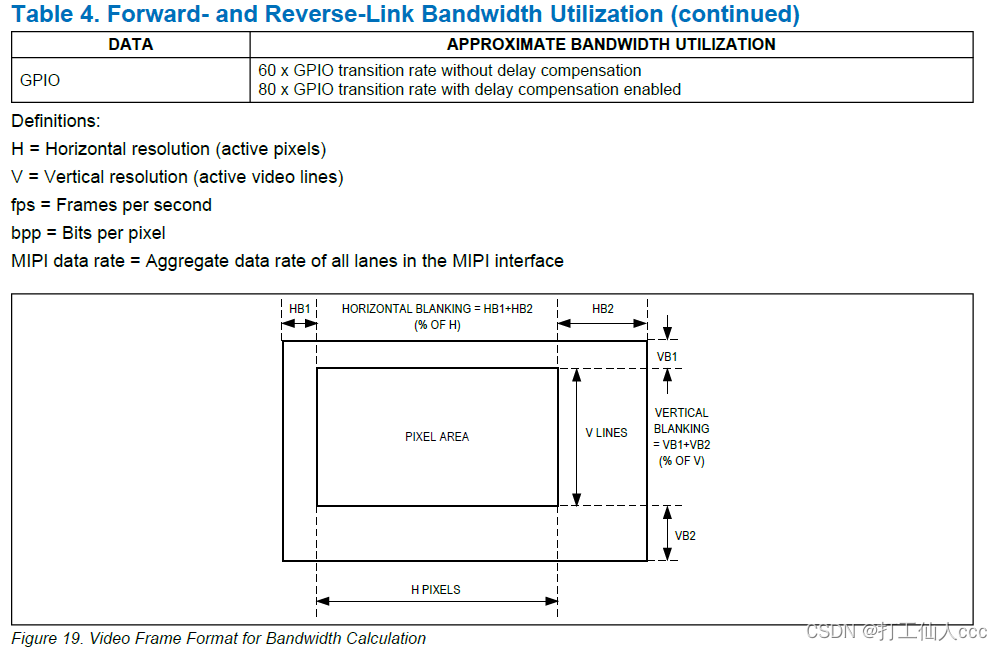

表4提供了每个通信信道的带宽利用率的粗略估计。

GMSL2 Minimum Blanking 最小空白

CSI-2串行器和解串器所需的最小水平消隐周期是40个像素或300ns+370UI的最大值(其中UI被定义为CSI-2通道速率的周期)。在大多数情况下,40个像素是较大的数字。最小垂直消隐周期是一个视频行。最小的垂直前廊是一条视频线。

推荐的垂直后廊是一条视频线。

像素模式下的最小垂直后廊是的最大值:

● 40像素

● 300ns+370UI

隧道模式下的最小垂直后廊为以下值的最大值:

● 40像素

● 200个PCLK周期

Auto-AEQ (Automatic Adaptive Equalization) 自使用均衡

GMSL2设备自动调整前向路径接收器特性,以补偿由电缆、连接器、温度和PCB组成的通道的插入损耗和回波损耗特性。这种方法可优化符合GMSL2信道规范的任何信道的性能。均衡器架构使

GMSL2链路对噪声、串扰和反射具有鲁棒性。初始自适应在链路锁定期间执行,然后每秒调用一次以跟踪温度和电压变化,这对不断变化的汽车安全应用至关重要。自适应过程通过使用内置的睁眼监视器来优化均衡器系数,以最大限度地提高睁眼效果。

Tunnel and Pixel Modes隧道和像素模式

MAX96714/MAX96714F/MAX96714R专为高级驾驶员辅助系统(ADAS)设计,其中数据完整性是关键的安全要求。先前的GMSL2解决方案仅支持像素模式,用于在GMSL链路上传输来自MIPI CSI-2接口的接收数据。

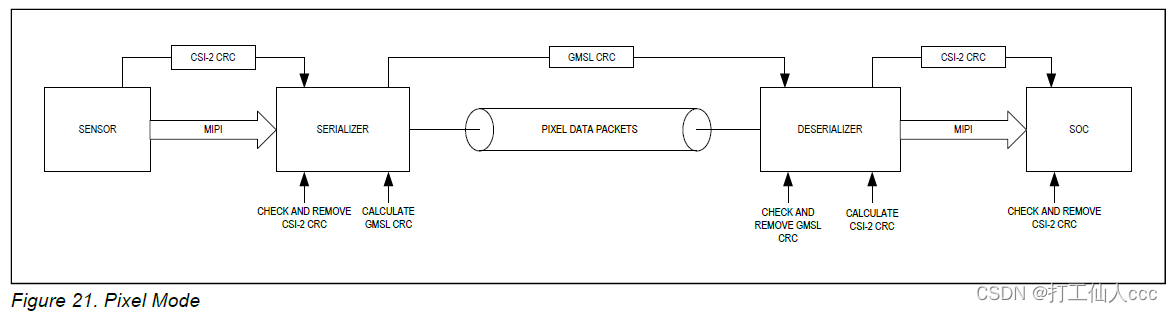

在像素模式下,在串行器的CSI-2输入接口处对接收到的CSI-2数据进行解包。所接收的CSI-2分组报头包括纠错码(ECC),其在串行器输入处被检查和移除。接收到的CSI-2分组页脚包含CSI-2循环冗余校验(CRC),该CRC也被检查和移除。

在CSI-2接口处接收并提取视频线像素数据和视频路由信息,例如数据类型和虚拟信道。视频像素数据、控制信道数据和路由信息都被输入到串行器中的调度器。调度器使用GMSL协议对数据进行分组和封装,并对GMSL链路上的数据传输进行排序。GMSL链路上的视频数据传输受到线路CRC的保护,线路CRC是GMSL协议的一部分。

解串器接收GMSL分组并验证GMSL2线路CRC。解串器输出端的CSI-2接口使用CSI-2协议封装每条视频线,并通过CSI-2接口以CSI-2格式将其输出到SoC。见图21。

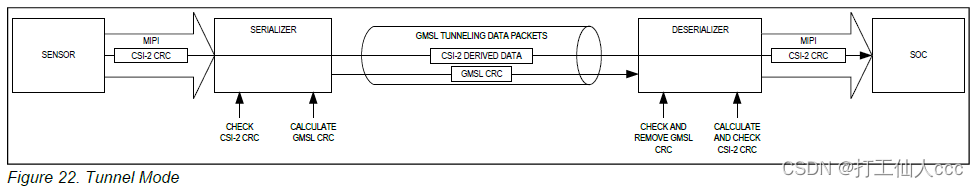

在隧道模式中,在串行器输入处检查接收到的CSI-2 ECC字节和CRC字节。这些,以及路由和像素数据,作为字节流被接收。字节流被分成更小的数据包,这些数据包使用GMSL2协议进行封装。

串行器在GMSL信道上添加线路CRC保护传输。该CRC覆盖视频线路的整个GMSL2分组字节流。见图22。解串器接收所发送的GMSL2分组和控制信道分组,检查并去除GMSL CRC,将视频数据与控制数据分离,并重构作为CSI-2接口上的SoC的输出的每个接收到的CSI-2分组。对在CSI-2接口上输出的视频数据计算CRC。解串器将该CRC与从视频源接收的原始CRC进行比较。这种比较保证了在标准MIPI接口上输出的整个数据包与在串行器输入处接收的数据包相同。如果发送多个数据类型,则隧道模式的带宽效率更高。因为在串行器输入处接收的数据和从解串器输出的数据被验证为相同,所以隧道模式不允许对视频数据进行处理,例如水印或有损数据压缩。串行器和反串行器上的不同数据速率和通道计数仍然是可能的。

Video Pipes - Stream Mode, Virtual Channel, Data Type, and Memory Information视频管道-流模式、虚拟频道、数据类型和内存信息

在GMSL2像素模式中,视频数据的传输基于视频管道的概念。在管道中携带数据允许GMSL2桥接不同的数字视频接口(即,并行YUV422源到CSI-2汇点)和检测。

管道承载视频流和视频同步数据,并以三种模式之一运行。在所有模式中,管道可以承载多个并发视频流,每个流具有不同的虚拟通道和数据类型,如下所示:

● 模式1:具有高达24bpp的恒定每像素比特数(BPP)的流。流的BPP必须相同。

● 模式2:具有16bpp、14bpp、12bpp、10bpp或8bpp的流。小于16bpp的流用零填充。

● 模式3:具有两种不同BPP速率的流。一个流的BPP必须是另一个流BPP的两倍或三倍。

较高的BBP流为24bpp。

模式1和模式3以全带宽传输数据,但对BPP的限制比模式2更多。模式2允许具有不同BPP速率的流,但小于16bpp的流使用比GMSL2链路上所需的带宽更多的带宽来承载(因为零填充)。模式1或3对于大多数应用程序来说已经足够了。如果应用程序不需要最大链路带宽,则模式2需要更方便。

MAX96714/F/R有一个视频管道。该管道有一个16k字节的专用视频线缓冲器,其线路长度可达4096个24位像素。在视频数据被发送到MIPI输出端口之前,数据被存储在行缓冲器中。在像素模式下,行缓冲器在控制器可读取数据之前存储完整的视频数据行。

如果视频源具有CSI-2输出,则分组DT和VC可以保持原样,或者通过像素模式下的寄存器编程重新分配。有两种方法可以更改MAX96714/F/R中的VC/DT。

1.目的地和来源地的使用。由于其功能,此功能比下面提到的覆盖功能稍微强大一些。最多可以将16个DT/VC传入对映射到16个DT/WC传出对。有关此功能的功能,请参阅《GMSL2用户指南》

2.如果需要,可以通过BACKTOP13-VC覆盖-BACKTOP15/6-MIPI软件数据类型覆盖-BACKTOP18-BPP覆盖来覆盖BPP/VC/DT。

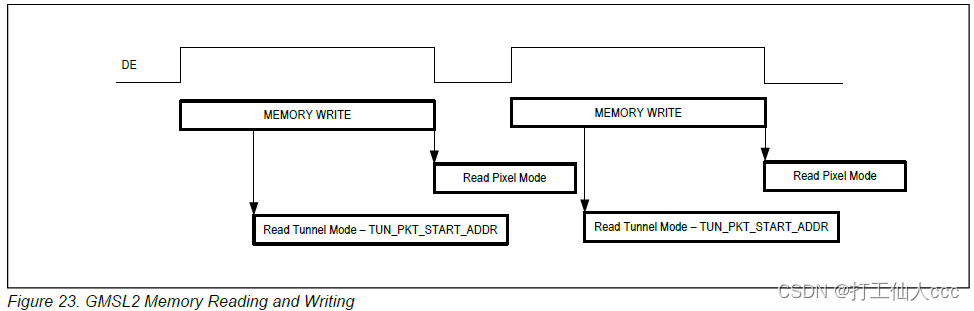

MAX96714/F/R在隧道模式下支持一种名为“直通”的新功能,该功能允许控制器更快地开始从内存中读取。寄存器TUN_PKT_START_ADDR可以调整写入后何时开始从内存读取。这允许将视频线内存扩展到4096像素以上的行,还可以通过更快地读取内存来减少延迟。一旦数据被读出,就不能再进行第二次读出。

图23显示了MAX96714/F/R内存操作。

为了防止缓冲区溢出,必须将CSI-2端口数据速率编程为等于或大于传入数据速率的速率。将输出速率编程为快于输入视频或数据的带宽会增加分组间隔(分组之间的LP时间)。视频内存具有内置溢出检测功能-BACKTOP11。当视频带宽高于MIPI端口上输出的数据时,就会发生这种情况,不会给内存清空的机会。

在隧道模式下不会重新格式化数据。对功能安全的要求是视频数据保持不变,从而可以由主机将其与隧道化的CSI-2 CRC进行比较。

数据退出重定时缓冲区后,将经过数据类型(DT)和虚拟通道(VC)重新分配阶段。如果视频源具有CSI-2输出,则分组DT和VC可以各自保持原样,或者通过寄存器编程重新分配。

MAX96714/F/R-GMSL2协议为视频内容分配每个数据包的24位,以有效地使用GMSL2前向信道带宽。串行器和MAX96714/F/R包含双像素模式,将x2 8bpp/10bpp/12bpp填充到同一数据包中。有关详细信息,请参阅bpp8dbly/bpp10dbly/bpp12db寄存器。

Video Memory ECC Protection视频内存ECC保护

ECC保证了通过管道的线存储器传播的数据的完整性,它能够校正每32位视频数据中的1位错误和检测2位错误。此功能提供对未受传入GMSL流或传出CSI流的CRC保护的数据的保护,消除了内部生成的静默比特错误可能损坏传出CSI-2流的可能性。ERRB引脚和错误状态寄存器FS_INTR1的状态可用于检测内存撬ECC错误的存在。有意记忆错误注入可用于诊断

Video PRBS Generator/Checker视频PRBS生成器/检查器

GMSL2设备包括用于视频链路测试的内置视频PRBS发生器/校验器。例如,串行器的PRBS生成器可以与解串器的PRB检查器结合使用,以测试连接两个设备的GMSL2视频信道。这里,MAX96714/MAX96714F/MAX96714R的PRBS检查器功能将接收到的PRBS流与预测的PRBS数据进行比较,以建立任何错误。要运行视频PRBS测试,请参阅GMSL2用户指南了解更多信息。

Frame Sync

在一些相机应用中,传感器需要帧同步信号来将帧的输出与系统中的其他相机同步。MAX96714/F/R可以在内部生成FSYNC信号,也可以从外部SoC接收FSYNC信号,并通过GMSL反向通道将其发送到传感器。MFP0或MFP2被编程为接收外部FSYNC信号,并且MAX96714/F/R被编程为FSYNC下属。为了生成内部FSYNC,MAX96714/F/R被编程为FSYNC电源。有关详细信息,请参阅寄存器FSYNC_0。

Vertical and Data Enable or Data Valid Sync Outputs垂直和数据启用或数据有效同步输出

MAX96714/MAX96714F/MAX96714R可以输出视频流的垂直同步(VS)和数据启用/数据有效(DE/DV),以通过处理器监控视频时序。此功能提供对在CSI-2输出处不直接可用的VS和DE/DV信号的访问。VS和DE/DV输出是MFP0和MFP5的替代功能。

反向通道

控制器可以通过GMSL2串行链路同时高速发送和接收控制和侧信道数据

视频数据。MAX96714/F/R支持以下接口:

● 主I2C/UART-MAX96714R上不存在UART

● 直通I2C/UART-MAX96714R上不存在

● GPIO

上述所有接口都可以通过GMSL2链路传递数据,但GMSL2设备寄存器只能通过主I2C/UART接口进行访问和配置。

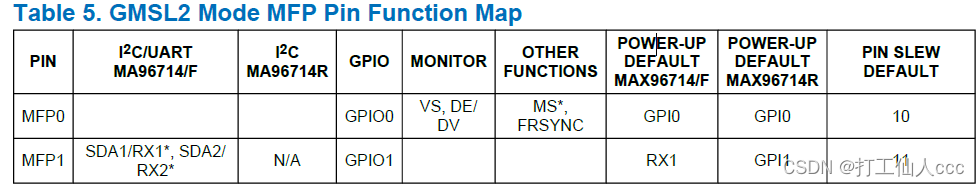

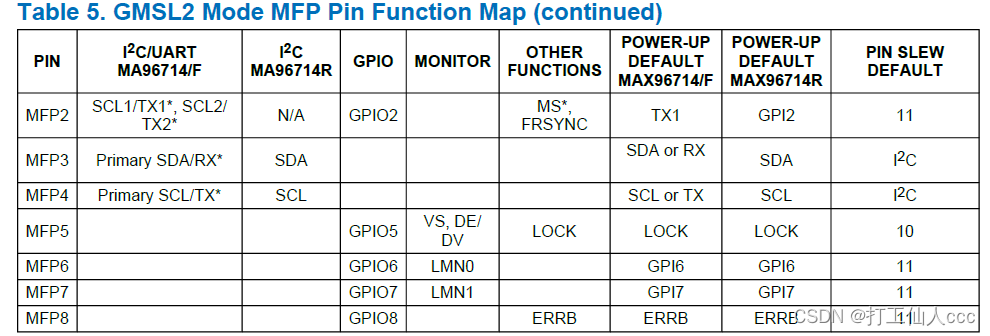

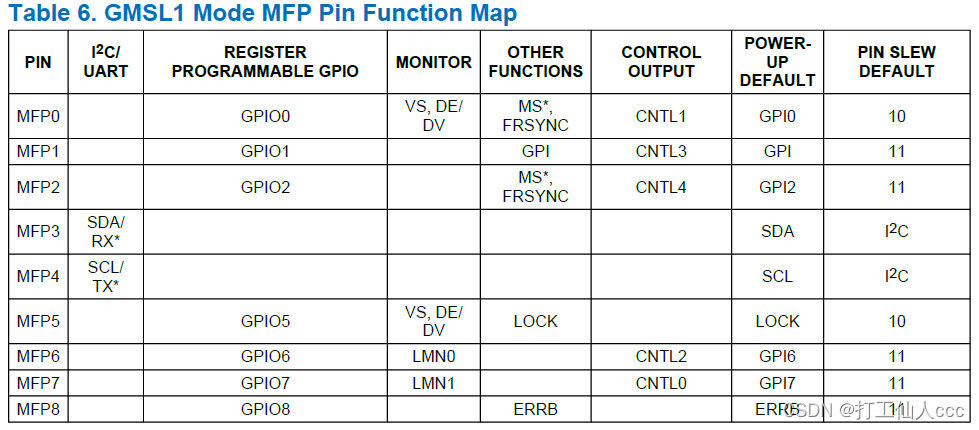

反向通道及其各种接口可通过多功能引脚访问。多功能引脚具有默认功能,通电后可编程为备用功能。由于给定设备上可用引脚数量的实际限制,并非所有接口都可以同时支持。参见多功能引脚分配部分的表5和表6,了解默认和备用多功能引脚功能以及可用的接口组合。

Scheduler/Arbiter 计划员/仲裁员

调度器在较低优先级值之前发送具有高优先级值的分组。每个通信传输适配器在向远程侧传输数据之前为分组请求设置优先级。优先级值为2位,可进行以下设置:0=低、1=正常、2=高和3=紧急-有关设置优先级,请参阅TR0。调度器提供了足够的链路带宽,并选择在未决的活动请求中发送具有最高优先级的分组。随着链路带宽变得稀缺,优先级变得更加重要,并相应地分配优先级。

在大多数情况下,每个发射机适配器都应该使用正常的优先级设置(优先级=1),以允许调度器根据最近的带宽使用情况选择传输调度。如果数据包需要低延迟或等待了指定的时间段,则可以增加数据包优先级。例如,如果直到最大延迟要求的一半已经过去才对数据包请求进行服务,则具有最大等待时间要求的数据包可以具有增加的优先级。这也可以用于具有连续数据流(例如视频)的通信信道。当传输适配器数据缓冲区接近溢出时,可以提高优先级。相反,寄存器配置允许覆盖每个通道的优先级设置。如果主机μC希望优先考虑一个通道而不是其他通道,则此选项非常有用。

具有非常宽松的延迟要求的通信信道可以使用低优先级设置(优先级=0)。如果存在更高优先级设置的任何未决请求,则调度器不为这些低优先级分组提供服务。在这种安排中,链路带宽分配可以达到视频的理论最大值。然后可以在视频水平消隐时间期间发送低优先级分组,在此期间视频信道带宽使用显著下降。

Primary and Pass-Through I2C/UART初级和直通I2C/UART

主I2C/UART位于SDA_RX和SCL_TX引脚上。I2C(SDA、SCL)或UART(Tx、Rx)(不在MAX96714R接口上)由通电时的CFG0引脚电压选择(见表8)。所选接口提供从链路任一端对MAX96714/F/R寄存器和外围寄存器的访问。

主控制器可以位于链路的任一端(通常是相机应用程序的解串器端)。MAX96714/F/R支持双主控制器,前提是使用软件仲裁(如令牌传递)来防止数据包冲突。反向通道一次只允许一个主主机进行通信。

MAX96714/F可以选择共享相同MFP的两个直通I2C/UART通道。这些通道不能访问GMSL2串行器或解串器中的寄存器;它们只是在GMSL2链路上传输I2C或UART信号。这允许I2C通道被分离,从而不会发生多主冲突。

Multifunction Pin Assignments多功能引脚分配

MAX946714/F/R提供一系列外围I/O功能。这些功能通过寄存器控制映射到多功能引脚(MFP)阵列。每个MFP都有几个可能的功能,但一次只能使用一个。用户通过对适当的寄存器进行编程来选择适合其使用情况的MFP函数:FRSYNC=FSYNC_0|VS=CFG_0/1|DE=CFG_2/4|。

Pin Descriptions(引脚说明)表显示了每个MFP的默认和备用功能,按优先级顺序列出(最高优先级列在第一位)。当通过寄存器写入启用较低优先级的功能时,必须禁用较高优先级的功能。

*MAX96714R不具有MS、UART或直通功能。

除了配置为I2C/UART或开漏输出的MFP(其转换时间是固定的)之外,每个MFP的转换时间可以通过编程PIO_SLEW寄存器从默认值更改。

转换时间取决于PIO_SLEW_0/1/2和VDDIO电源电压。关于每个PIO_SLEW_0/1/2设置的典型上升和下降时间,请参见表7。要更改MFP的转换时间,请对PIO_SLEW_0/1/2表7进行编程。有关详细信息,请参见PIO_SLEW_0/1/2。当选择时,这些功能的转换时间的寄存器控制将自动绕过。

General Purpose Input and Output (GPIO)

GPIO通道用于通过GMSL2链路传输低速(<100Kbps)信号。MFP引脚可以编程为GPI、GPO(推挽输出)或ODO(开漏输出)。通过对每个GPIO引脚的GPIO_TX_EN和GPIO_RX_EN寄存器位进行编程,可以将每个GPIO管脚配置为输入、输出或输入/输出。请注意,对于配置为输入/输出的引脚,可以避免不必要的环路行为:当引脚由从远程侧接收的转换驱动时,驱动的GPIO转换不会传输回来。GPIO引脚可以交替地被控制并且仅从寄存器读取。大多数GPIO引脚可编程为1MΩ或40kΩ上拉/下拉/无上拉/下拉、漏极开路或

推挽输出。有关配置和编程,请参阅寄存器GPIO_A/GPIO_B-MFP0。

GPIO数据包具有32个可能的GPIO通道ID。每个GPI根据GPIO_TX_ID寄存器映射到一个通道ID。在接收端,每个GPO输出具有与该引脚的GPIO_RX_ID寄存器相对应的编程GPIO通道ID的接收数据。这在确定哪个GPIO输入驱动哪个GPIO输出方面提供了灵活性。

GPIO通道不具有带宽效率,应用于低速信号。每个GPIO转换在GMSL2链路上使用40-80比特进行传输,在反向链路上使用40比特到60比特(由于接收到ACK分组)。

有关各种配置的更多信息,请参阅《GMSL2用户指南》

Automatic Repeat Request (ARQ)/Automatic Retransmission

自动重复请求(ARQ)/自动重传

具有控制数据的通信信道(I2C/UART、GPIO)带宽相对较低,但需要最高的数据完整性保护。这里采用可选的自动分组重传方法ARQ(自动重传请求)。ARQ与16比特分组CRC一起工作,以检测分组是否被无错误地接收。分组在发送侧附加有2比特序列号,并且在成功接收到每个数据分组时从接收器侧发送确认分组。这些分组被存储在发送侧,直到它们被确认为止。如果确认数据包没有在预定间隔内到达,或者确认数据包的序列号与预期值不匹配,则在队列顶部等待的数据包将自动重新发送。

确认数据包使用与低带宽数据包相同的头字段,但以不同的特殊符号开始,以将其与常规数据包区分开来。这种简化的格式使重传交换独立于通信信道。注意,这种较小的分组格式不包含数据,从而消除了对完整的16位CRC的需要。相反,Header符号在数据包中发送两次,并相互检查实例以确保匹配。确认分组还包括与正确接收的数据分组的序列号相同的2比特序列号。数据包发送器跟踪哪些数据包被确认。

请参阅每个功能的ARQ0/1/2寄存器GPIO/控制通道/通过1和2来配置ARQ。默认情况下,每个功能都启用ARQ。

Functional Safety Features - POST/LBIST/MBIST - CRC

功能安全特性-POST/LBIST/MBIST-CRC

MAX96714/F集成了许多安全功能,包括开机自检(POST),其中包括逻辑内置自检(LBIST)和内存内置自检(MBIST)。在通电时,LBIST验证关键逻辑块是否正常工作并且没有潜在故障。MBIST检查行缓冲存储器和解串器中的其他小存储器,以确保数据在被发送到MIPI输出端口之前被正确存储。POST生成一个通过/失败结果,该结果可以通过每个测试的寄存器读取。故障不会阻止设备运行,但会断言ERRB。

用于读取POST/LBIST/MBIT信息的寄存器包含在REG_POST0寄存器中。

MAX96714/F包含以下CRC。所有CRC都需要链路或通信主机两侧的启用和理解。

1.位于RX1寄存器中的前向信道CRC-6/3Gbps使能。启用时,选择正确的管道

来自序列化程序。

2.反向信道CRC-位于TR0中的187Mbps使能-控制信道CRC

3.外部I2C/UART CRC-这是从MAX96714/F到主机的I2C/UART连接的CRC/

主控制器。要启用此功能,请参阅I2C_UART_CRC7。

4.信息帧正向和反向信道CRC-FWD-视频信息帧是在每条线路和每个VSYNC之后发送的低带宽分组。REV信息监控锁定状态。两者都默认启用-TR0-信息帧CRC启用

5.视频线CRC-用于检测视频线内的像素损坏-Video_RX0

6.视频数据包CRC-启用时,每个携带36个像素的数据包都受到CRC-INTR6的保护,以启用

7.隧道模式CRC-CSI-2 CRC字节-要启用,请查看MIPI_PHY16

8.GPIO正向和反向通道CRC-要启用,请查看TR0 GPIO CRC

9.通过正向和反向通道1和2 CRC-要启用,请查看TR0通过1/2

10.RBB反向信道CRC-在数据的仲裁和调度中发生的故障为Fault_OEN

11.线存储器ECC-CRC不能被输入的数据所信任,因此执行ECC-

FS_INTR0。有关ECC阈值的进一步设置,请参阅《用户指南》。

12.寄存器表CRC-可以使用滚动CRC来确认是否发生了任何寄存器更改。要启用,请参阅

REGCRC0/1/2/3。有关详细信息,请参阅《用户指南》。

13.EFUSE CRC-包含芯片配置和测试信息的电气保险丝。此功能位于

FS_INTR0

14.GMSL1视频线CRC-GMSL1_1C

15.GMSL1反向信道CRC-GMSL1_18

16.GMSL1反向信道分组CRC-GMSL1_19

上面提到的所有CRC都是16位的,除了视频线是32位的。

其他功能安全功能,如过电压、欠电压、溢出等,可在适用于该特定功能的其他功能中找到。

RoR (Reference over Reverse)

RoR(反向参考)

反向信道上的参考时钟(RoR)是GMSL时钟操作模式,其中串行器通过GMSL链路从解串器接收其参考时钟。RoR消除了在链路的串行器侧上对晶体振荡器的需要。

在RoR模式中,串行器的定时参考是从反向信道上发送的信号中提取的。串行器芯片上锁相环(PLL)使用来自解串器的恢复的时钟来合成串行器输出参考时钟RCLKOUT。

MAX96714/F/R上默认启用RoR模式。

RoR中晶体振荡器的去除提供了几个优点:

● 降低了系统成本

● 提高了可靠性

● 减少了板面积

● 简化的板布局

Link Error Generator

链接错误生成器

每个GMSL链路都包括一个可配置的错误生成器,该生成器在传输前立即将错误注入输出数据流。解串器将错误注入反向通道,串行器将错误插入正向通道。接收设备检测、计数并标记错误,从而能够彻底验证系统对不同严重程度的错误条件的响应。有关如何实现链路错误生成器的更多信息,请参阅《GMSL用户指南》。

Cabling Options

布线选项

GMSL2可容纳50Ω同轴电缆或100Ω屏蔽双绞线(STP)电缆。电缆必须具有足够的回波和插入损耗特性,才能获得最佳的全双工链路性能。有关更多信息,请参阅GMSL2信道规范。

Eye-Opening Monitor

片上眼图(EOM)使GMSL2部件能够监视活动链路上的链路裕度,并在其低于可接受水平时产生中断。例如,如果电缆损坏,链路可以无错误运行,但链路裕度低于所需。这使得用户能够在发生任何链路错误之前对不断恶化的电缆性能做出主动反应。GMSL2设备可以测量均衡器输出的水平或垂直睁眼。一旦链路激活,测量将以大约1Hz的速率自动激活。EOM块将在眼睛中心采样的数据与水平EOM的相位偏移或垂直EOM的电压偏移的样本进行比较EOM。然后报告睁眼,如果睁眼低于用户定义的阈值,EOM可以触发中断或重置。

Line Fault

线路故障

GMSL解串器包括一种新颖的线路故障检测电路。它检测并报告断路、对蓄电池短路、对地短路和线对线短路。线路故障监测器需要同轴模式和STP模式下的外部电阻器REXT和RPD连接到LMN_引脚,如图35所示。参考部件值见表2。

默认情况下,线路故障监测器被禁用,配置选项可通过寄存器获得,状态可通过INTR2/3和fault_STAT读取。线路故障检测不能与同轴电缆供电(PoC)或交流耦合接地应用程序结合使用。

线路故障监测器引脚在同轴电缆或STP应用中提供灵活的连接和编程。

图35说明了线路故障检测位置的两种配置选项。本地端串行器配置通常用于显示链路,而本地端解串器配置一般用于相机链路;然而,任何一种配置都可以在任何设备串行链路系统上使用。此外,适用于同轴电缆或STP模式。

Spread Spectrum

扩频

MAX96714/F/R可以接受前向信道6/3Gbps扩频,这可以用于减轻设备发出的电磁干扰。通过用锯齿形轮廓以25kHz的速率调制内部6GHz时钟来减少窄频率峰值。为了保持一致的锁定时间,建议不要启用扩频。要启用此功能,请参阅《GMSL2用户指南》或与工厂联系。并不是所有寄存器都对客户可见。

CSI-2 Output Interface

MIPI Lane Information

CSI-2输出接口

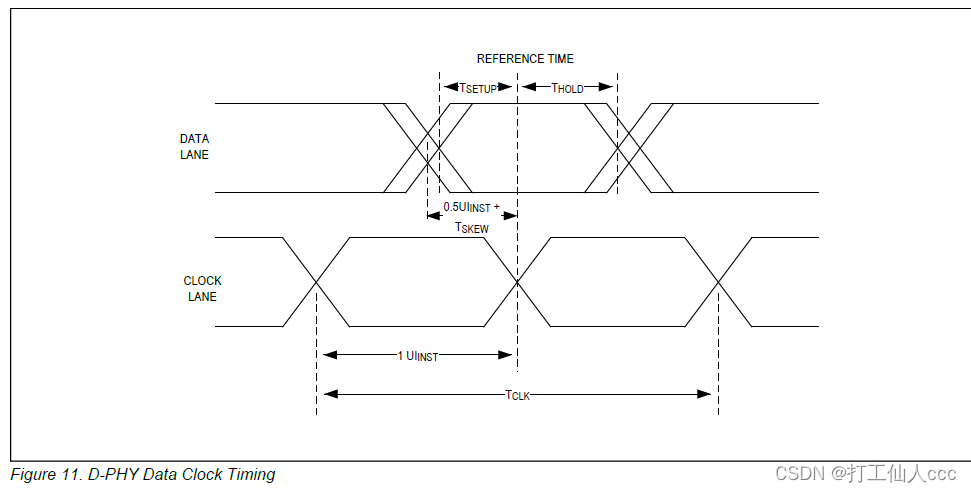

MIPI通道信息视频数据通过单向MIPI CSI-2 v1.3输出端口输出。D-PHY v1.2接口支持四个差分通道。为了简化PCB布局,支持通道和极性交换。有关更多信息,请参阅MIPI_PHY3和MIPI_PHY5。D-PHY输出支持每个通道高达2.5Gbps的数据速率。

所有与MIPI相关的配置都在视频流开始之前编程。

CSI-2 Virtual Channel

CSI-2虚拟信道

该设备支持虚拟通道,包括CSI-2 v2.0中引入的虚拟通道扩展(VCX),最多可支持16个虚拟通道。

MIPI CSI-2输出配置

由于对许多主机接收器控制器和PCB路由的限制,MAX96714/F/R具有许多MIPI优化,可用于实现最佳MIPI定时。有关MAX96714/F/R执行的各种MIPI定时调整,请参阅MIPI_PHY1/2/3/5/8/9。MAX96714/F/R具有微调MIPI输出时钟的能力。请参见BACKTOP25。在进行定时调整之后,必须使用MIPI_PHY15来执行MIPI控制器的重置。

MAX96714/F/R支持连续的D-PHY时钟输出。当MAX96714/F/R接收到视频流时,它们开始在MIPI时钟通道上发送传输开始(SOT)序列,然后是连续的高速时钟脉冲。SoC中的D-PHY接收器应该准备好在传输视频之前接收时钟SOT转换,因为时钟通道上的SOT序列只发送一次。一旦MIPI进入高速模式,时钟通道继续发送高速信号,直到MAX96714/F/R复位或断电。

MAX96714/F/R通过允许在HS传输模式下直接从每个D-PHY输出通道生成PRBS输出流,促进了MIPI PHY特性的表征。可用模式是PRBS9、PRBS11和PRBS18,并且得到的输出数据是未被CSI-2控制器分组的连续流。

MIPI Lane Deskew

MIPI Lane Deskew

当比特传输速率为1.5Gbps/通道及以上时,CSI-2 D-PHY接口通过从发射机发送去偏移模式来支持线间去偏移。对于低于1.5Gbps/通道的数据速率,可以选择Deskew。

MAX96714/F/R同时支持初始和周期性去偏斜。有关更多信息,请参阅MIPI_TX52。用户可以编程去偏移模式的长度和周期性去偏移输出的频率。启用时会自动生成定期去偏移。周期性去偏移的出现可以在“帧开始”或“帧结束”之后。

它可以在每帧开始,也可以在寄存器MIPI_TX4[5:3]指定的帧数之后开始。在隧道模式中,添加了额外的去扭曲功能,以便解串器的Tx去扭曲生成可以跟踪

CFG Latch at Power-Up Pins

加电引脚处的CFG闩锁

在上电或复位后,对CFG0和CFG1引脚处的电压进行采样。采样电平用于设置某些寄存器的初始值.每个引脚的电压电平由连接在VDDIO和地之间的外部精密电阻器分压器设置(图36),或者对于某些配置,由连接到VDDIO或地的单个电阻器设置。表8和表9显示了选择每种配置的推荐电阻值。CFG引脚处的电压电平通常在所有MAX96714/MAX96714F/MAX96714R电源达到上电复位(POR)电路所需的最小电平之后11ms被锁存。通电时,CFG引脚的负载不得超过10pF,以确保电压电平正确。

GMSL1 Backwards Compatibility GMSL1向后兼容性

MAX96714/F/R设计用于与任何GMSL1串行器配对。但是,不支持某些GMSL1序列化程序功能。GMSL1向后兼容性仅支持500Mbps到3.12Gbps的前向链路速率和1Mbps的反向链路速率。当MAX96714/F/R与传统的仅限GMSL1的串行器配对时,必须将其配置为GMSL1兼容模式,并且降低可用的前向链路速率以符合指定的GMSL1串行器的限制。

表10规定了在GMSL1模式下运行的GMSL2设备中通用GMSL2功能的可用性。MAX96714/F/R可能不支持表10中的所有GMSL1功能。一些GMSL2功能仅在GMSL2模式中可用,因此在GMSL1模式中不可用。禁用链接中两个设备都不支持的功能。

表10中规定的大多数功能可以通过适当的寄存器配置启用/禁用。序列化器和反序列化器子系统负责实现实现所需设置所需的配置引脚连接。有关如何连接到GMSL1串行器的更多信息,请参阅《GMSL2用户指南-与GMSL1序列化器配对》一节。

Power-Up and Link Startup

通电和链路启动

当PWDNB引脚为低电平或任何电源关闭时,GMSL2 IC处于断电模式。寄存器和配置设置为默认重置条件。

串行器和解串器可以按任何顺序通电。在PWDNB释放且所有电源接通后,每个设备开始其通电顺序,并按顺序执行以下操作:

1.根据所选配置设置内部寄存器(由CFG0、CFG1选择)。

2.开机自检从MBIST开始,然后是LBIST。POST完成后,将更新寄存器REG_POST0。POST后芯片复位(仅适用于MAX96714/F)。

3.本地侧的设备寄存器可通过I2C或UART写入和读取。

4.GMSL2 PHY执行链路校准、均衡器自适应和数据信道锁定。两个芯片都将LOCK引脚设置为高电平。

5.远程侧的设备寄存器可通过GMSL通道写入和读取。

Device Reset and Power Down

设备重置和断电

通过寄存器写入,有三种通用重置选项可用:

1.RESET_ALL重置所有块,包括所有寄存器、数字块和模拟块。该过程类似于将PWDNB引脚驱动为低电平然后驱动为高电平。它将所有控制寄存器重置为默认值。

2.设置RESET_LINK重置所有与GMSL PHY相关的数字逻辑和所有数据管道。在该位被设置之后,所有控制寄存器仍然可以通过本地反向通道访问,并且它们的值被保留。链路和数据管道保持在RESET状态,直到RESET_link被清除。

3.RESET_ONESHOT重置所有与GMSL PHY相关的数字逻辑和所有数据管道,然后自动清除自身。这类似于设置和清除RESET_LINK。

首先对影响GMSL2链路操作的寄存器(即RX_RATE、CXTP、GMSL2)进行编程,然后

RESET_ONESHOT,或者当RESET_LINK=1时设置这些寄存器,然后设置RESET_LINK=0。

断言PWDNB引脚(低电平有效)将设备置于断电模式,并将寄存器和设备配置重置为其通电默认值。任何低于其内部阈值设置的电源也会使设备处于断电模式。

Link and Video Lock

链接和视频锁定

图37显示了用于表征GMSL2链路锁定时间的序列。设备A是第一个通电或从RESET_LINK状态恢复操作的设备(串行器或解串器)。设备B是位于GMSL链路另一端的设备(解串器或串行器)。

链接锁定表示数据接收路径已锁定(解串器中的正向通道、串行器中的反向通道)。视频和控制信道功能(I2C、GPIO)可以在链路锁定被断言后立即使用。

该设备将在通电后自动建立单链路GMSL2连接和链路锁定。这表明电缆已插入,系统已启动并运行。μC和GMSL器件之间没有相互作用,实现了锁定。串行器和反串行器都有一个开漏LOCK输出引脚和一个相关的状态寄存器。

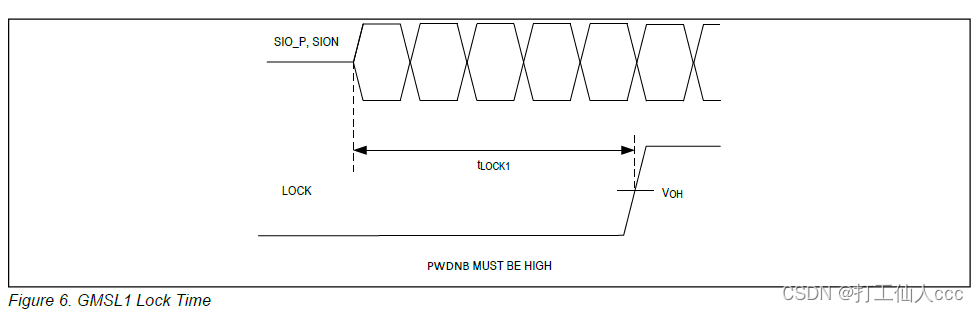

GMSL2链路使用晶体作为GMSL2链接的参考时钟,因此不需要有效的视频输入(PCLK)来锁定GMSL2连接。

笔记:

1.通过释放串行器或解串器中的PWDNB引脚或RESET_LINK位来启动锁定序列。

2.锁定时间是从串行器或解串器中的PWDNB或RESET_LINK释放中较晚的一个到被断言的Lock测量的。

3.在锁定过程开始之前,当两个设备都处于PWDNB/RESET_LINK模式时,链路两侧的PWDNB/RESET_LINK状态必须重叠。

4.如果RESET_LINK用于启动锁定,则假定PWDNB在通电(正常操作)后为高电平。

5.如果PWDNB用于启动锁定,则假设RESET_LINK在通电(正常操作)后为低电平。

6.为了达到规定的锁定时间,时间延迟tRD(两个设备上PWDNB/RESET_LINK释放之间的延迟)必须小于电气特性部分注释9中规定的阈值。如果不能保证这一时间,请联系工厂寻求指导。

7.锁定时间和最大允许tRD在不同系列的GMSL设备之间变化。它们取决于序列化程序和反序列化程序的特性。特定链路的典型锁定时间可以最好地估计为每个设备数据表中指定的锁定时间中较长的一个。类似地,特定链路的最大允许tRD可以估计为每个设备数据表中指定的值中的较小值。如需进一步指导,请联系工厂。

8.如果链路锁定出现瞬时中断,应在失去锁定后提供100ms的时间,以使链路能够在发出任何ECU启动的重置之前自动恢复。这将最大限度地减少由连接的瞬时丢失引起的任何中断。

Video Lock

视频锁定

视频锁定指示解串器正在接收有效的视频数据。在GMSL2链路被锁定之后,解串器视频输出PLL开始其锁定序列。解串器通常在断言行锁定几毫秒后开始输出视频数据,前提是它正在从串行器接收视频分组。视频锁定状态通常从寄存器中读取。

Error and Fault Condition Monitoring

错误和故障状态监测

MAX96714/F/R具有漏极开路、多功能错误报告和中断状态输出。活动的低ERRB引脚由各种错误和事件状态指示器的逻辑OR驱动。每个错误条件驱动ERRB的能力可通过寄存器设置屏蔽。可以驱动ERRB的每个错误和事件在寄存器的子块中都有一个状态标志。因此,断言ERRB的原因可以通过读取寄存器状态来确定。可以通过链路从串行器自动转发错误,使得某些串行器错误,例如CSI-2输入CRC错误,可以由MAX96714/F/R的ERRB输出自动标记。

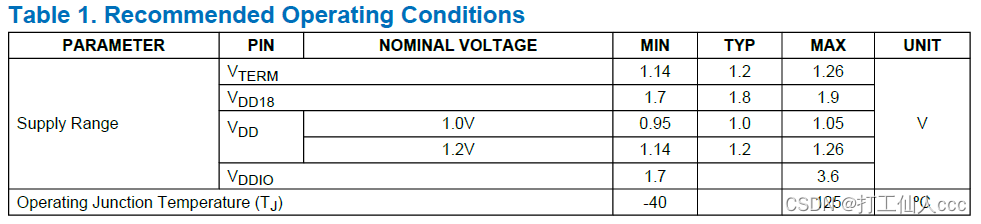

Power Supplies Information, and Overvoltage and Undervoltage

电源信息以及过电压和欠电压

没有启动设备电源所需的顺序。片上电源管理块在通电期间管理电源域。

MAX96714/F/R提供了灵活的电源配置。

1V核心电源可以直接提供,也可以通过内部低压差(LDO)调节器提供。为了最大限度地减少功耗,请将1.0V±5%连接到VDD。如果VDD<1.1V且CAP_VDD<1.05V,则在通电时自动禁用调节器,并且低电阻开关将VDD连接到内部电源导轨。对于内部调节器,将1.2V±5%连接到VDD。通电后,写入REG_ENABLE=1,然后写入REG_MNL=1,作为设备初始化的一部分,以启用内部LDO。

GPIO引脚的VDDIO电源可以是1.8V到3.3V,以灵活容纳与部件接口的设备。

允许的电源电压范围为1.7V(1.8V-5%)至3.6V(3.3V+9%)。VDD18是主要模拟电源。连接1.8V±5%。VTERM是D-PHY终端电源。连接1.2V±5%。

电源斜坡时间建议:20μs<斜坡时间<2ms。电源斜坡应是单调的。

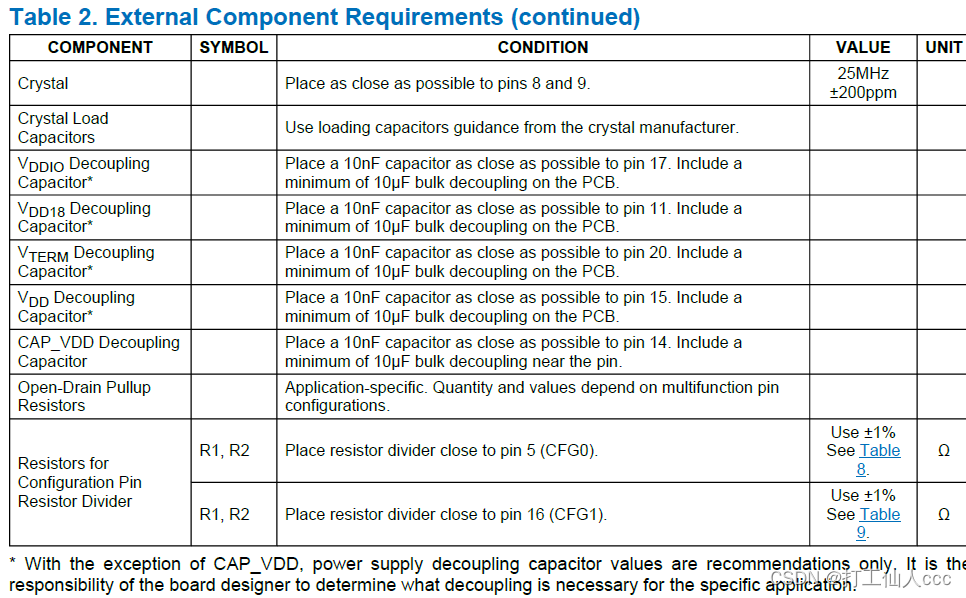

一旦电源电压达到最小电源电压限制,就不应允许其降至技术规格以下。所有电源的适当电源旁路对高频电路的稳定性至关重要。见表2。见表1

电源容差和噪声要求。请联系工厂,以获得有关共享供应和优化供应解耦的指导。

MAX96714/F/R提供了广泛的电源诊断功能。还为除VDDIO之外的所有电源电压提供过电压检测。关于欠压事件,请参阅PWR0寄存器以获取信息。过电压(请参阅INTR10和PM_OV_STAT2/4启用)和欠电压可通过CMP_STATUS和VDDBAD进行监测。

除了专用的内部中断标志外,还可以通过ERRB引脚报告OV/UV情况。在过电压情况下,电源管理器不采取进一步行动,设备继续正常运行,尽管根据过电压事件的持续时间和大小,设备可能会受到损坏。

当依靠ERRB引脚来传达欠压事件的发生时,在ERRB引脚和接地之间连接一个外部1MΩ电阻器,因为ERRB不是通电默认MFP功能。因此,在由欠压事件触发的重置之后,ERRB MFP引脚恢复为高阻抗,而不是ERRB。在错误状态期间,主机设备期望ERRB驱动逻辑低,并且上述电阻器的存在使得在复位之后能够保持适当的逻辑电平,从而提醒主机设备需要注意。

4441

4441

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?